17

LTC1292/LTC1297

12927fb

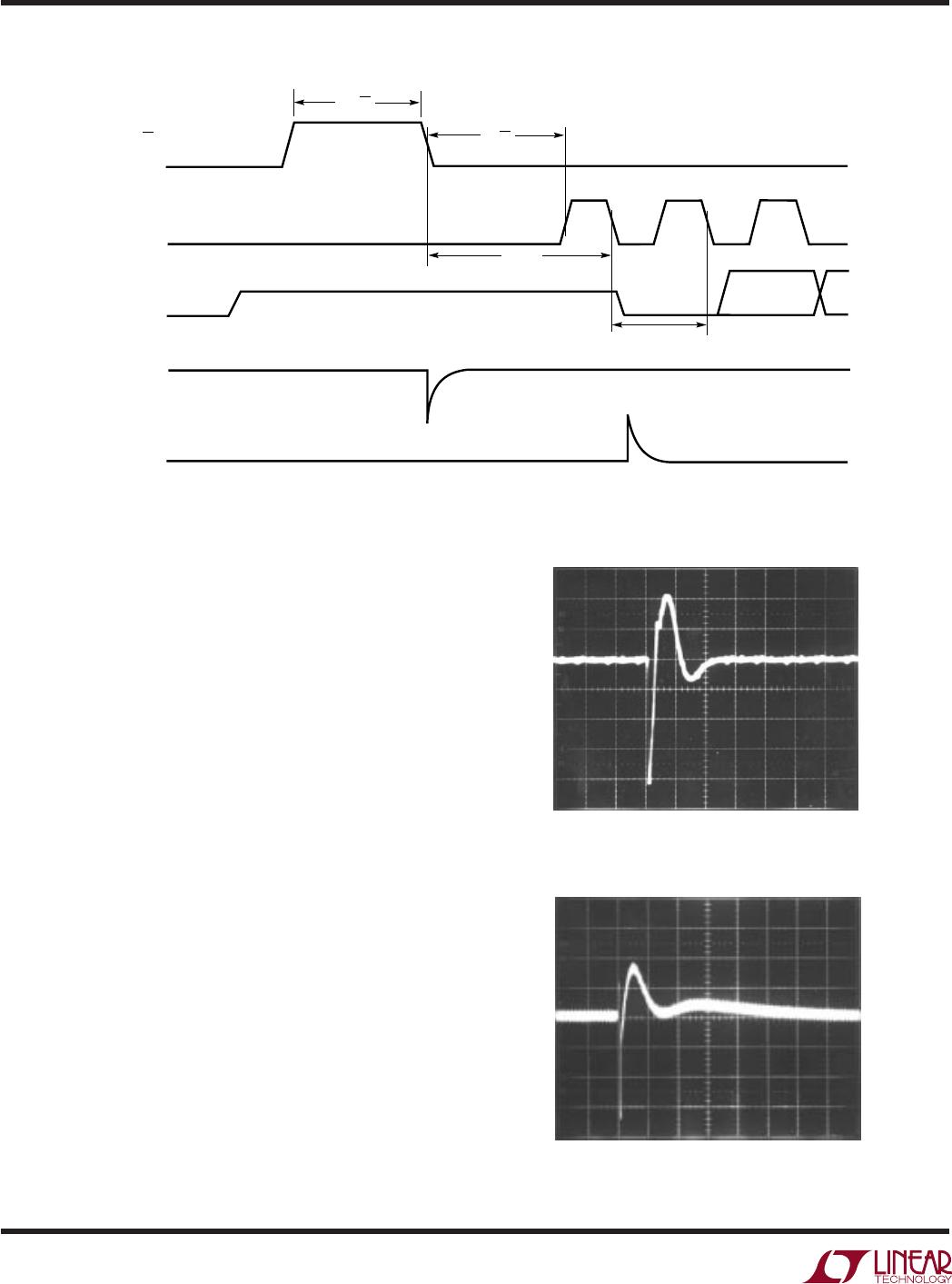

RC Input Filtering

It is possible to filter the inputs with an RC network as

shown in Figure 15. For large values of C

F

(e.g., 1µF) the

capacitive input switching currents are averaged into a net

DC current. A filter should be chosen with a small resistor

and large capacitor to prevent DC drops across the resistor.

The magnitude of the DC current is approximately I

DC

=

100pF × V

IN

/t

CYC

and is roughly proportional to V

IN

. When

running the LTC1292(LTC1297) at the minimum cycle

time of 16.5µs (20µs), the input current equals 30µA

(25µA) at V

IN

= 5V. Here a filter resistor of 4Ω (5Ω) will

cause 0.1LSB of full scale error. If a large filter resistor

must be used, errors can be reduced by increasing the

cycle time as shown in the typical performance

characteristics curve Maximum Filter Resistor vs Cycle

Time.

Figure 15. RC Input Filtering

curve of S&H Acquisition Time vs Source Resistance). The

input voltage is sampled during the t

SMPL

time as shown

in Figure 11. The sampling interval begins at the rising

edge of CS for the LTC1292, and at the falling edge of CS

for the LTC1297, and continues until the falling edge of the

CLK before the conversion begins. On this falling edge the

S&H goes into the hold mode and the conversion begins.

Differential Input

With a differential input the A/D no longer converts a single

voltage but converts the difference between two voltages.

The voltage on the +IN pin is sampled and held and can be

rapidly time-varying as in single-ended mode. The voltage

on the –IN pin must remain constant and be free of noise

and ripple throughout the conversion time. Otherwise the

differencing operation will not be done accurately. The

conversion time is 12 CLK cycles. Therefore a change in

the –IN input voltage during this interval can cause

conversion errors. For a sinusoidal voltage on the –IN

input this error would be:

VfV

f

ERROR MAX IN PEAK

CLK

( ) (– )

=

()

2

12

π

Where f

(–IN)

is the frequency of the –IN input voltage,

V

PEAK

is its peak amplitude and f

CLK

is the frequency of the

CLK. Usually V

ERROR

will not be significant. For a 60Hz

signal on the –IN input to generate a 0.25LSB error

(300µV) with the converter running at CLK = 1MHz, its

peak value would have to be 66mV. Rearranging the above

equation the maximum sinusoidal signal that can be

digitized to a given accuracy is given as:

f

V

V

f

IN MAX

ERROR MAX

PEAK

CLK

(– )

()

=

π

2

12

For 0.25LSB error (300µV) the maximum input sinusoid

with a 5V peak amplitude that can be digitized is 0.8Hz.

Reference Input

The voltage on the reference input of the LTC1292/

LTC1297 determine the voltage span of the A/D con-

verter. The reference input has transient capacitive

Input Leakage Current

Input leakage currents also can create errors if the source

resistance gets too large. For example, the maximum input

leakage specification of 1µA flowing through a source

resistance of 1k will cause a voltage drop of 1mV or

0.8LSB. This error will be much reduced at lower

temperatures because leakage drops rapidly (see typical

performance characteristics curve Input Channel Leakage

Current vs Temperature).

SAMPLE-AND-HOLD

Single-Ended Input

The LTC1292/LTC1297 provide a built-in sample-and-

hold (S&H) function on the +IN input for signals acquired

in the single-ended mode (–IN pin grounded). The sample-

and-hold allows the LTC1292/LTC1297 to convert rapidly

varying signals (see typical performance characteristics

R

FILTER

C

FILTER

LTC1292/7 F15

LTC1292

LTC1297

“+”

“–”

I

DC

V

IN

U

S

A

O

PP

L

IC

AT

I

WU

U

I FOR ATIO