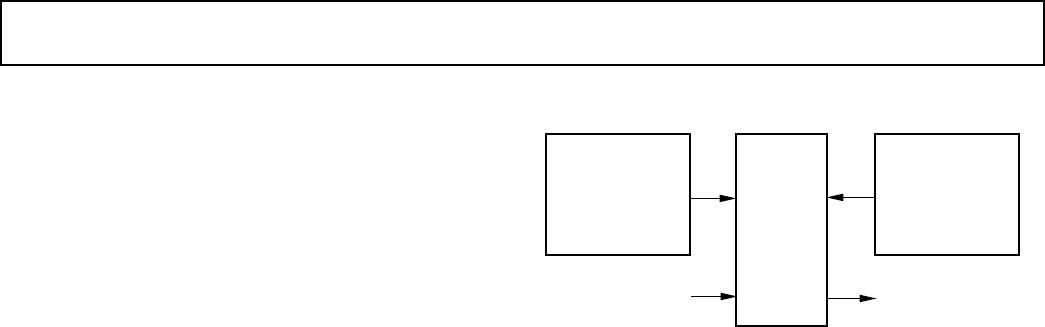

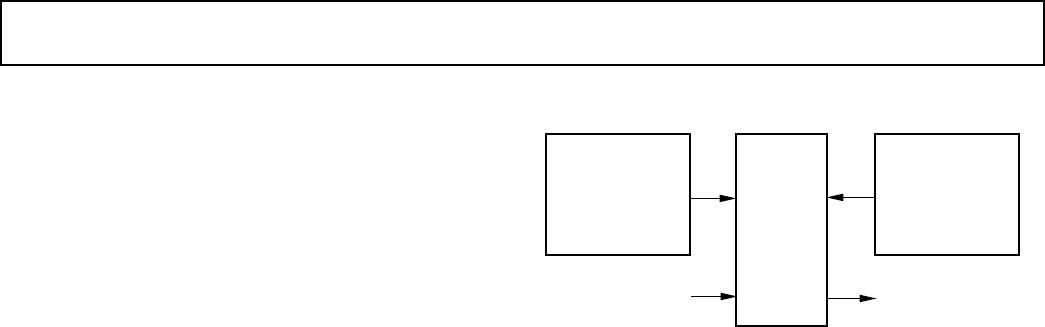

SYSTEM DIAGRAM

AD1893

EXAMPLE

FREQUENCIES:

DAT 48kHz OR

CD 44.1kHz OR

BROADCAST 32kHz

EXAMPLE

FREQUENCIES:

DAT 48kHz OR

CD 44.1kHz OR

BROADCAST 32kHz

INPUT SERIAL DATA

OUTPUT SERIAL DATA

INPUT SAMPLE CLOCK

OUTPUT SAMPLE CLOCK

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

FEATURES

Low Cost

LQFP and PDIP Packages

3 V Supply Performance Specified—Very Low Power

Automatically Senses Sample Frequencies—No

Programming Required

Rejects Sample Clock Jitter

Accommodates Dynamically Changing Asynchronous

Sample Clocks

8 kHz to 56 kHz Sample Clock Frequency Range

Approximately 1:2 to 2:1 Ratio Between Sample

Clocks

–96 dB THD+N at 1 kHz

96 dB Dynamic Range

Optimal Clock Tracking Control—Slow/Fast Settling

Modes

Linear Phase in All Modes

Automatic Output Mute

Flexible Four-Wire Serial Interfaces with Right-Justified

Mode

Power-Down Mode

On-Chip Oscillator

APPLICATIONS

Consumer CD-R, DAT, DCC, MD and 8 mm Video Tape

Recorders Including Portables

Digital Audio Communication/Network Systems

Computer Multimedia Systems

PRODUCT OVERVIEW

The AD1893 SamplePort is a fully digital, stereo Asynchronous

Sample Rate Converter (ASRC) that solves sample rate interfacing

and compatibility problems in digital audio equipment. Concep-

tually, this converter interpolates the input data up to a very high

internal sample rate with a time resolution of 300 ps, then deci-

mates down to the desired output sample rate. The AD1893 is

intended for 16-bit low cost, non-varispeed applications where low

voltage, low power (i.e., battery-powered) operation is required.

Refer to the AD1890/AD1891 data sheet for other products in the

SamplePort family. This device is asynchronous because the fre-

quency and phase relationships between the input and output

sample clocks (both are inputs to the AD1893 ASRC) are arbitrary

and need not be related by a simple integer ratio. There is no need

to explicitly select or program the input and output sample clock

frequencies, as the AD1893 automatically senses the relationship

between the two clocks. The input and output sample clock fre-

quencies can nominally range from 8 kHz to 56 kHz, and the ratio

between them can vary from approximately 1:2 to 2:1.

SamplePort is a registered trademark of Analog Devices, Inc.

AD1893

Low Cost SamplePort

®

16-Bit Stereo Asynchronous

Sample Rate Converter

The AD1893 uses multirate digital signal processing techniques

to construct an output sample stream from the input sample

stream. The input word width is 4 to 16 bits for the AD1893.

Shorter input words are automatically zero-filled in the LSBs.

The output word width is 24 bits. The user can receive as many

of the output bits as desired. Internal arithmetic is performed

with 22-bit coefficients and 27-bit accumulation. The digital

samples are processed with unity gain.

The input and output control signals allow for considerable

flexibility for interfacing to a variety of DSP chips, AES/EBU

receivers and transmitters and for I

2

S compatible devices. Input

and output data can be independently right- or left- (with or

without a one bit clock delay) justified to the left/right clock

edge. In the right-justified mode, the MSB is delayed 16-bit

clock periods from the left/right clock edge transition. Input and

output data can also be independently justified to the word

clock rising edge. The data justification options are encoded on

two mode pins for both the input port and the output port. The

bit clocks can also be independently configured for rising edge

active or falling edge active operation.

The AD1893 SamplePort ASRC has on-chip digital coefficients

that correspond to a highly oversampled 0 Hz to 20 kHz low-

pass filter with a flat passband, a very narrow transition band,

and a high degree of stopband attenuation. A subset of these

filter coefficients are dynamically chosen on the basis of the

filtered ratio between the input sample clock (LR_I) and the

output sample clock (LR_O), and these coefficients are then

used in an FIR convolver to perform the sample rate conversion.

Refer to the Theory of Operation section of this data sheet for a

more thorough functional description. The low-pass filter has

been designed so that full 20 kHz bandwidth is maintained

when the input and output sample clock frequencies are as low

as 44.1 kHz. If the output sample rate drops below the input

sample rate, the bandwidth of the input signal is automatically

(continued on Page 4)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1998