AD1893

REV. A

–13–

OPERATING FEATURES

Serial Input/Output Ports

The AD1893 uses the frequency of the left/right input clock

(LR_ I) and the left/right output clock (LR_O) signals to deter-

mine the sample rate ratio, and therefore these signals must run

continuously and transition twice per sample period. (The LR_I

clock frequency is equivalent to F

SIN

and the LR_O clock fre-

quency is equivalent to F

SOUT

.) The other clocks (WCLK_I,

WCLK_O, BCLK_I, BCLK_O) are edge sensitive and may be

used in a gated or burst mode (i.e., a stream of pulses during

data transmission or reception followed by periods of inactivity).

The word clocks and the output bit clock are used only to write

data into or read data out of the serial ports; only the left/right

clocks are used in the internal DSP blocks. The input bit clock

is used to sample the input left/right clock. It is important that

the left/right clocks are “clean” with monotonic rising and falling

edge transitions and no excessive overshoot or undershoot which

could cause false triggering on the AD1893.

The AD1893’s flexible serial input and output ports consume

and produce data in twos-complement, MSB-first format. The

left channel data field always precedes the right channel data

field; the current channel being consumed or produced is indi-

cated by the state of the left/right clock (LR_I and LR_O). A left

channel field, right channel field pair is called a frame. The

input data field consists of 4 to 16 bits. The output data field

consists of 4 to 24 bits. The input signals are specified to TTL

logic levels, and the outputs swing to full CMOS logic levels.

The ports are configured by pin selections.

Serial I/O Port Modes

The AD1893 has pin-selectable bit clock polarity for the input

and output ports. In “normal” mode (BKPOL_I or BKPOL_O

LO) the data is valid on the rising edge. In the “inverted” mode

(BKPOL_I or BKPOL_O HI) the data is valid on the falling

edge. Both modes are shown in Figures 23 and 24.

The AD1893 uses two multiplexed input pins to control the mode

configuration of the input and output serial ports. MODE0_I

and MODE1_I control the input serial port, and MODE0_O

and MODE1_O control the output serial port as follows:

MODE0_I MODE1_I Serial Input Port Mode

0 0 Left-justified, no MSB delay, LR_I clock

triggered.

0 1 Left-justified, MSB delay, LR_I clock

triggered.

1 0 Right-justified, MSB delayed 16-bit clock

periods from LR_I clock transition, LR_I

clock triggered.

1 1 Word clock triggered, no MSB delay.

MODE0_O MODE1_O Serial Output Port Mode

0 0 Left-justified, no MSB delay, LR_O clock

triggered.

0 1 Left-justified, MSB delay, LR_O clock

triggered.

1 0 Right-justified, MSB delayed 16-bit clock

periods from LR_O clock transition, LR_O

clock triggered.

1 1 Word clock triggered, no MSB delay.

The MSB delay is useful for I

2

S format compatibility and for

ease of interfacing to some DSP processors.

The AD1893 SamplePort serial ports operate in either the word

clock (WCLK_I, WCLK_O) triggered mode or left/right clock

(LR_I, LR_O) triggered mode. These modes can be utilized

independently for the input and output ports. In the word clock

triggered mode, as shown in Figure 23, after the left/right clock

is valid, the appearance of the MSB of data is synchronous with

the rising edge of the word clock. Note that the word clock is

rising edge sensitive, and can fall anytime after it is sampled HI

by the bit clock. In the left-justified left/right clock triggered

modes, as shown in Figure 24, the appearance of the MSB of

data is synchronous with the rising edge of the left/right clock

for the left channel and the falling edge of left/right clock for the

right channel. The MSB is delayed by one bit clock after the

left/right clock if the MSB delay mode is selected. In the right-

justified left/right clock triggered mode, as shown in Figure 25,

the MSB is delayed 16 bit clock periods from a left/right clock

edge, so that when there are 64 bit clock periods per frame, the

LSB is right-justified to a left/right clock edge. The word clock

is not required in the left/right clock triggered modes, and

should be tied either HI or LO. Figure 24 shows the bit clock in

the optional gated or burst mode; the bit clock is inactive be-

tween data fields, and can take either the HI state or the LO

state while inactive.

Note that there is no requirement for a delay between the left

channel data and the right channel data. The left/right clocks

and the word clocks can transition immediately after the LSB of

the data, so that the MSB of the subsequent channel appears

without any timing delay. The AD1893 is therefore capable of a

32-bit frame mode, in which both 16-bit channels are packed

into a 32-bit clock period. More generally, there is no particular

requirement for when the left/right clock falls (i.e., there is no

left/right clock duty cycle or pulsewidth specification), provided

that the left/right clock frequency equals the intended sample

frequency, and there are sufficient bit clock periods to clock in

or out the intended number of data bits.

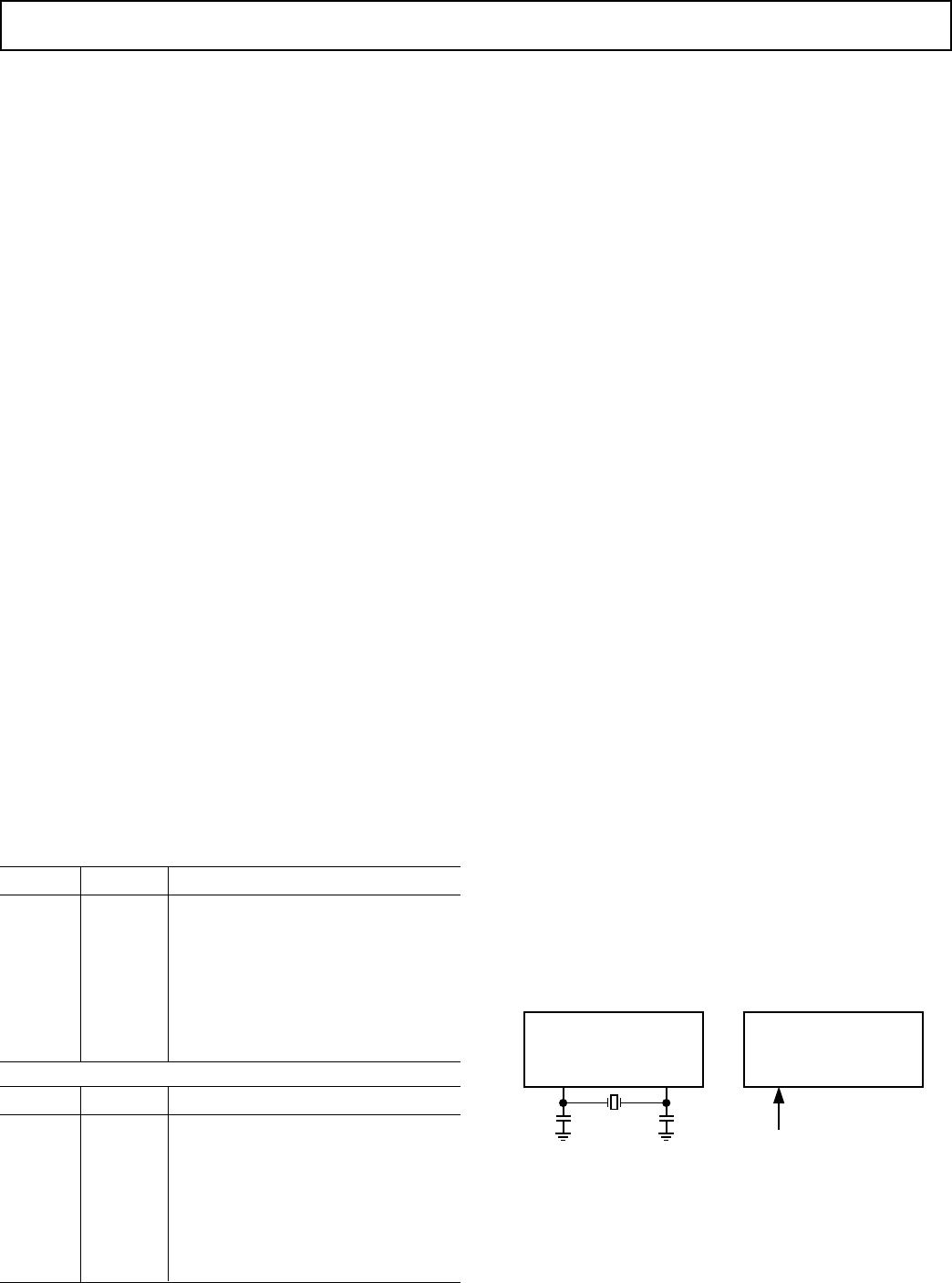

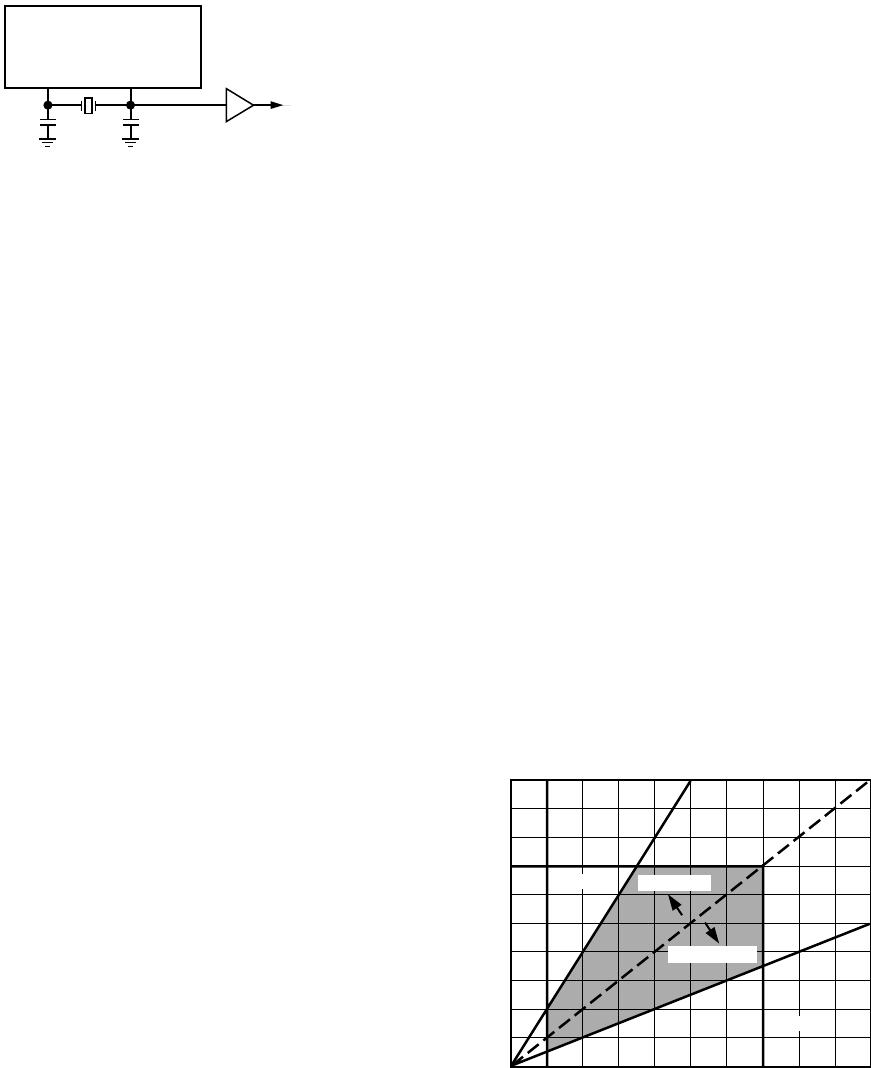

On-Chip Oscillator

The AD1893 includes an on-chip oscillator so that the user

need only supply an external quartz crystal or ceramic resonator.

The crystal or the resonator should be tied to the XTAL_I and

XTAL_O pins of the AD1893. An external crystal oscillator can

be used to overdrive the AD1893 on-chip oscillator. The exter-

nal clock source should be applied to the XTAL_I pin, and the

XTAL_O pin should be left unconnected.

AD1893

XTAL_I XTAL_O

AD1893

XTAL_I XTAL_O

NC

16MHz CRYSTAL CONNECTION 16MHz OSCILLATOR CONNECTION

16MHz

16MHz

20–64pF 20–64pF

Figure 9. Crystal and Oscillator Connections