MAX1240/MAX1241

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

8 _______________________________________________________________________________________

_______________Detailed Description

Converter Operation

The MAX1240/MAX1241 use an input track/hold (T/H)

and successive-approximation register (SAR) circuitry

to convert an analog input signal to a digital 12-bit out-

put. No external-hold capacitor is needed for the T/H.

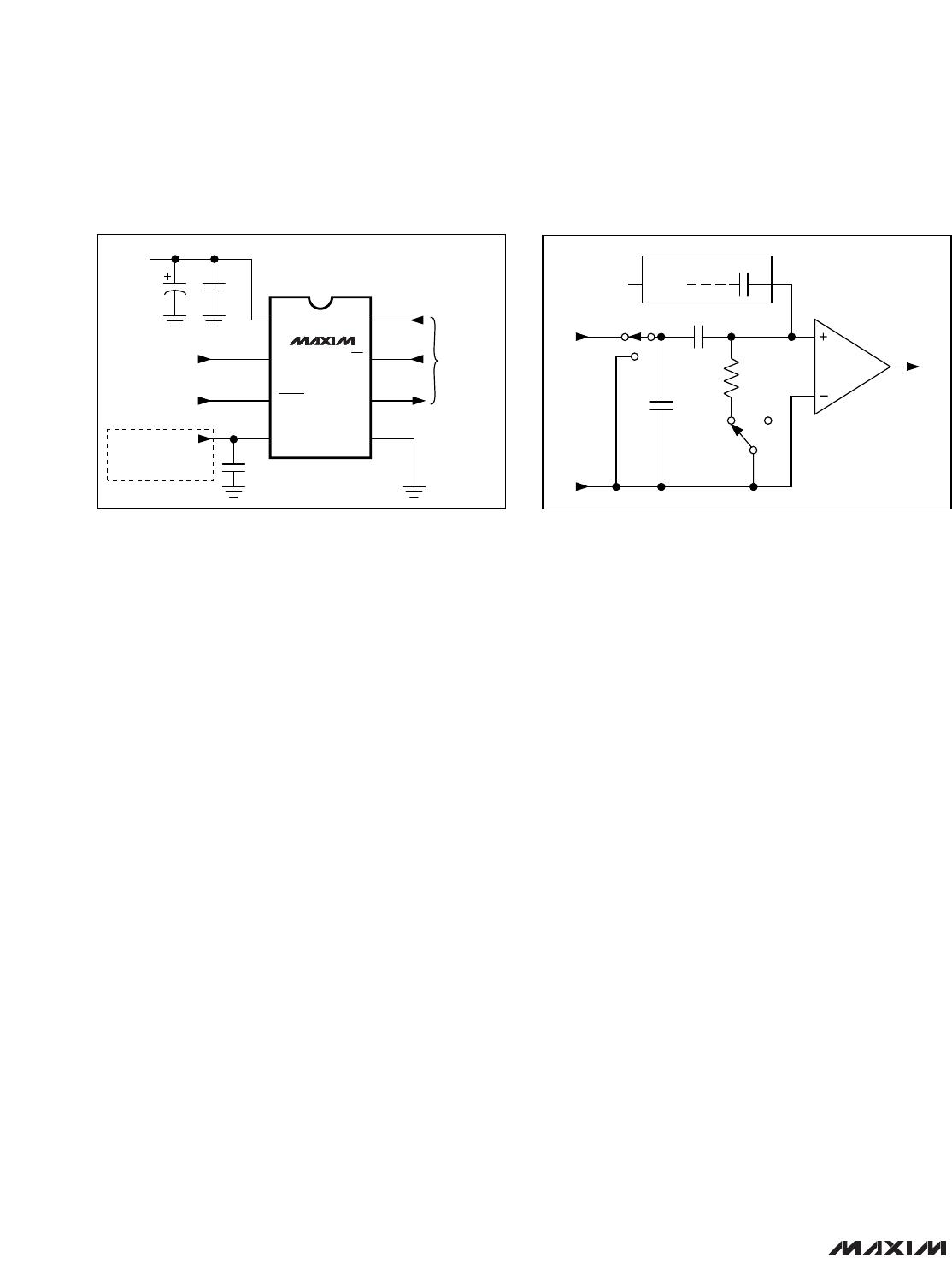

Figure 3 shows the MAX1240/MAX1241 in its simplest

configuration. The MAX1240/MAX1241 convert input

signals in the 0V to V

REF

range in 9µs, including T/H

acquisition time. The MAX1240’s internal reference is

trimmed to 2.5V, while the MAX1241 requires an external

reference. Both devices accept voltages from 1.0V to

V

DD

. The serial interface requires only three digital lines

(SCLK,

CS,

and DOUT) and provides an easy interface

to microprocessors (µPs).

The MAX1240/MAX1241 have two modes: normal and

shutdown. Pulling

SHDN

low shuts the device down and

reduces supply current below 10µA (V

DD

≤ 3.6V

), while

pulling

SHDN

high or leaving it open puts the device

into operational mode. Pulling CS low initiates a conver-

sion. The conversion result is available at DOUT in

unipolar serial format. The serial data stream consists

of a high bit, signaling the end of conversion (EOC), fol-

lowed by the data bits (MSB first).

Analog Input

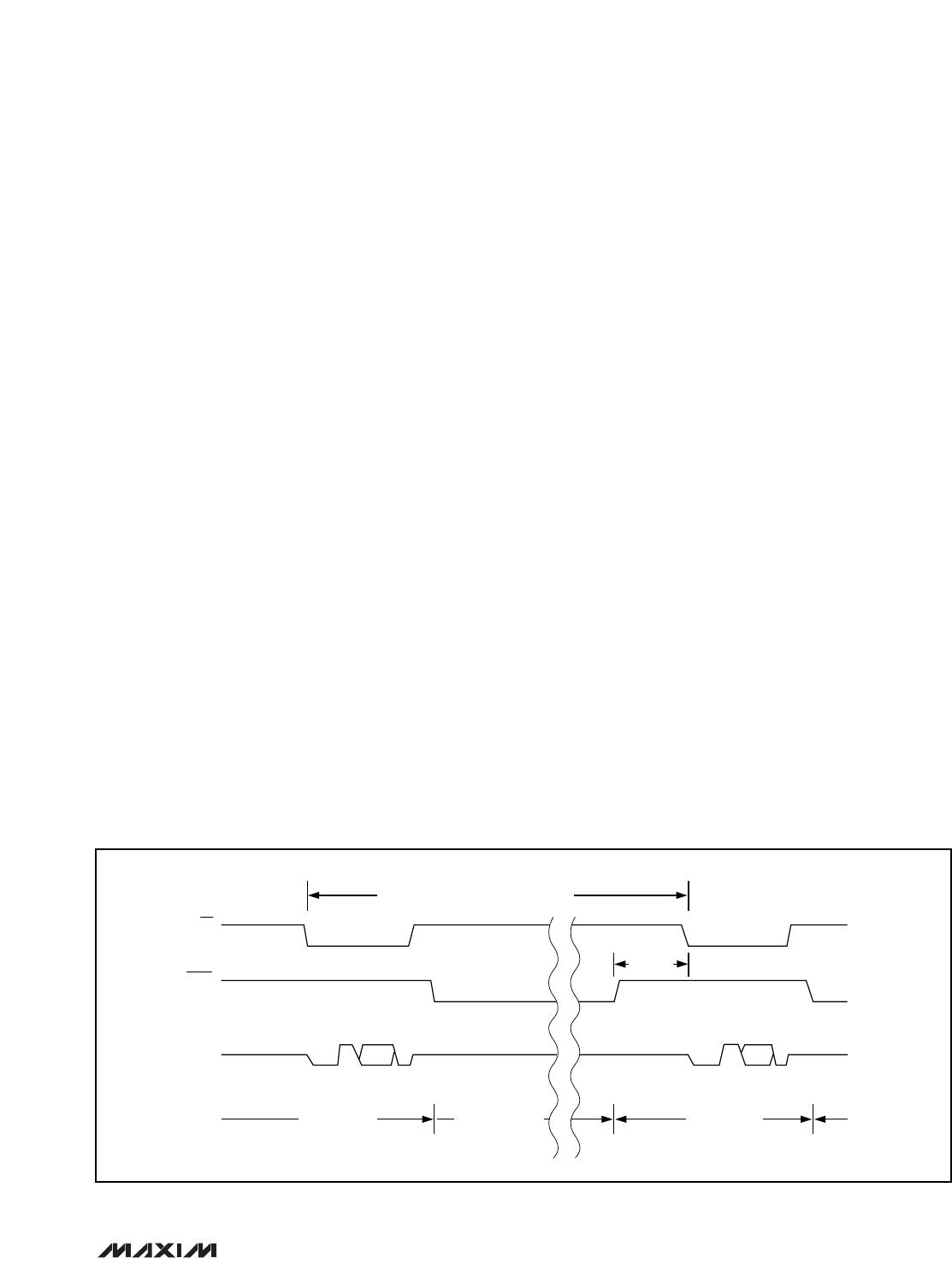

Figure 4 illustrates the sampling architecture of the ana-

log-to-digital converter’s (ADC’s) comparator. The full-

scale input voltage is set by the voltage at REF.

Track/Hold

In track mode, the analog signal is acquired and stored

in the internal hold capacitor. In hold mode, the T/H

switch opens and maintains a constant input to the

ADC’s SAR section.

During acquisition, the analog input (AIN) charges

capacitor C

HOLD

. Bringing

CS

low ends the acquisition

interval. At this instant, the T/H switches the input side

of C

HOLD

to GND. The retained charge on C

HOLD

repre-

sents a sample of the input, unbalancing node ZERO at

the comparator’s input.

In hold mode, the capacitive digital-to-analog converter

(DAC) adjusts during the remainder of the conversion

cycle to restore node ZERO to 0V within the limits of 12-

bit resolution. This action is equivalent to transferring a

charge from C

HOLD

to the binary-weighted capacitive

DAC, which in turn forms a digital representation of the

analog input signal. At the conversion’s end, the input

side of C

HOLD

switches back to AIN, and C

HOLD

charges to the input signal again.

The time required for the T/H to acquire an input signal

is a function of how quickly its input capacitance is

charged. If the input signal’s source impedance is high,

the acquisition time lengthens and more time must be

allowed between conversions. The acquisition time

(t

ACQ

) is the maximum time the device takes to acquire

the signal, and is also the minimum time needed for the

signal to be acquired. Acquisition time is calculated by:

t

ACQ

= 9(R

S

+ R

IN

) x 16pF

where R

IN

= 9kΩ, R

S

= the input signal’s source imped-

ance, and t

ACQ

is never less than 1.5µs. Source imped-

ances below 1kΩ do not significantly affect the ADC’s

AC performance.

Higher source impedances can be used if a 0.01µF

capacitor is connected to the analog input. Note that

the input capacitor forms an RC filter with the input

source impedance, limiting the ADC’s input signal

bandwidth.

AIN TO GND.