74HC161 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

Product data sheet Rev. 3 — 4 January 2017 4 of 20

NXP Semiconductors

74HC161

Presettable synchronous 4-bit binary counter; asynchronous reset

5. Pinning information

5.1 Pinning

5.2 Pin description

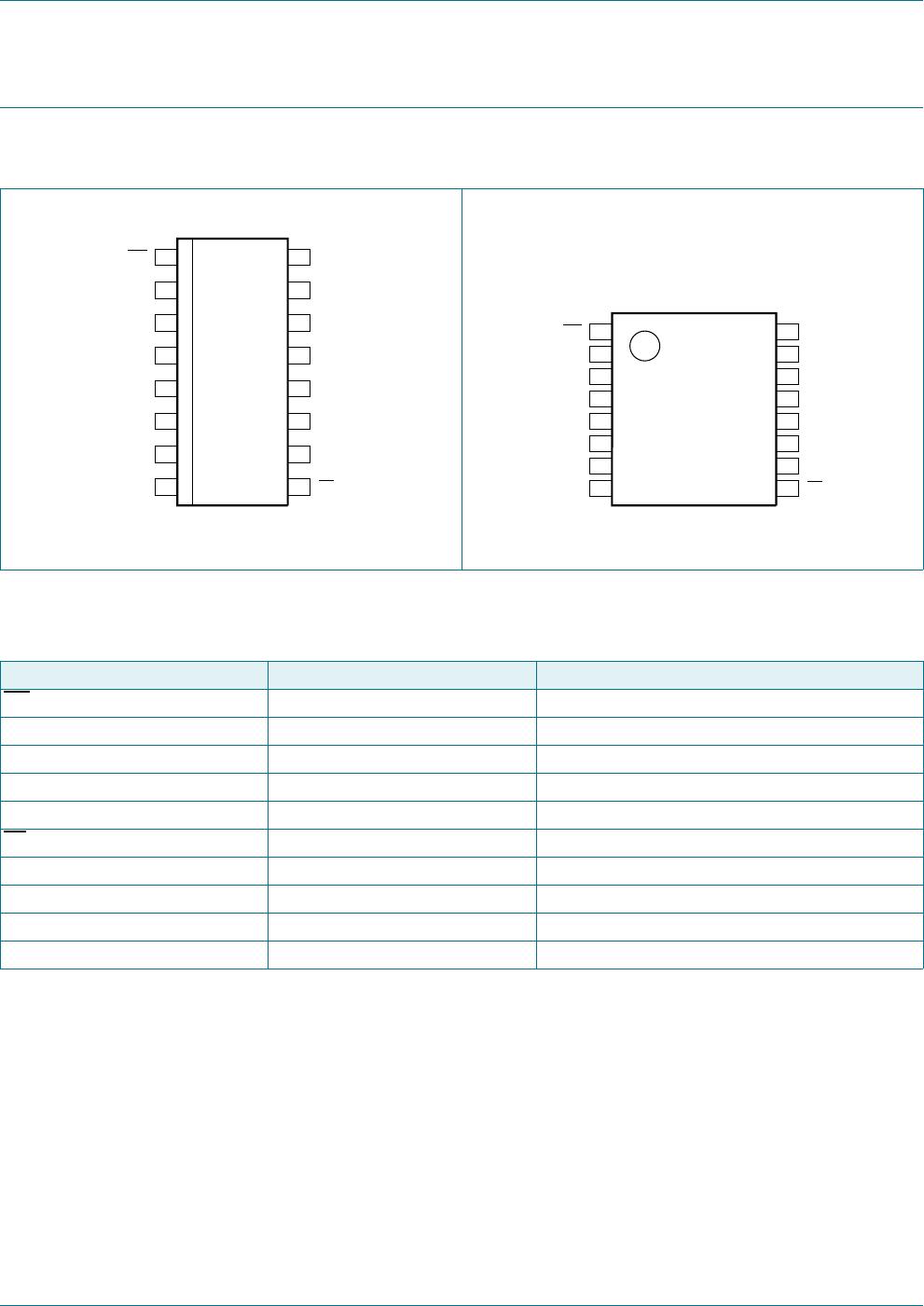

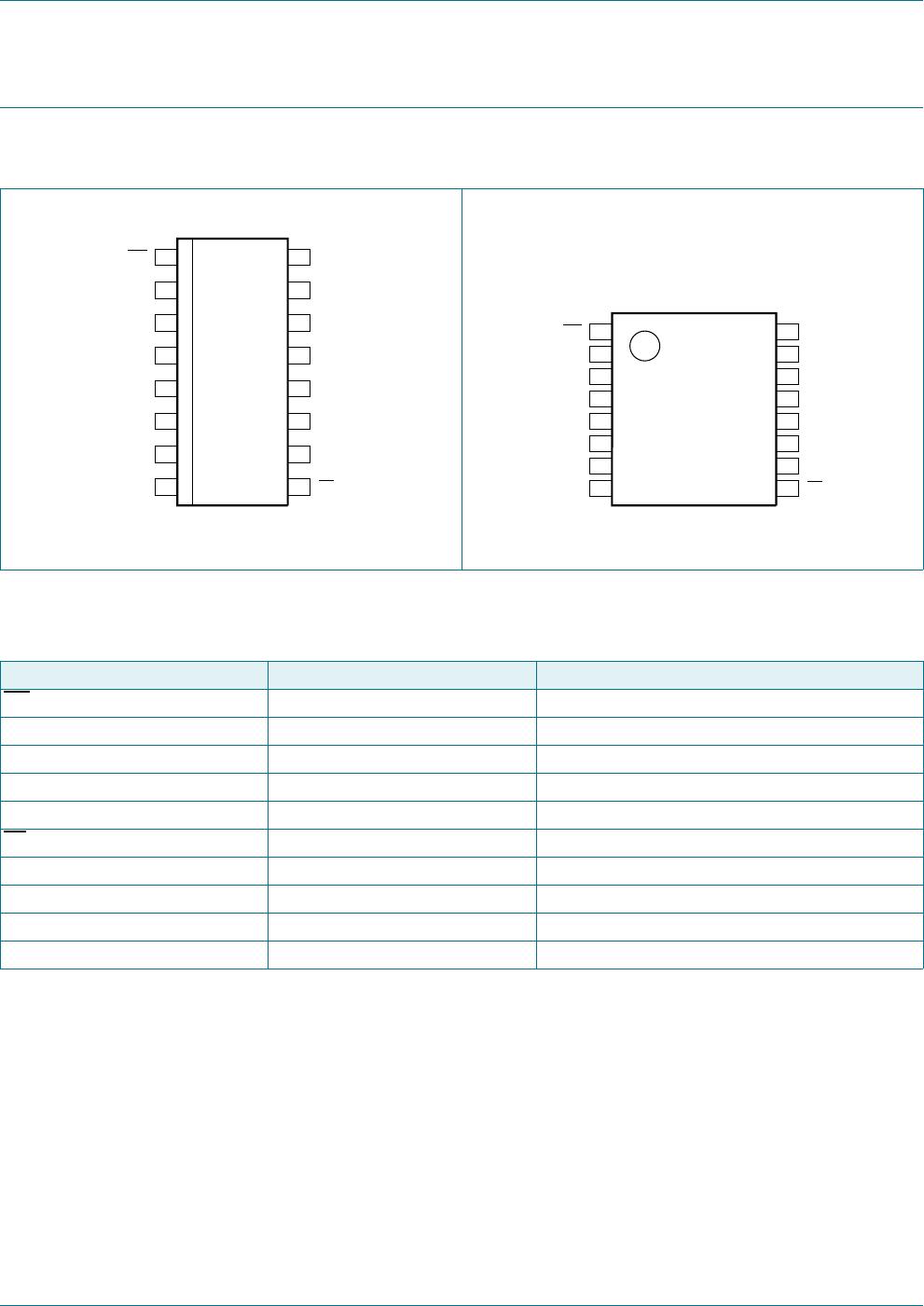

Fig 5. Pin configuration SO16 Fig 6. Pin configuration TSSOP16 and SSOP16

5

3

4

&(3 &(7

*1' 3(

DDD

5

3

4

&(3 &(7

*1' 3(

DDD

Table 2. Pin description

Symbol Pin Description

MR

1 asynchronous master reset (active LOW)

CP 2 clock input (LOW-to-HIGH, edge-triggered)

D0, D1, D2, D3 3, 4, 5, 6 data input

CEP 7 count enable input

GND 8 ground (0 V)

PE

9 parallel enable input (active LOW)

CET 10 count enable carry input

Q0, Q1, Q2, Q3 14, 13, 12, 11 flip-flop output

TC 15 terminal count output

V

CC

16 supply voltage