12 Integrated Silicon Solution, Inc. — www.issi.com

Rev. E

01/10/2013

IS61WV12816DALL/DALS, IS61WV12816DBLL/DBLS,

IS64WV12816DBLL/DBLS

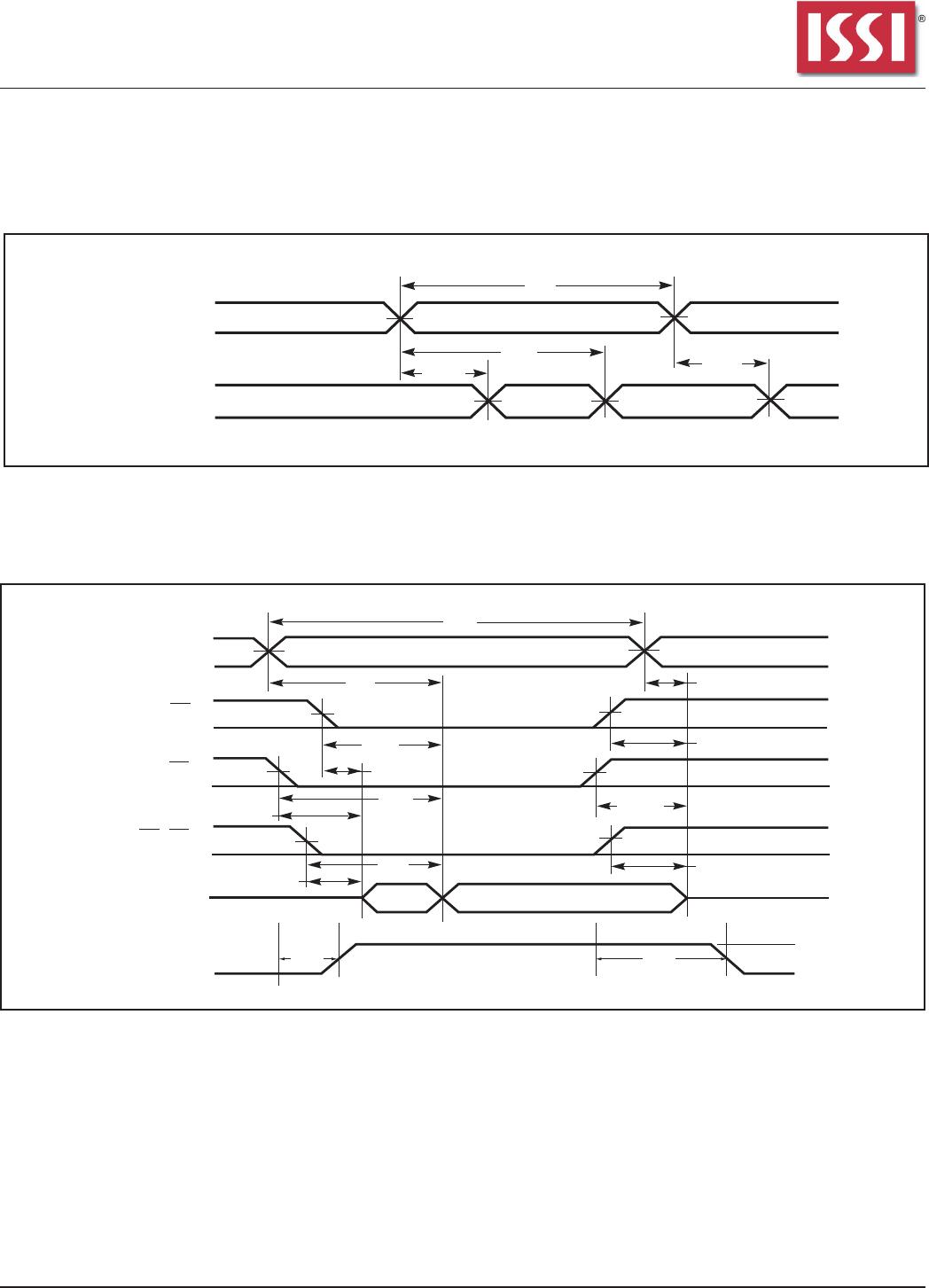

WRITE CYCLE SWITCHING CHARACTERISTICS

(1,3)

(Over Operating Range)

-8 -10 -12

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit

twc WriteCycleTime 8 — 10 — 12 — ns

tsce CEtoWriteEnd 6.5 — 8 — 9 — ns

tAw AddressSetupTime 6.5 — 8 — 9 — ns

to Write End

tHA Address Hold from Write End 0 — 0 — 0 — ns

tsA AddressSetupTime 0 — 0 — 0 — ns

tPwb LB, UBValidtoEndofWrite 6.5 — 8 — 9 — ns

tPwe1 WEPulseWidth 6.5 — 8 — 9 — ns

tPwe2 WE Pulse Width (OE = LOW) 8.0 — 10 — 11 — ns

tsd DataSetuptoWriteEnd 5 — 6 — 9 — ns

tHd Data Hold from Write End 0 — 0 — 0 — ns

tHzwe

(2)

WELOWtoHigh-ZOutput — 3.5 — 5 — 6 ns

tLzwe

(2)

WE HIGH to Low-Z Output 2 — 2 — 3 — ns

Notes:

1. Testconditionsassumesignaltransitiontimesof3nsorless,timingreferencelevelsof1.5V,inputpulselevelsof0Vto3.0V

andoutputloadingspeciedinFigure1.

2. TestedwiththeloadinFigure2.Transitionismeasured±500mVfromsteady-statevoltage.Not100%tested.

3. TheinternalwritetimeisdenedbytheoverlapofCE LOW and UB or LB, and WE LOW. All signals must be in valid states

toinitiateaWrite,butanyonecangoinactivetoterminatetheWrite.TheDataInputSetupandHoldtimingarereferencedto

the rising or falling edge of the signal that terminates the write. Shaded area product in development