XRA1202/1202P

6

8-BIT I2C/SMBUS GPIO EXPANDER WITH RESET

REV. 1.0.1

1.1.2 I

2

C Read and Write

A read or write transaction is determined by bit-0 of the slave address. If bit-0 is ’0’, then it is a write

transaction. If bit-0 is ’1’, then it is a read transaction.

1.1.3 I

2

C Command Byte

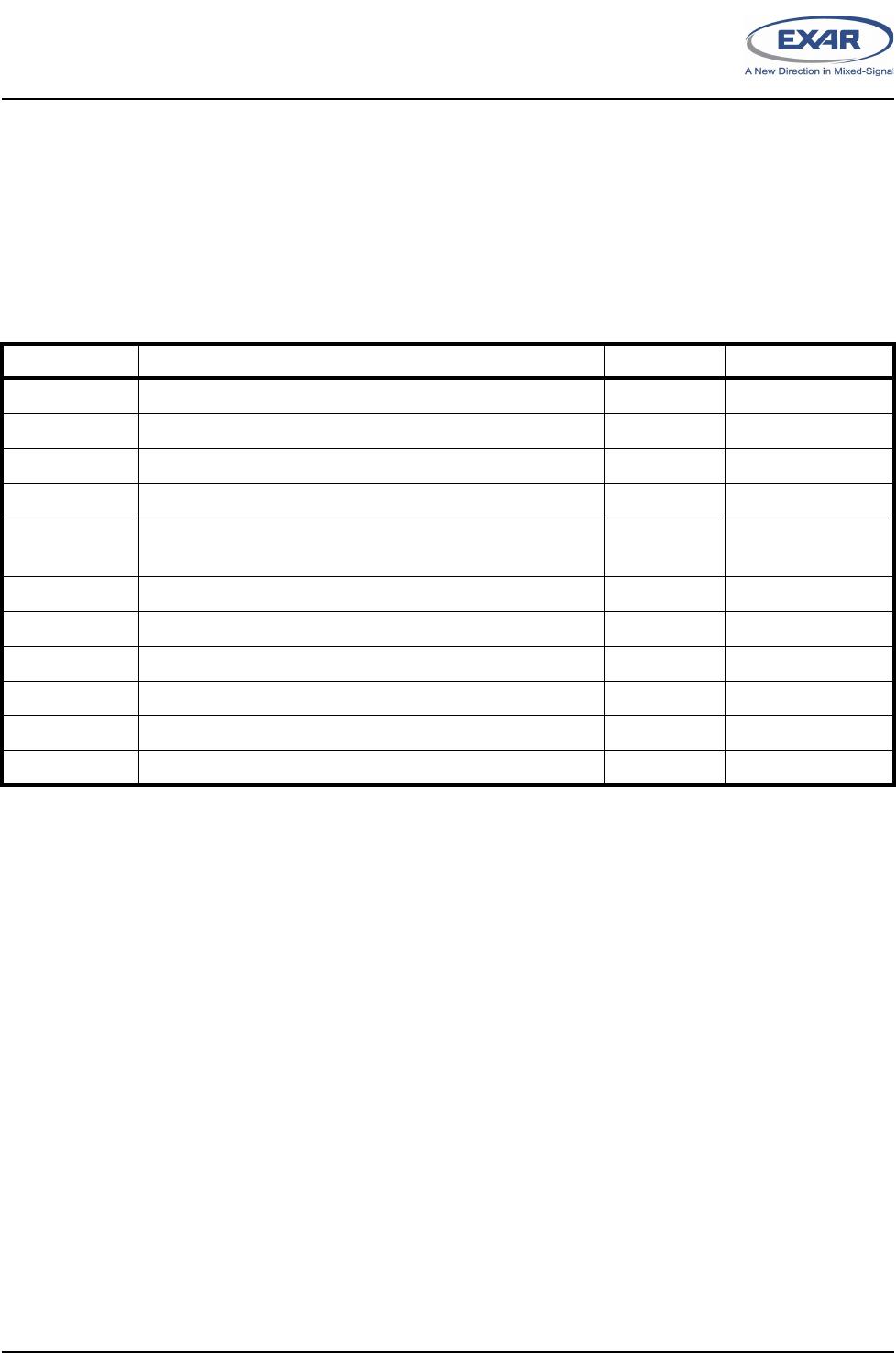

An I

2

C command byte is sent by the I

2

C master following the slave address. The command byte indicates the

address offset of the register that will be accessed. Table 2 below lists the command bytes for each register.

T

ABLE

2: I

2

C C

OMMAND

B

YTE

(R

EGISTER

A

DDRESS

)

C

OMMAND

B

YTE

R

EGISTER

N

AME

D

ESCRIPTION

R

EAD

/W

RITE

D

EFAULT

V

ALUES

0x00 GSR - GPIO State Read-Only 0xXX

0x01 OCR - Output Control Read/Write 0xFF

0x02 PIR - Input Polarity Inversion Read/Write 0x00

0x03 GCR - GPIO Configuration Read/Write 0xFF

0x04 PUR - Input Internal Pull-up Resistor Enable/Disable Read/Write 0x00 (XRA1202)

0xFF (XRA1202P)

0x05 IER - Input Interrupt Enable Read/Write 0x00

0x06 TSCR - Output Three-State Control Read/Write 0x00

0x07 ISR - Input Interrupt Status Read 0x00

0x08 REIR - Input Rising Edge Interrupt Enable Read/Write 0x00

0x09 FEIR - Input Falling Edge Interrupt Enable Read/Write 0x00

0x0A IFR - Input Filter Enable/Disable Read/Write 0xFF