XRA1202/1202P

8

8-BIT I2C/SMBUS GPIO EXPANDER WITH RESET

REV. 1.0.1

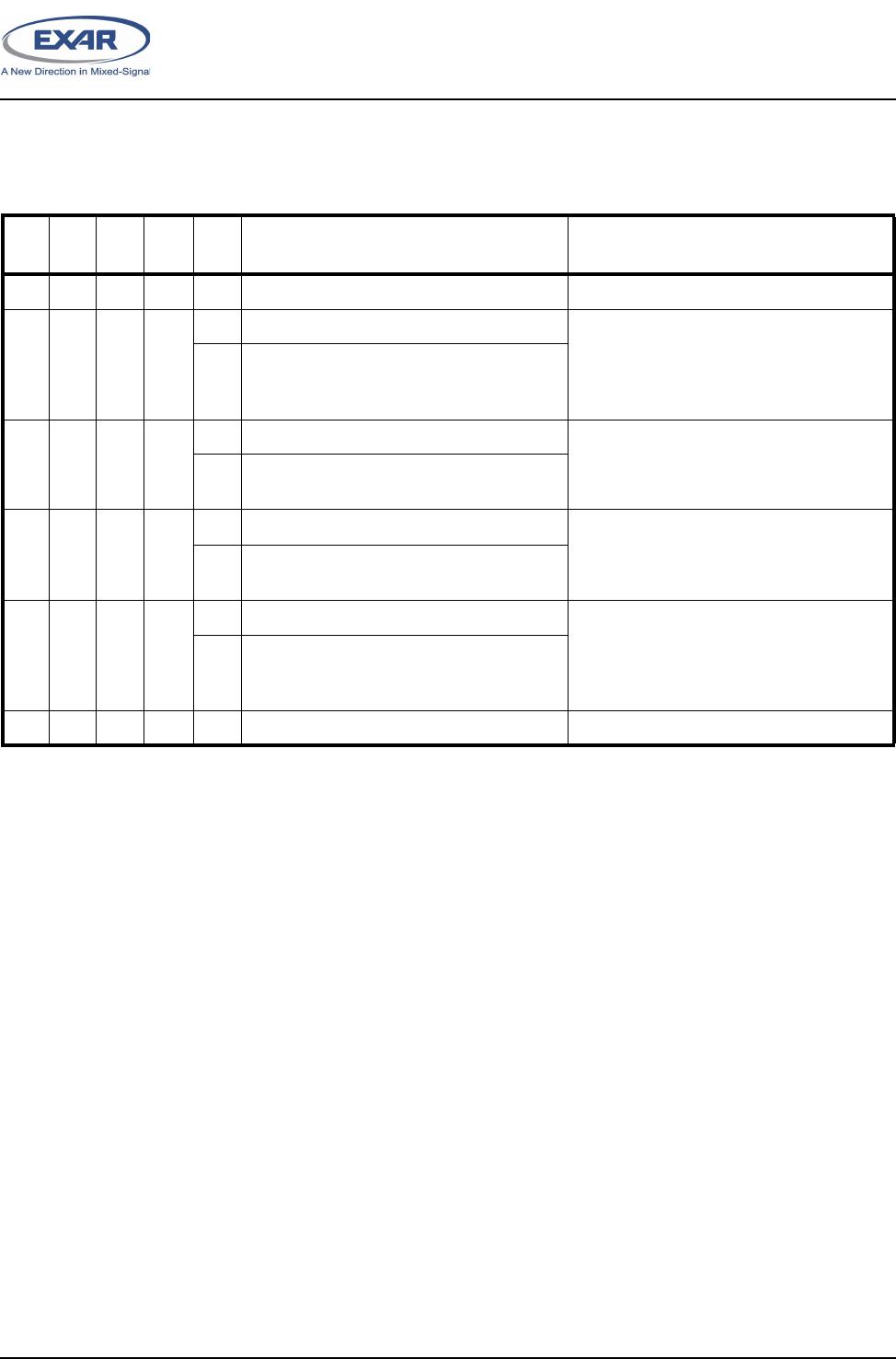

2.0 REGISTER DESCRIPTION

2.1 GPIO State Register (GSR) - Read-Only

The status of P7 - P0 can be read via this register. A read will show the current state of these pins (or the

inverted state of these pins if enabled via the PIR Register). Reading this register will clear an input interrupt

(see Table 3 for complete details). Reading this register will also return the last value written to the OCR

register for any pins that are configured as outputs (ie. this is not the same as the state of the actual output pin

since the output pin can be in three-state mode). A write to this register has no effect. The MSB of this register

corresponds with P7 and the LSB of this register corresponds with P0.

2.2 Output Control Register (OCR) - Read/Write

When P7 - P0 are defined as outputs, they can be controlled by writing to this register. Reading this register

will return the last value written to it, however, this value may not be the actual state of the output pin since

these pins can be in three-state mode. The MSB of this register corresponds with P7 and the LSB of this

register corresponds with P0.

2.3 Input Polarity Inversion Register (PIR) - Read/Write

When P7 - P0 are defined as inputs, this register inverts the polarity of the input value read from the Input Port

Register. If the corresponding bit in this register is set to ’1’, the value of this bit in the GSR Register will be the

inverted value of the input pin. If the corresponding bit in this register is set to ’0’, the value of this bit in the

GSR Register will be the actual value of the input pin. The MSB of this register corresponds with P7 and the

LSB of this register corresponds with P0.

2.4 GPIO Configuration Register (GCR) - Read/Write

This register configures the GPIOs as inputs or outputs. After power-up and reset, the GPIOs are inputs.

Setting these bits to ’0’ will enable the GPIOs as outputs. Setting these bits to ’1’ will enable the GPIOs as

inputs. The MSB of this register corresponds with P7 and the LSB of this register corresponds with P0.

2.5 Input Internal Pull-up Enable/Disable Register (PUR) - Read/Write

This register enables/disables the internal pull-up resistors for an input. After power-up and reset, the internal

pull-up resistors are disabled for the XRA1202. Writing a ’1’ to these bits will enable the internal pull-up

resistors. After power-up and reset, the internal pull-up resistors are enabled for the XRA1202P. Writing a ’0’

to these bits will disable the internal pull-up resistors. The MSB of this register corresponds with P7 and the

LSB of this register corresponds with P0.

2.6 Input Interrupt Enable Register (IER) - Read/Write

This register enables/disables the interrupts for an input. After power-up and reset, the interrupts are disabled.

Writing a ’1’ to these bits will enable the interrupt for the corresponding input pins. See Table 3 for complete

details of the interrupt behavior for various register settings. No interrupts are generated for outputs when GCR

bit is 0. The MSB of this register corresponds with P7 and the LSB of this register corresponds with P0.

2.7 Output Three-State Control Register (TSCR) - Read/Write

This register can enable/disable the three-state mode of an output. Writing a ’1’ to these bits will enable the

three-state mode for the corresponding output pins. The MSB of this register corresponds with P7 and the LSB

of this register corresponds with P0.

2.8 Input Interrupt Status Register (ISR) - Read-Only

This register reports the input pins that have generated an interrupt. See Table 3 for complete details of the

interrupt behavior for various register settings. The MSB of this register corresponds with P7 and the LSB of

this register corresponds with P0.