NCP1075A/B, NCP1076A/B, NCP1077A/B, NCP1079A/B

www.onsemi.com

27

Design Procedure

The design of an SMPS around a monolithic device does

not differ from that of a standard circuit using a controller

and a MOSFET. However, one needs to be aware of certain

characteristics specific of monolithic devices. Let us follow

the steps:

V

IN,MIN

= 90 V rms or 127 V dc once rectified,

assuming a low bulk ripple

V

IN,MAX

= 265 V rms or 375 V dc

V

OUT

= 12 V

P

OUT

= 10 W

Operating mode is CCM

η = 0.8

1. The lateral MOSFET body−diode shall never be

forward biased, either during start−up (because of

a large leakage inductance) or in normal operation,

depicted by Figure 50. This condition sets the

maximum voltage that can be reflected during t

F

As a result, the flyback voltage which is reflected

on the drain at the switch opening cannot be larger

than the input voltage. When selecting

components, you thus must adopt a turn ratio

which adheres to the following equation:

N @

ǒ

V

OUT

) V

F

Ǔ

t V

IN,MIN

(eq. 6)

2. In our case, since we operate from a 127 V dc rail

while delivering 12 V, we can select a reflected

voltage of 120 V dc maximum. Therefore, the turn

ratio Np:Ns must be smaller than

V

reflect

V

OUT

) V

F

+

120

12 ) 0.5

+ 9.6orNp:Nst 9.6

Here we choose N = 8 in this case. We will see later

on how it affects the calculation.

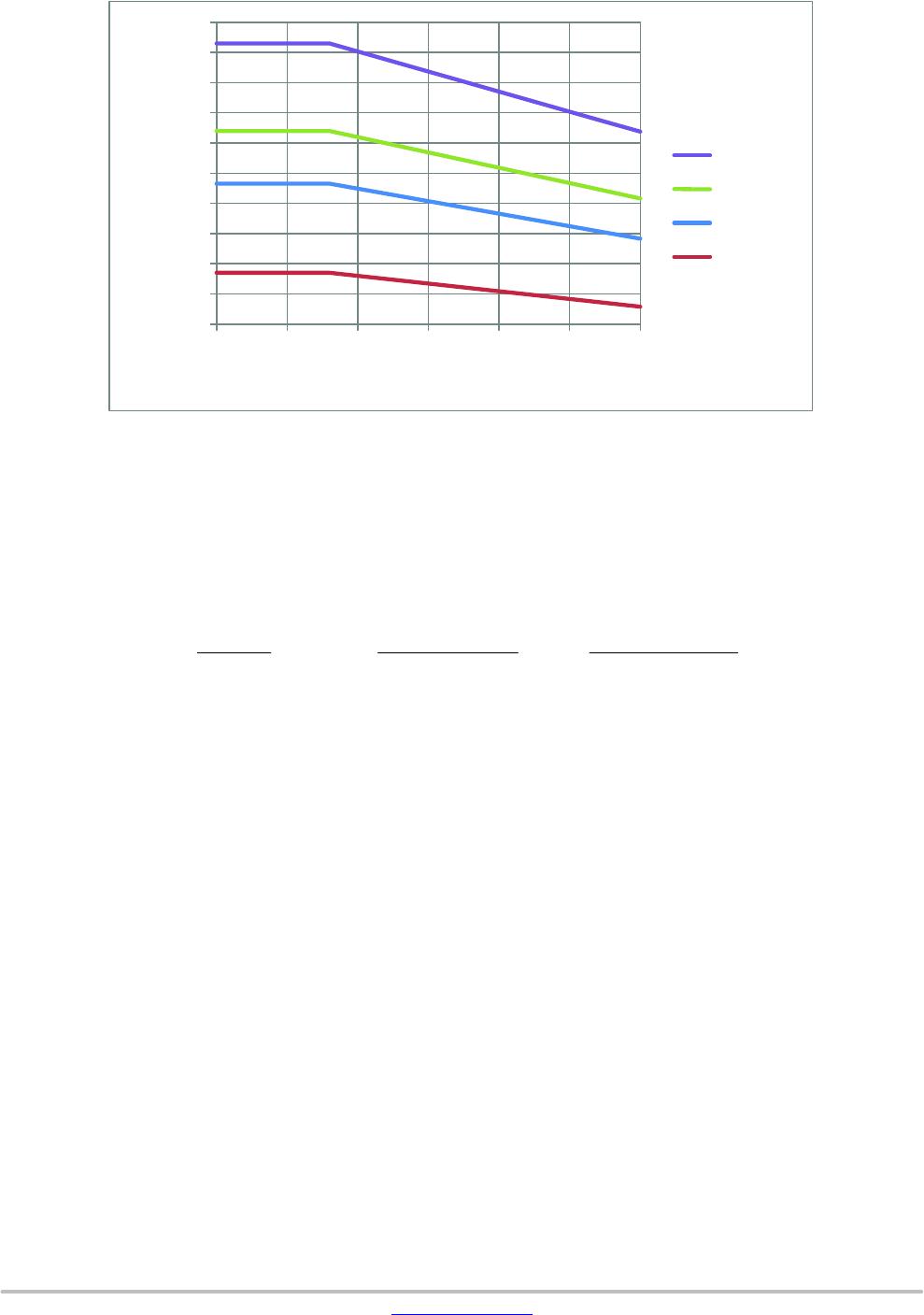

Figure 50. The Drain−Source Wave Shall Always be Positive

I

PEAK

I

VALLEY

I

avg

I

Lavg

DT

sw

T

sw

I

L

t

D

I

L

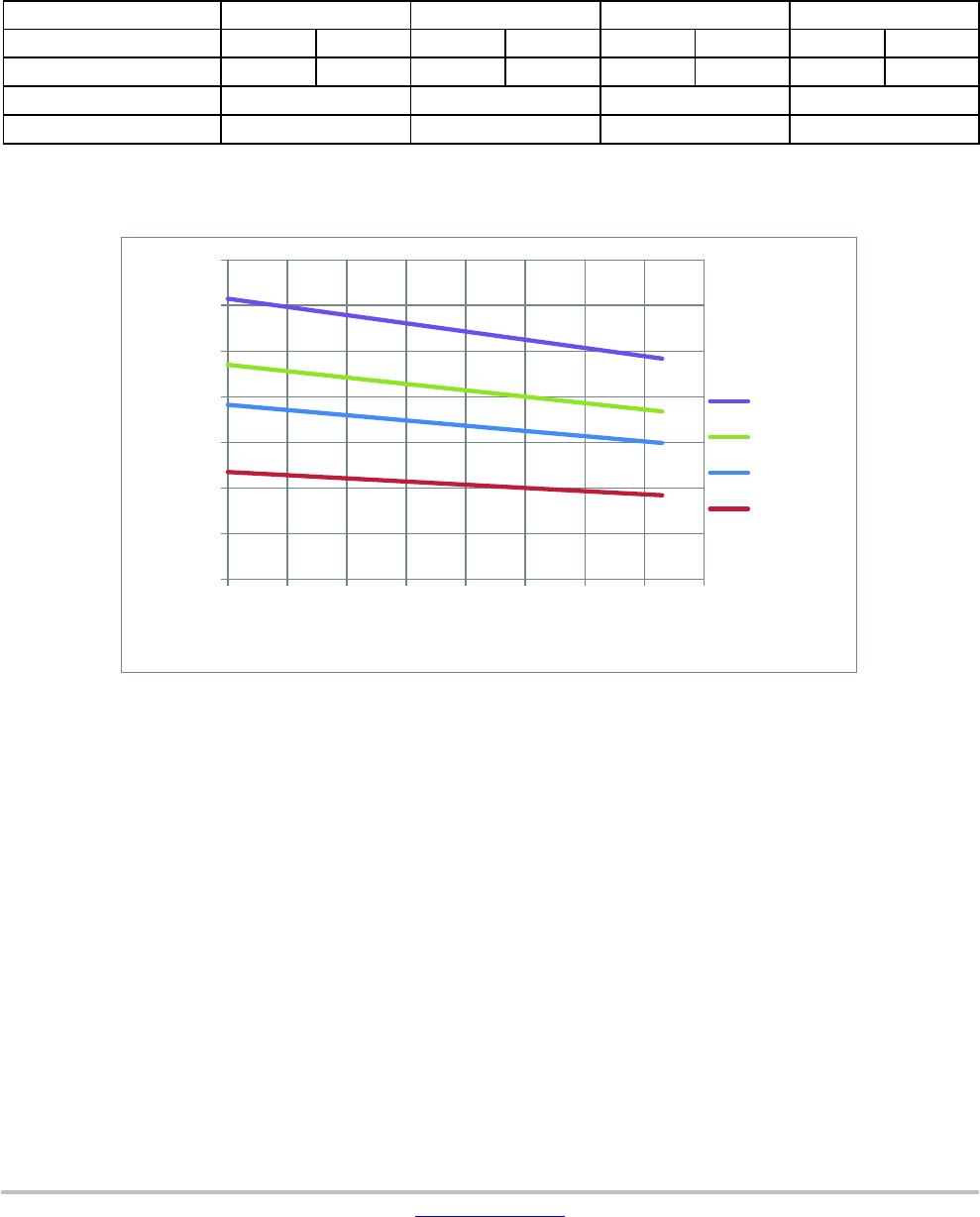

Figure 51. Primary Inductance Current

Evolution in CCM

3. Lateral MOSFETs have a poorly doped

body−diode which naturally limits their ability to

sustain the avalanche. A traditional RCD clamping

network shall thus be installed to protect the

MOSFET. In some low power applications,

a simple capacitor can also be used since

V

DRAIN,MAX

+

(eq. 7)

V

IN

) N @

ǒ

V

OUT

) V

F

Ǔ

) I

PEAK

@

L

F

C

TOT

Ǹ

where L

F

is the leakage inductance, C

TOT

the total

capacitance at the drain node (which is increased by

the capacitor you will wire between drain and

source), N the N

P

:N

S

turn ratio, V

OUT

the output

voltage, V

F

the secondary diode forward drop and

finally,

I

PEAK

the maximum peak current. Worse

case occurs when the SMPS is very close to

regulation, e.g. the

V

OUT

target is almost reached

and

I

PEAK

is still pushed to the maximum. For this