IDT8L3010I Data Sheet CRYSTAL OR DIFFERNTIALTO LVCMOS/LVTTL CLOCK BUFFER

IDT8L3010ANLGI REVISION A JANUARY 12, 2012 9 ©2012 Integrated Device Technology, Inc.

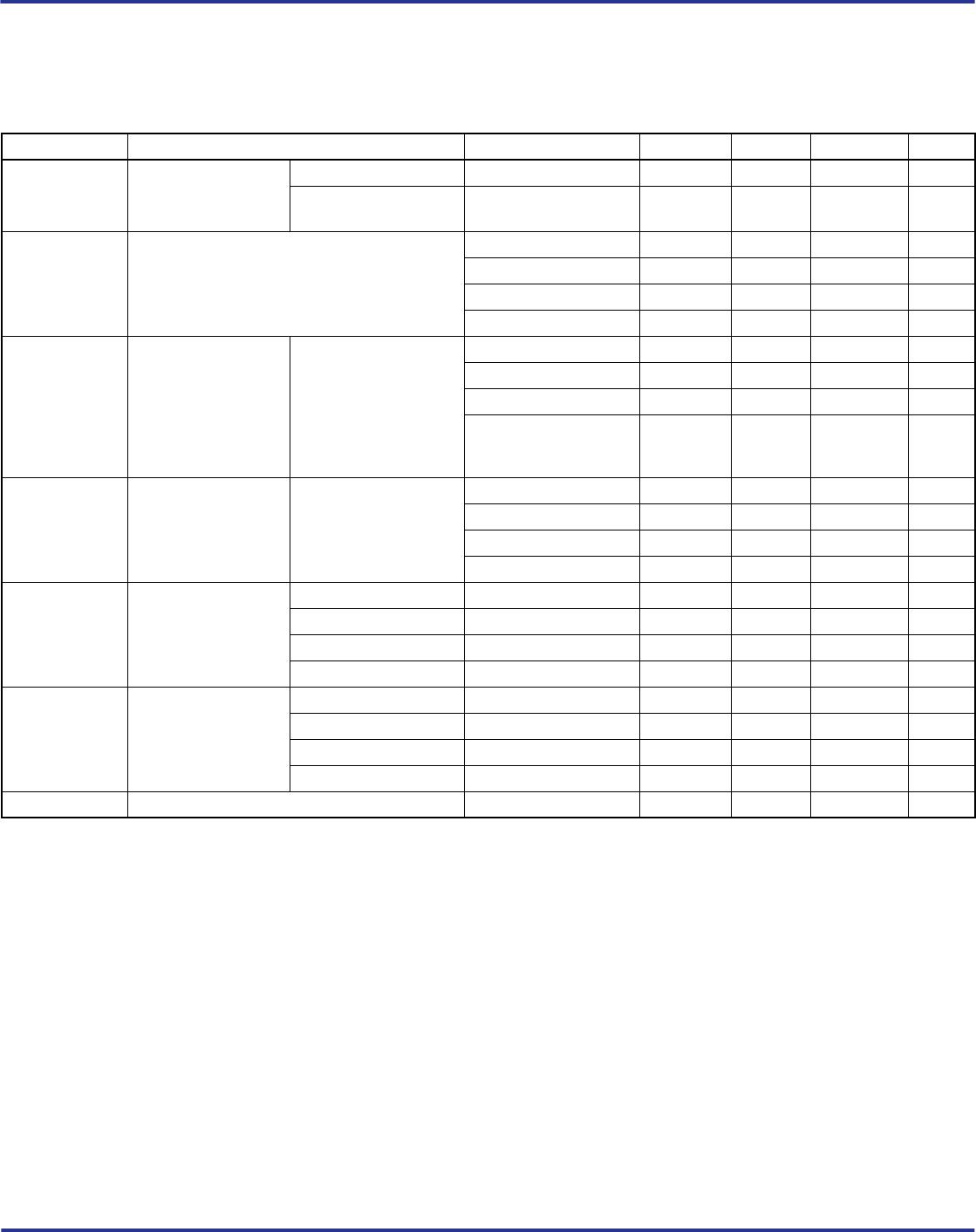

Additive Phase Jitter (3.3V)

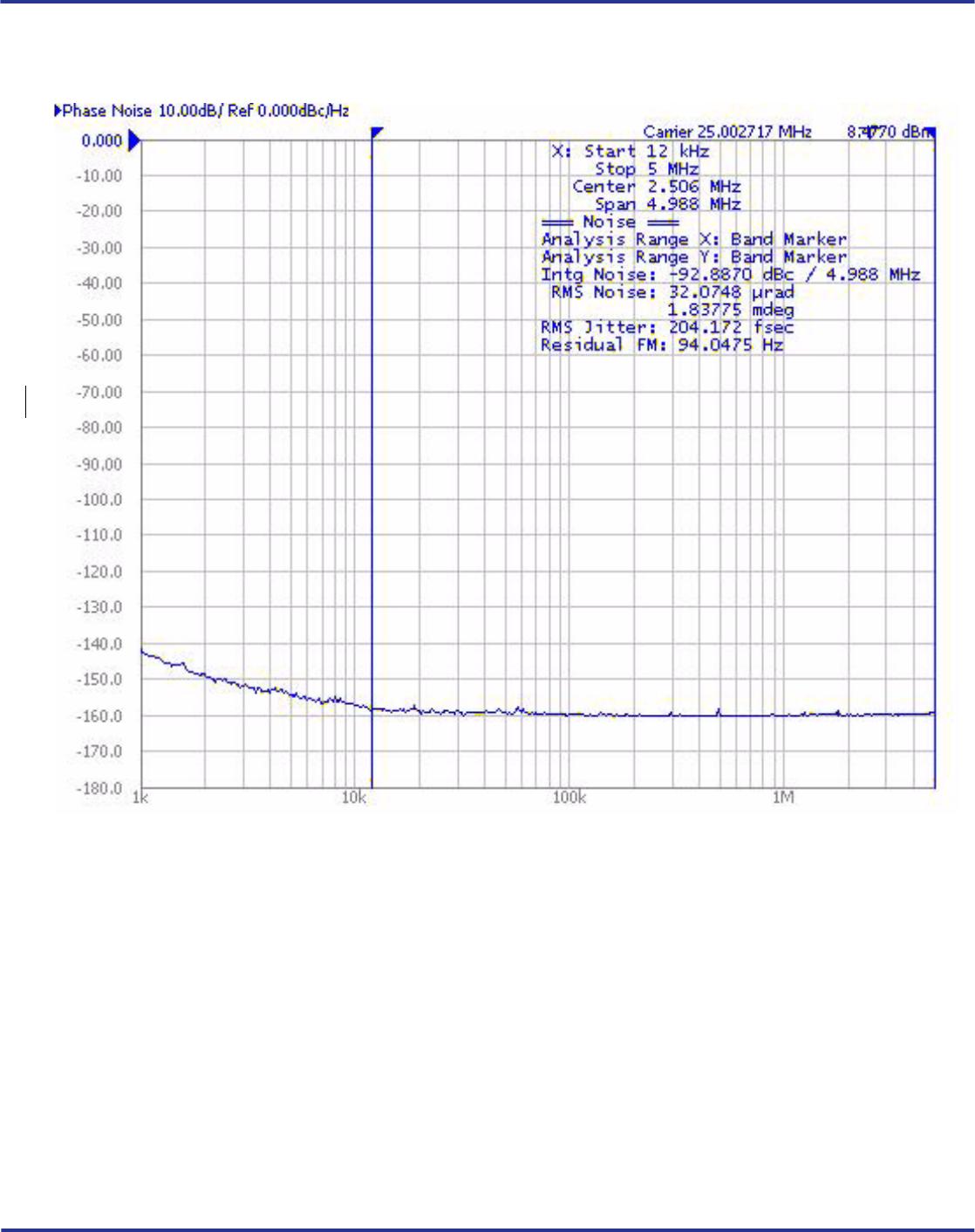

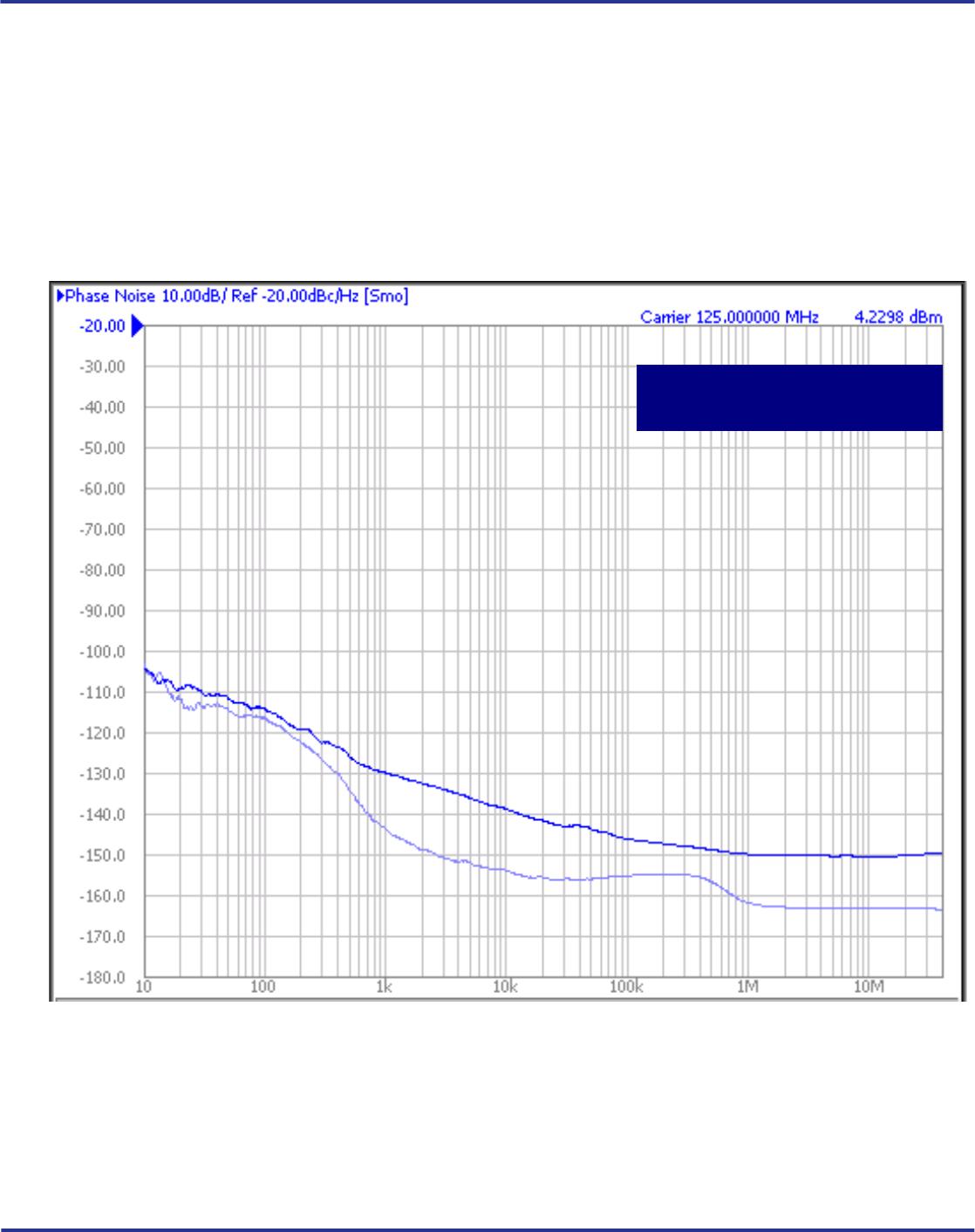

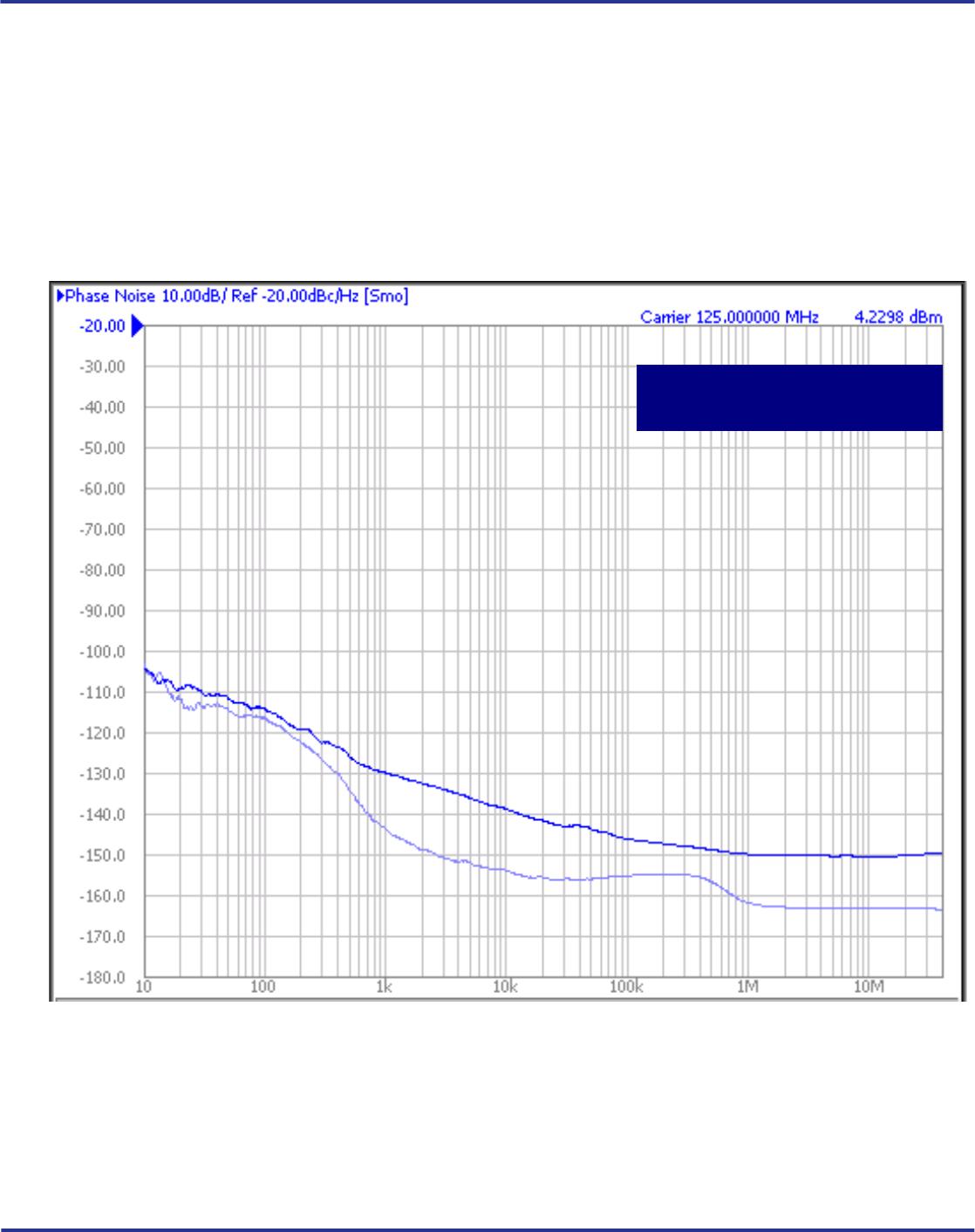

The spectral purity in a band at a specific offset from the fundamental

compared to the power of the fundamental is called the dBc Phase

Noise. This value is normally expressed using a Phase noise plot

and is most often the specified plot in many applications. Phase noise

is defined as the ratio of the noise power present in a 1Hz band at a

specified offset from the fundamental frequency to the power value of

the fundamental. This ratio is expressed in decibels (dBm) or a ratio

of the power in the 1Hz band to the power in the fundamental. When

the required offset is specified, the phase noise is called a dBc value,

which simply means dBm at a specified offset from the fundamental.

By investigating jitter in the frequency domain, we get a better

understanding of its effects on the desired application over the entire

time record of the signal. It is mathematically possible to calculate an

expected bit error rate given a phase noise plot.

As with most timing specifications, phase noise measurements has

issues relating to the limitations of the equipment. Often the noise

floor of the equipment is higher than the noise floor of the device. The

phase noise is dependent on the input source and measurement

equipment.

The signal generator used is, “Rohde & Schwarz SMA100A,

measured with Agilent 5052A”.

Additive Phase Jitter @ 125MHz

12kHz to 20MHz = 0.24ps (typical)

SSB Phase Noise dBc/Hz

Offset from Carrier Frequency (Hz)