46

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

65,536 x 36 and 131,072 x 36

THE INSTRUCTION REGISTER

The Instruction register allows an instruction to be shifted in serially into the

processor at the rising edge of TCLK.

The Instruction is used to select the test to be performed, or the test data

register to be accessed, or both. The instruction shifted into the register is latched

at the completion of the shifting process when the TAP controller is at Update-

IR state.

The instruction register must contain 4 bit instruction register-based cells

which can hold instruction data. These mandatory cells are located nearest the

serial outputs they are the least significant bits.

TEST DATA REGISTER

The Test Data register contains three test data registers: the Bypass, the

Boundary Scan register and Device ID register.

These registers are connected in parallel between a common serial input

and a common serial data output.

The following sections provide a brief description of each element. For a

complete description, refer to the IEEE Standard Test Access Port Specification

(IEEE Std. 1149.1-1990).

TEST BYPASS REGISTER

The register is used to allow test data to flow through the device from TDI

to TDO. It contains a single stage shift register for a minimum length in serial path.

When the bypass register is selected by an instruction, the shift register stage

is set to a logic zero on the rising edge of TCLK when the TAP controller is in

the Capture-DR state.

The operation of the bypass register should not have any effect on the

operation of the device in response to the BYPASS instruction.

THE BOUNDARY-SCAN REGISTER

The Boundary Scan Register allows serial data TDI be loaded in to or read

out of the processor input/output ports. The Boundary Scan Register is a part

of the IEEE 1149.1-1990 Standard JTAG Implementation.

THE DEVICE IDENTIFICATION REGISTER

The Device Identification Register is a Read Only 32-bit register used to

specify the manufacturer, part number and version of the processor to be

determined through the TAP in response to the IDCODE instruction.

IDT JEDEC ID number is 0xB3. This translates to 0x33 when the parity

is dropped in the 11-bit Manufacturer ID field.

For the IDT72V36100/72V36110, the Part Number field contains the

following values:

JTAG INSTRUCTION REGISTER

The Instruction register allows instruction to be serially input into the device

when the TAP controller is in the Shift-IR state. The instruction is decoded to

perform the following:

• Select test data registers that may operate while the instruction is

current. The other test data registers should not interfere with chip

operation and the selected data register.

• Define the serial test data register path that is used to shift data between

TDI and TDO during data register scanning.

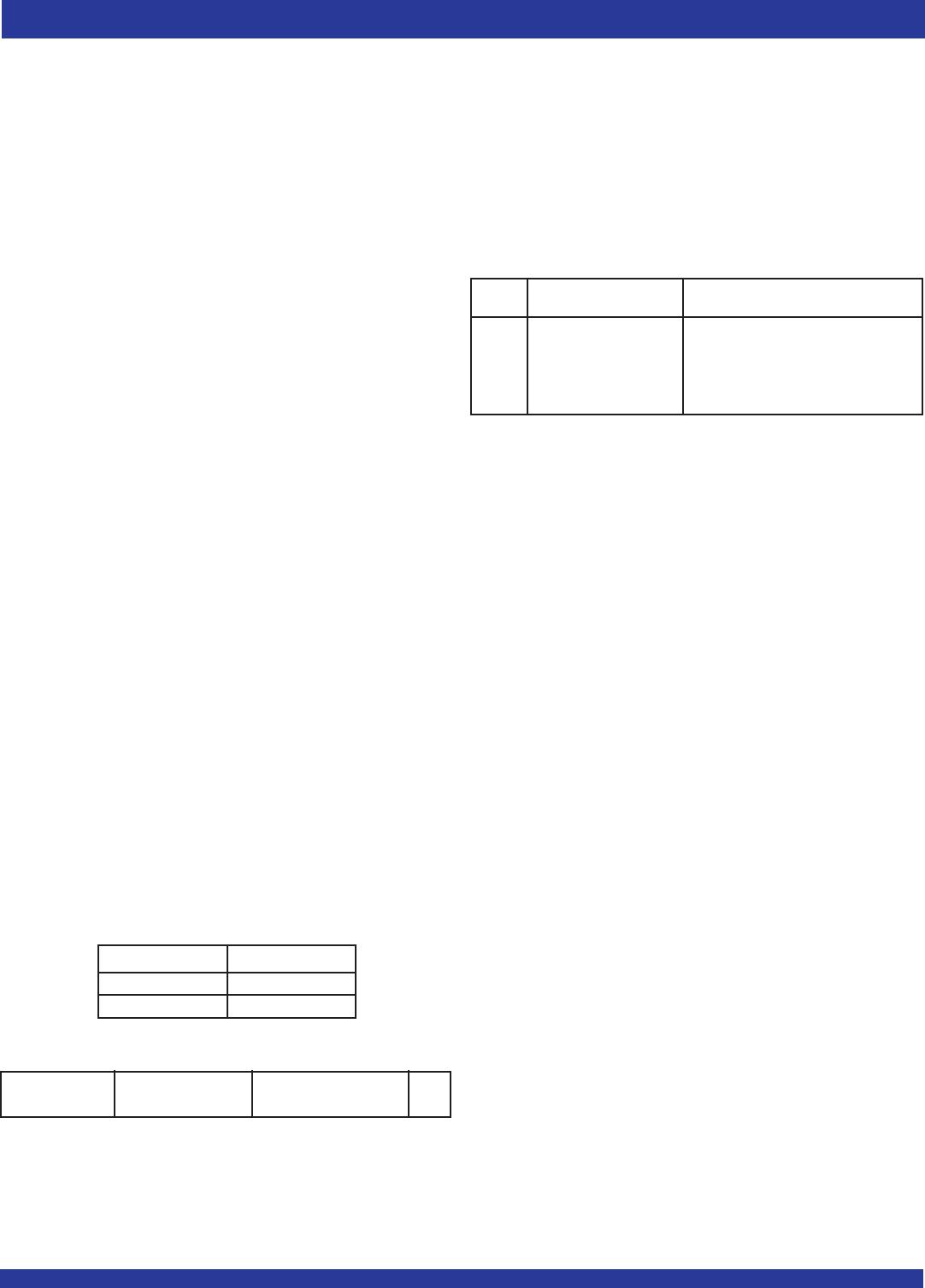

The Instruction Register is a 4 bit field (i.e.IR3, IR2, IR1, IR0) to decode 16

different possible instructions. Instructions are decoded as follows.

Hex Instruction Function

Value

0x00 EXTEST Select Boundary Scan Register

0x02 IDCODE Select Chip Identification data register

0x01 SAMPLE/PRELOAD Select Boundary Scan Register

0x03 HIGH-IMPEDANCE JTAG

0x0F BYPASS Select Bypass Register

Table 6. JTAG Instruction Register Decoding

The following sections provide a brief description of each instruction. For

a complete description refer to the IEEE Standard Test Access Port Specification

(IEEE Std. 1149.1-1990).

EXTEST

The required EXTEST instruction places the IC into an external boundary-

test mode and selects the boundary-scan register to be connected between TDI

and TDO. During this instruction, the boundary-scan register is accessed to

drive test data off-chip via the boundary outputs and receive test data off-chip

via the boundary inputs. As such, the EXTEST instruction is the workhorse of

IEEE. Std 1149.1, providing for probe-less testing of solder-joint opens/shorts

and of logic cluster function.

IDCODE

The optional IDCODE instruction allows the IC to remain in its functional mode

and selects the optional device identification register to be connected between

TDI and TDO. The device identification register is a 32-bit shift register containing

information regarding the IC manufacturer, device type, and version code.

Accessing the device identification register does not interfere with the operation

of the IC. Also, access to the device identification register should be immediately

available, via a TAP data-scan operation, after power-up of the IC or after the

TAP has been reset using the optional TRST pin or by otherwise moving to the

Test-Logic-Reset state.

SAMPLE/PRELOAD

The required SAMPLE/PRELOAD instruction allows the IC to remain in a

normal functional mode and selects the boundary-scan register to be connected

between TDI and TDO. During this instruction, the boundary-scan register can

be accessed via a date scan operation, to take a sample of the functional data

entering and leaving the IC. This instruction is also used to preload test data into

the boundary-scan register before loading an EXTEST instruction.

Device Part# Field

IDT72V36100 04DE

IDT72V36110 04DF

IDT72V36100/72V36110 JTAG Device Identification Register

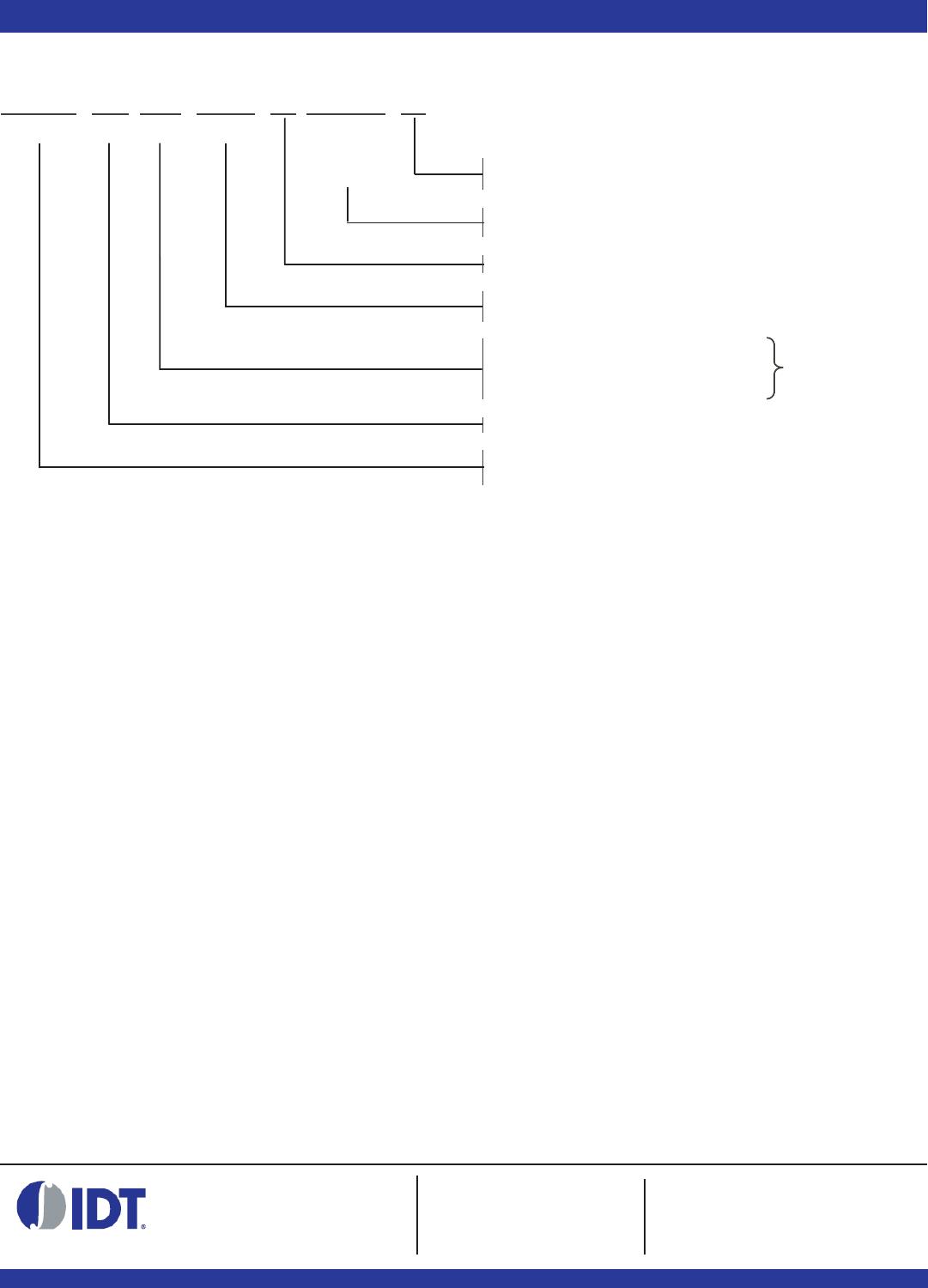

31(MSB) 28 27 12 11 1 0(LSB)

Version (4 bits) Part Number (16-bit) Manufacturer ID (11-bit)

0X0 0X33 1