© March 2010 Altera Corporation Stratix III Device Handbook, Volume 1

1. Stratix III Device Family Overview

The Stratix

®

III family provides one of the most architecturally advanced,

high-performance, low-power FPGAs in the marketplace.

Stratix III FPGAs lower power consumption through Altera’s innovative

Programmable Power Technology, which provides the ability to turn on the

performance where needed and turn down the power consumption for blocks not in

use. Selectable Core Voltage and the latest in silicon process optimizations are also

employed to deliver the industry’s lowest power, high-performance FPGAs.

Specifically designed for ease of use and rapid system integration, the Stratix III

FPGA family offers two variants optimized to meet different application needs:

■ The Stratix III L family provides balanced logic, memory, and multiplier ratios for

mainstream applications.

■ The Stratix III E family is memory- and multiplier-rich for data-centric

applications.

Modular I/O banks with a common bank structure for vertical migration lend

efficiency and flexibility to the high-speed I/O. Package and die enhancements with

dynamic on-chip termination, output delay, and current strength control provide

best-in-class signal integrity.

Based on a 1.1-V, 65-nm all-layer copper SRAM process, the Stratix III family is a

programmable alternative to custom ASICs and programmable processors for

high-performance logic, digital signal processing (DSP), and embedded designs.

Stratix III devices include optional configuration bit stream security through volatile

or non-volatile 256-bit Advanced Encryption Standard (AES) encryption. Where

ultra-high reliability is required, Stratix III devices include automatic error detection

circuitry to detect data corruption by soft errors in the configuration random-access

memory (CRAM) and user memory cells.

Features Summary

Stratix III devices offer the following features:

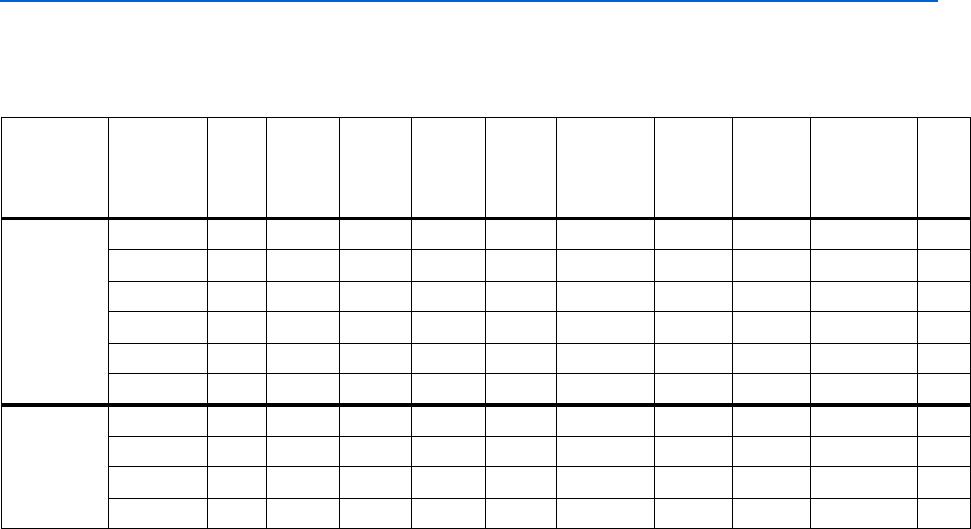

■ 48,000 to 338,000 equivalent logic elements (LEs) ( refer to Ta ble 1–1 )

■ 2,430 to 20,497 Kbits of enhanced TriMatrix memory consisting of three RAM

block sizes to implement true dual-port memory and FIFO buffers

■ High-speed DSP blocks provide dedicated implementation of 9×9, 12×12, 18×18,

and 36×36 multipliers (at up to 550 MHz), multiply-accumulate functions, and

finite impulse response (FIR) filters

■ I/O:GND:PWR ratio of 8:1:1 along with on-die and on-package decoupling for

robust signal integrity

■ Programmable Power Technology, which minimizes power while maximizing

device performance

SIII51001-1.8