21

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

IDT72V295/72V2105 3.3V HIGH DENSITY CMOS

SUPERSYNC FIFO

TM

131,072 x 18, 262,144 x 18

NOTES:

1. Retransmit setup is complete after OR returns LOW.

2. No more than D - 2 words may be written to the FIFO between Reset (Master or Partial) and Retransmit setup. Therefore, IR will be LOW throughout the Retransmit setup

procedure. D = 131,073 for the IDT72V295 and 262,145 for the IDT72V2105.

3. OE = LOW

4. W1, W2, W3 = first, second and third words written to the FIFO after Master Reset.

5. There must be at least two words written to the FIFO before a Retransmit operation can be invoked.

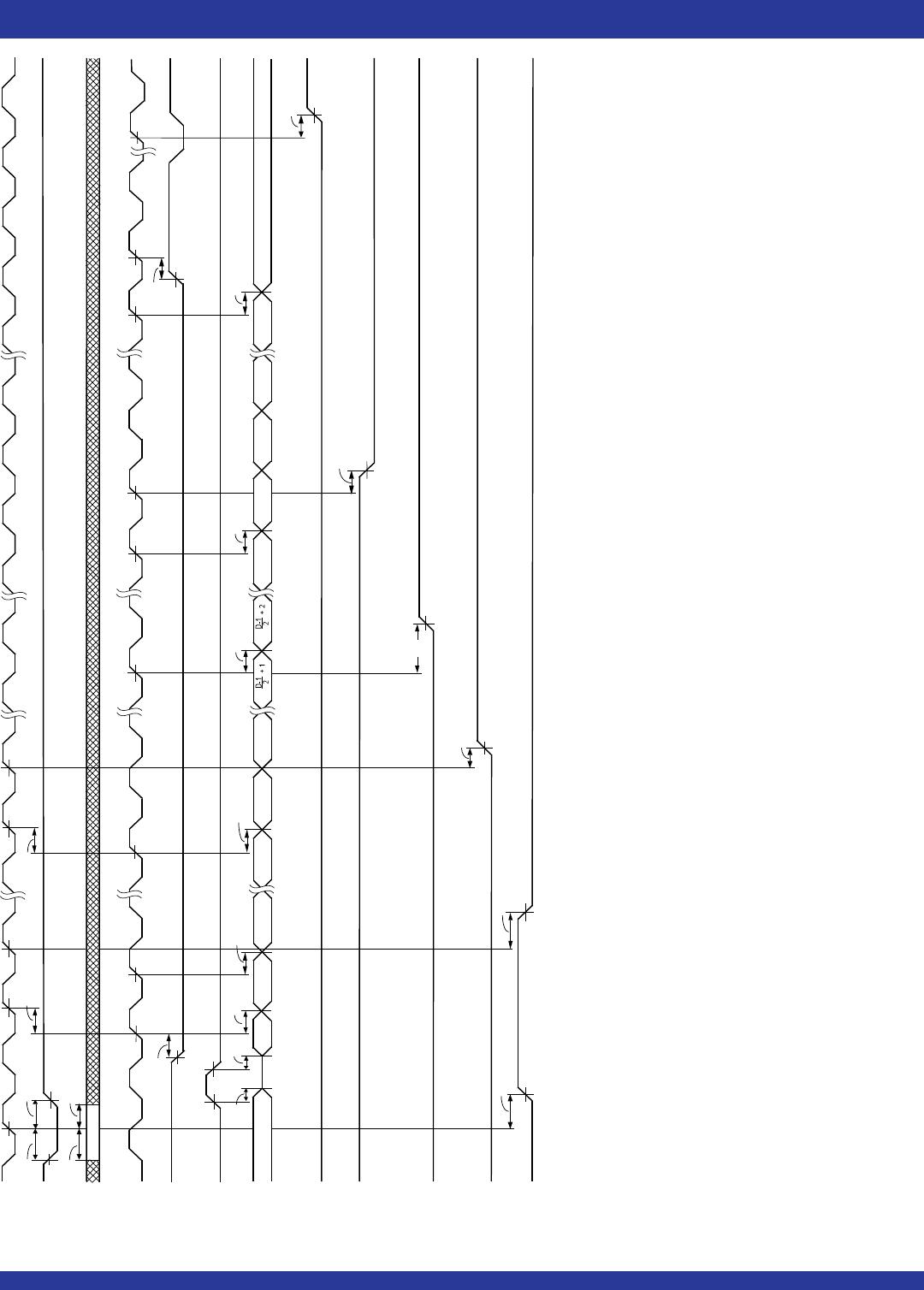

Figure 12. Retransmit Timing (FWFT Mode)

Figure 13. Serial Loading of Programmable Flag Registers (IDT Standard and FWFT Modes)

NOTE:

1. X = 16 for the IDT72V295 and X = 17 for the IDT72V2105.

tREF

tRTS

tENH

4668 drw 15

tENS

Wx

WCLK

RCLK

REN

RT

OR

PAF

HF

PAE

Q

0 - Qn

tSKEW2

12

1

tPAF

tHF

tPAE

tREF

Wx+1

2

W2

(4)

tENH

tRTS

WEN

tENS

W1

(4)

tENS

3

4

tENH

W3

(4)

tAtA

tA

W4

tA

WCLK

SEN

SI

4668 drw 16

t

ENH

t

ENS

t

LDS

LD

t

DS

BIT 0

EMPTY OFFSET

BIT X

(1)

BIT 0

FULL OFFSET

t

ENH

BIT X

(1)

t

LDH

t

LDH

t

DH