10©2016 Integrated Device Technology, Inc Revision C January 27, 2016

894D115I-04 Data Sheet

Application Information

Power Supply Filtering Technique

As in any high speed analog circuitry, the power supply pins are

vulnerable to random noise. To achieve optimum jitter perform-

ance, power supply isolation is required. The 894D115I-04

provides separate power supplies to isolate any high switching

noise from the outputs to the internal PLL. V

DD

and V

DDA

should

be individually connected to the power supply plane through vias,

and 0.01µF bypass capacitors should be used for each pin. Figure

2 illustrates this for a generic V

DD

pin and also shows that V

DDA

requires that an additional 10 resistor along with a 10F bypass

capacitor be connected to the V

DDA

pin.

Figure 2. Power Supply Filtering

Recommendations for Unused Input and Output Pins

Inputs:

LVCMOS Control Pins

All control pins have internal pull-ups or pull-downs; additional

resistance is not required but can be added for additional

protection. A 1k resistor can be used.

Outputs:

LVDS Outputs

All unused LVDS output pairs can be either left floating or

terminated with 100 across. If they are left floating, there should

be no trace attached.

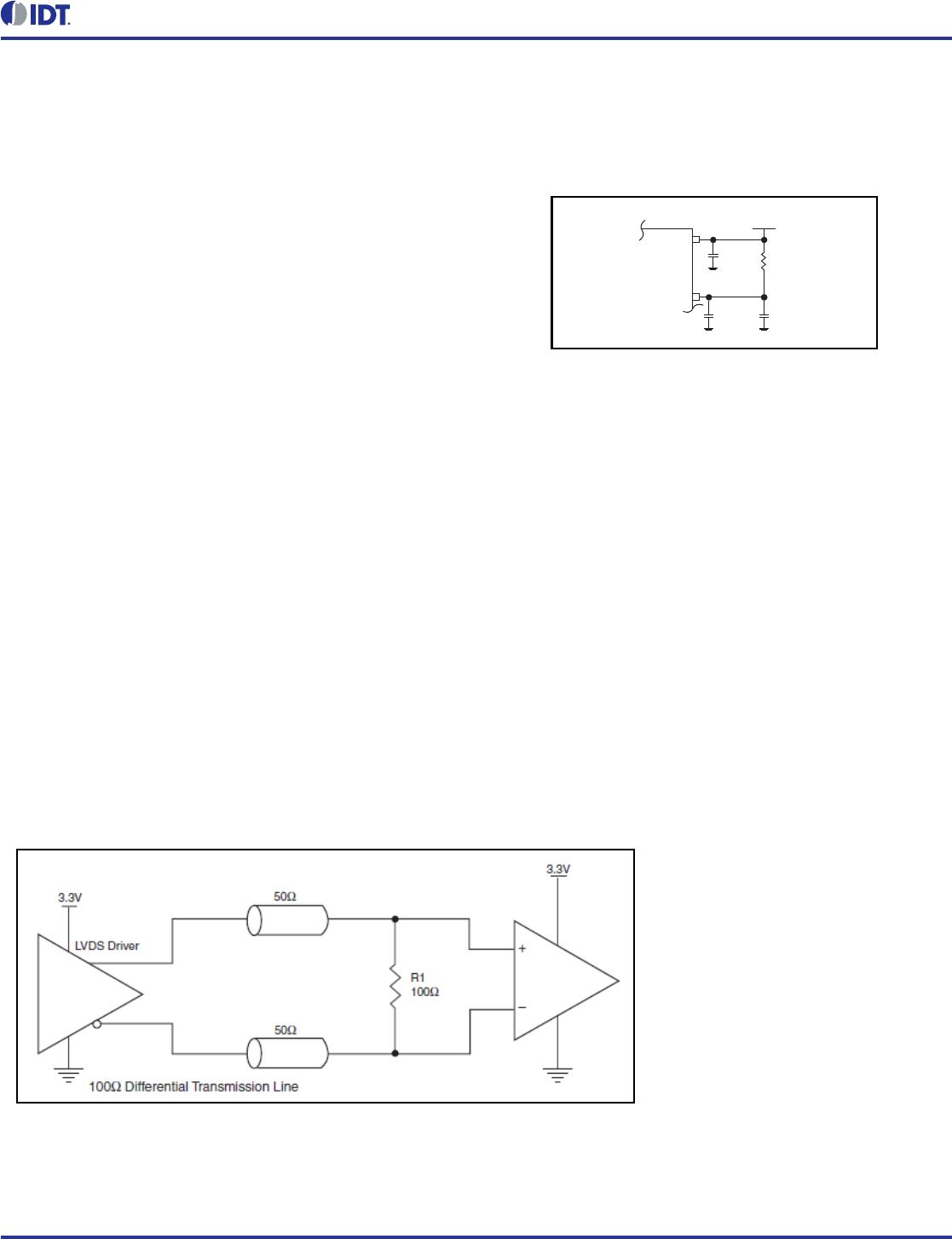

3.3V LVDS Driver Termination

A general LVDS interface is shown in Figure 3. In a 100 differ-

ential transmission line environment, LVDS drivers require a

matched load termination of 100 across near the receiver input.

Figure 3. Typical LVDS Driver Termination

V

DD

V

DDA

3.3V

10Ω

10µF.01µF

.01µF