7©2016 Integrated Device Technology, Inc Revision C January 27, 2016

894D115I-04 Data Sheet

AC Electrical Characteristics

Table 6. AC Characteristics, V

DD

= 3.3V ± 5%, V

EE

= 0V, T = -40°C to 85°C

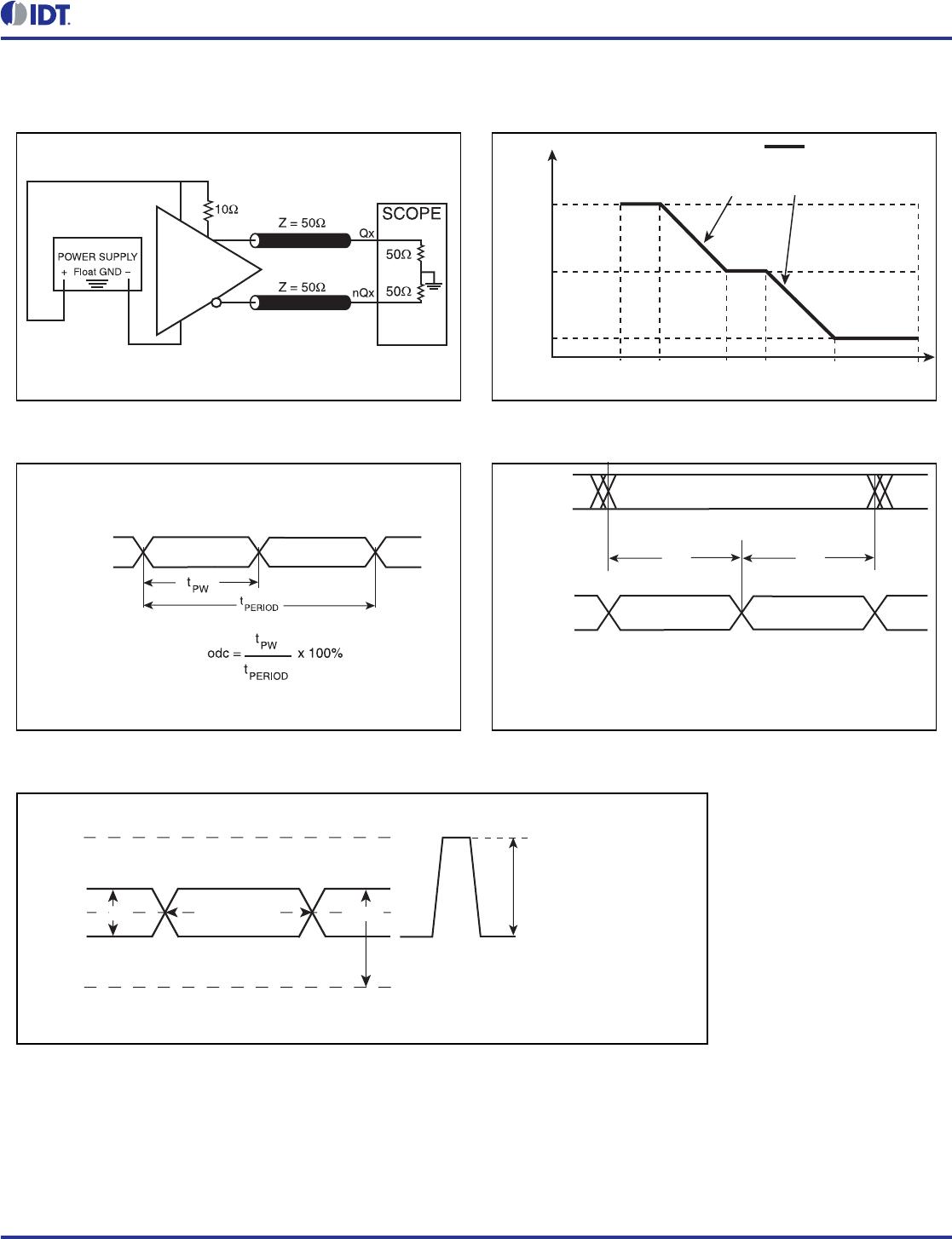

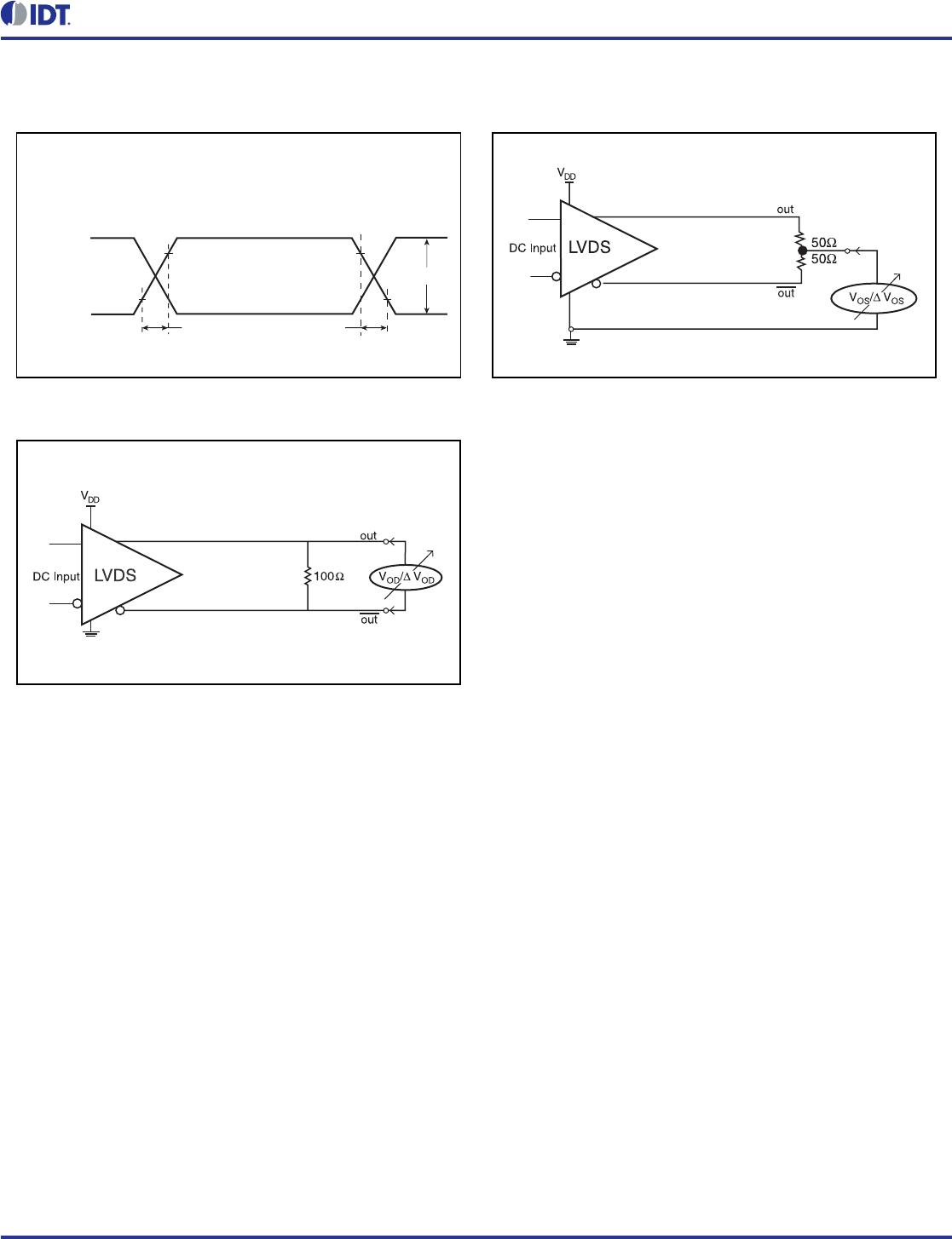

NOTE 1: See diagram in Parameter Measurement Information section.

Parameter Symbol Test Conditions Minimum Typical Maximum Units

f

VCO

VCO Center Frequency 622.08 MHz

f

TOL

CRU’s Reference Clock

Frequency Tolerance

-250 250 ppm

fT

REF_CLK

OC-12/STS-12 Capture Range

With respect to the fixed

reference frequency

±500 ppm

t

LOCK

Acquisition

Lock Time

OC-12/STS-12

Valid REF_CLK and device already

powered-up

16 µs

J

GEN_CLK

Jitter

Generation

CLK_OUT/

nCLK_OUT

14ps rms (max.) jitter on

DATA_IN/nDATA_IN

0.005 0.01 UI

J

TOL

Jitter

Tolerance

OC-12/STS-12;

NOTE 1

Sinusoidal input jitter of DATA_IN/

nDATA_IN from 250kHz to 5MHz

0.45 UI

t

R

/ t

F

Output Rise/Fall Time; NOTE 1 20% to 80% 500 ps

odc Output Duty Cycle; NOTE 1 20% minimum transition density 45 55 %

t

S

Setup Time; NOTE 1

STS-3 2000 3220 ps

STS-12 450 800 ps

t

H

Hold Time; NOTE 1

STS-3 3000 3220 ps

STS-12 650 800 ps