4©2016 Integrated Device Technology, Inc Revision C January 27, 2016

894D115I-04 Data Sheet

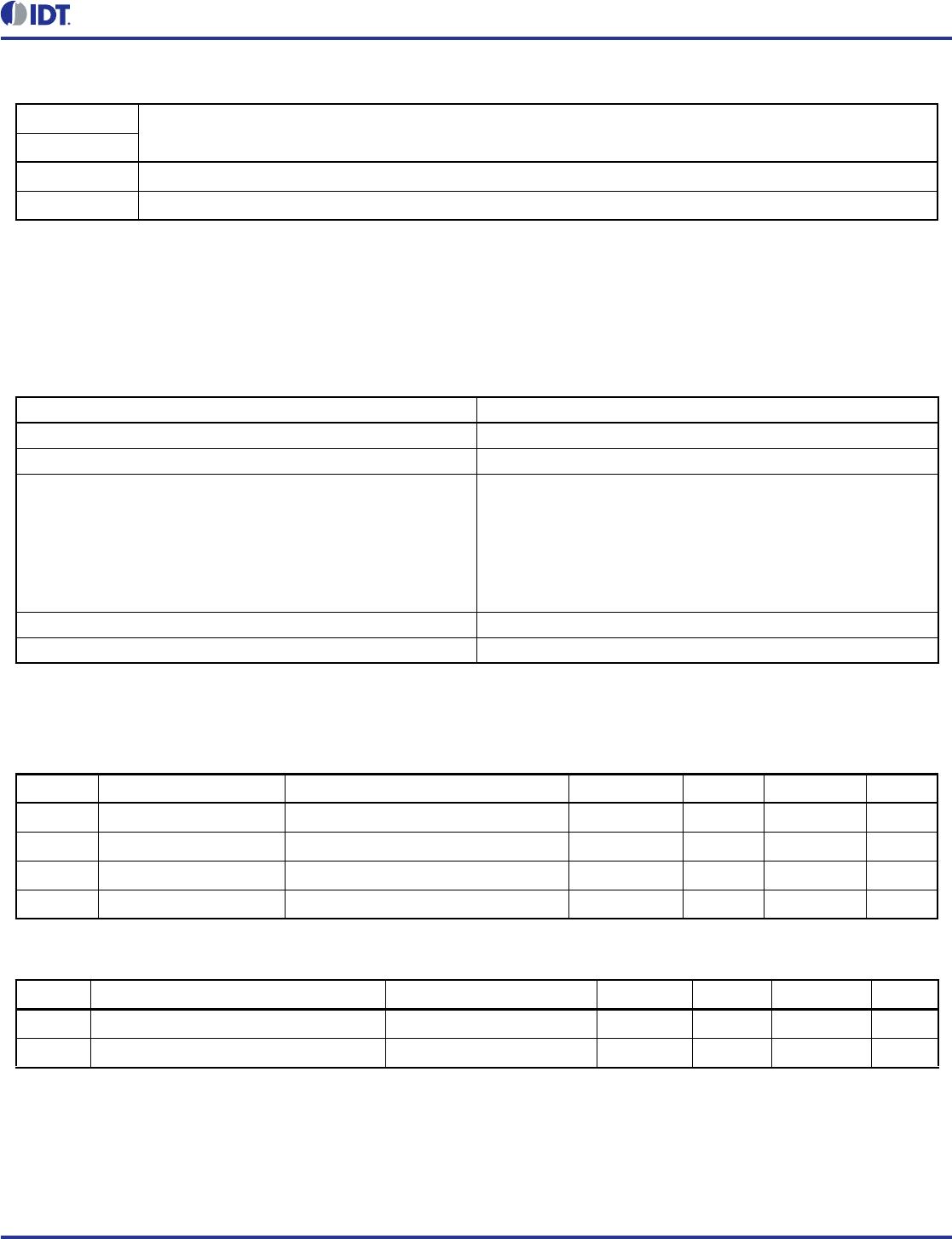

Table 3. Pin Characteristics

Function Tables

Table 4A. LOCK_DET Operation Table

Table 4B. STS12 Mode Configuration Table

Table 4C. LOCK_REFN Mode Configuration Table

Table 4D. SD Mode Configuration Table

Symbol Parameter Test Conditions Minimum Typical Maximum Units

C

IN

Input Capacitance 4 pF

R

PULLUP

Input Pullup Resistor 51 k

R

PULLDOWN

Input Pulldown Resistor 51 k

Operation

Output

LOCK_DET

The PLL is not locked to the serial input data stream if any of these three conditions occur:

A. Internal oscillator and REF_CLK input frequency are not within 500ppm of each other.

B. SD input is at logic LOW state.

C. LOCK_REFN is at logic LOW state.

LOW

When the PLL is locked to the serial input data stream, the CLK_OUT and DATA_OUT signals are valid. HIGH

Input

OperationSTS12

0

STM-1 (OC-3, STS-3) operation. The clock/data recovery circuit attempts to recover the clock from a 155.52 Mbit/s

input data stream. The output clock frequency is 155.52MHz.

1

STM-4 (OC-12, STS-12) operation. The clock/data recovery circuit attempts to recover the clock from a 622.08 Mbit/s

input data stream. The output clock frequency is 622.08MHz.

Input

OperationLOCK_REFN

0

Lock to reference clock. CLK_OUT/nCLK_OUT output frequency is within ±500ppm of the reference clock

(REF_CLK). DATA_OUT is set to logic LOW state and nDATA_OUT is set to logic HIGH state. (DATA_OUT = L,

nDATA_OUT = H).

1 Normal operation.

Input

OperationSD

0

Indicates a loss-of-signal (LOS) condition to the device. CLK_OUT/nCLK_OUT output frequency is within ±500ppm

of the reference clock (REF_CLK). DATA_OUT is set to logic LOW state and nDATA_OUT is set to logic HIGH state.

(DATA_OUT = L, nDATA_OUT = H).

1 Normal operation.