2008-2016 Microchip Technology Inc. DS20002122D-page 11

11AA02E48/11AA02E64

4.3 Write Instruction

Prior to any attempt to write data to the 11AA02EXX,

the write enable latch must be set by issuing the WREN

instruction (see Section 4.4 “Write Enable (WREN)

and Write Disable (WRDI) Instructions”).

Once the write enable latch is set, the user may

proceed with issuing a WRITE instruction (including the

header and device address bytes) followed by the MSB

and LSB of the Word Address. Once the last

Acknowledge sequence has been performed, the

master transmits the data byte to be written.

The 11AA02EXX features a 16-byte page buffer,

meaning that up to 16 bytes can be written at one time.

To utilize this feature, the master can transmit up to

16 data bytes to the 11AA02EXX, which are

temporarily stored in the page buffer. After each data

byte, the master sends a MAK, indicating whether or

not another data byte is to follow. A NoMAK indicates

that no more data is to follow, and as such will initiate

the internal write cycle.

Upon receipt of each word, the four lower-order

Address Pointer bits are internally incremented by one.

The higher-order bits of the word address remain

constant. If the master should transmit data past the

end of the page, the address counter will roll over to the

beginning of the page, where further received data will

be written.

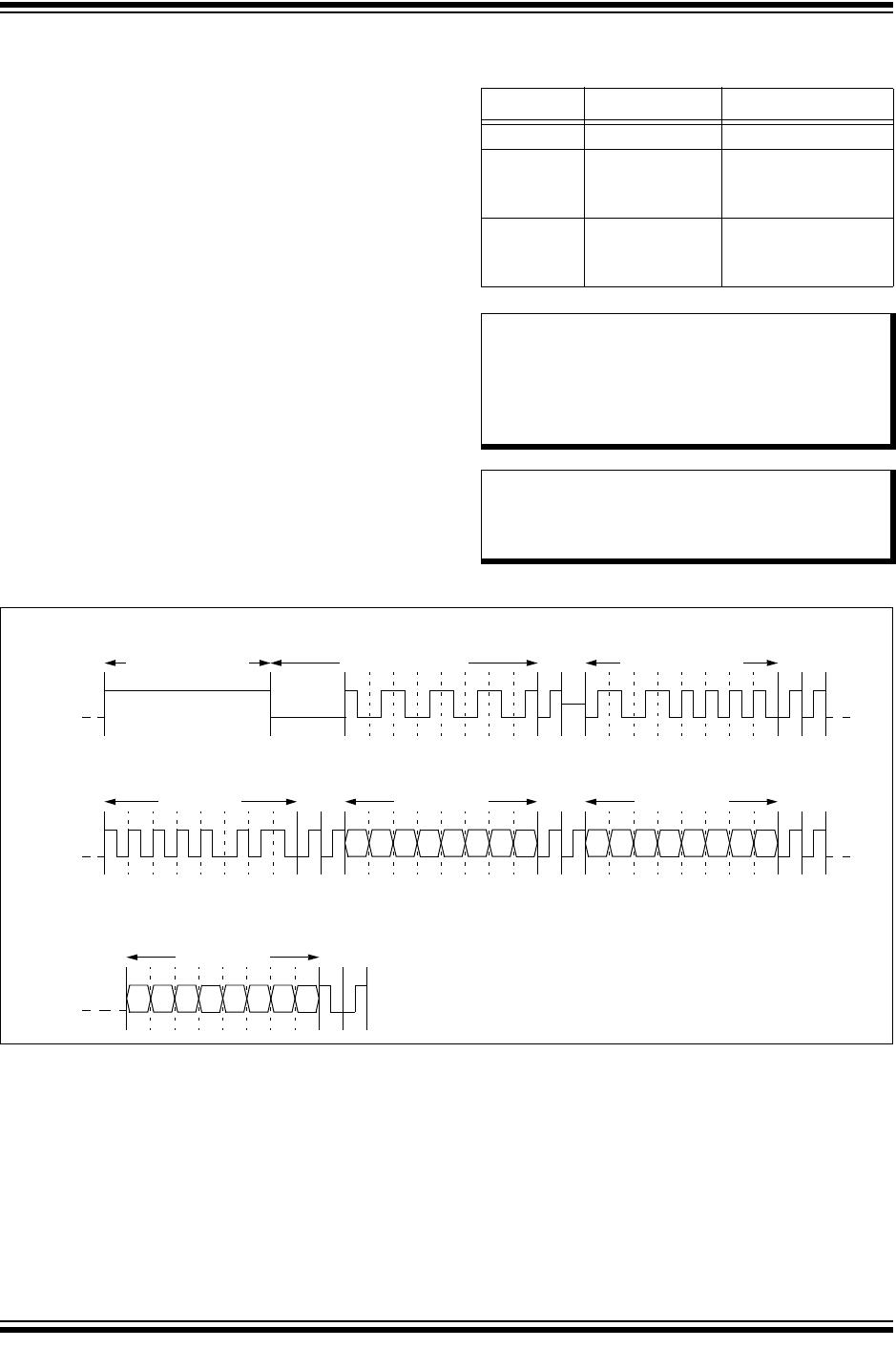

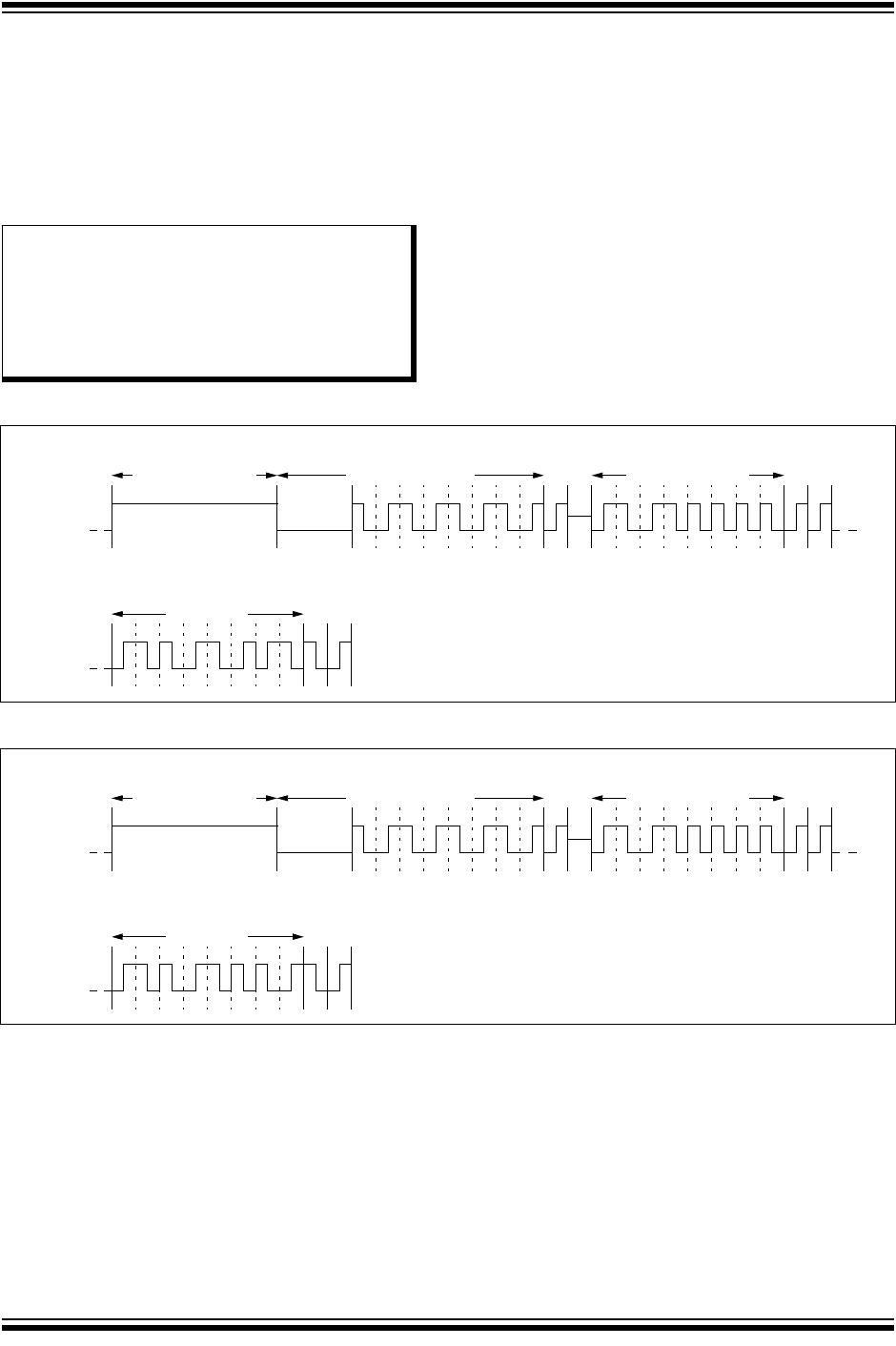

FIGURE 4-3: WRITE COMMAND SEQUENCE

Note: If a NoMAK is generated before any data

has been provided, or if a standby pulse

occurs before the NoMAK is generated,

the 11AA02EXX will be reset, and the

write cycle will not be initiated.

Note: Page write operations are limited to

writing bytes within a single physical page,

regardless of the number of bytes

actually being written. Physical page

boundaries start at addresses that are

integer multiples of the page size

(16 bytes) and end at addresses that are

integer multiples of the page size minus 1.

As an example, the page that begins at

address 0x30 ends at address 0x3F. If a

page Write command attempts to write

across a physical page boundary, the

result is that the data wraps around to the

beginning of the current page (overwriting

data previously stored there), instead of

being written to the next page as might be

expected. It is therefore necessary for the

application software to prevent page write

operations that would attempt to cross a

page boundary.

7654

Data Byte 1

3210

7654

Data Byte 2

3210

7654

Data Byte n

3210

SCIO

MAK

MAK

No MAK

11010100

Start Header

SCIO

Device Address

MAK

00001010

MAK

Command

10101100

MAK

NoSAK

SAK

Standby Pulse

SCIO

SAK

15 14 13 12

Word Address MSB

11 10 9 8

MAK

SAK

7654

Word Address LSB

3210

MAK

SAK

SAK

SAK

SAK

Twc