2008-2016 Microchip Technology Inc. DS20002122D-page 15

11AA02E48/11AA02E64

4.7 Erase All (ERAL) Instruction

The ERAL instruction allows the user to write ‘0x00’ to

the entire memory array with one command. Note that

the write enable latch (WEL) must first be set by issuing

the WREN instruction.

Once the write enable latch is set, the user may

proceed with issuing a ERAL instruction (including the

header and device address bytes). Immediately after

the NoMAK bit has been transmitted by the master, the

internal write cycle is initiated, during which time all

words of the memory array are written to ‘0x00’.

The ERAL instruction is ignored if either of the Block

Protect bits (BP0, BP1) are not 0, meaning 1/4, 1/2 or

all of the array is protected.

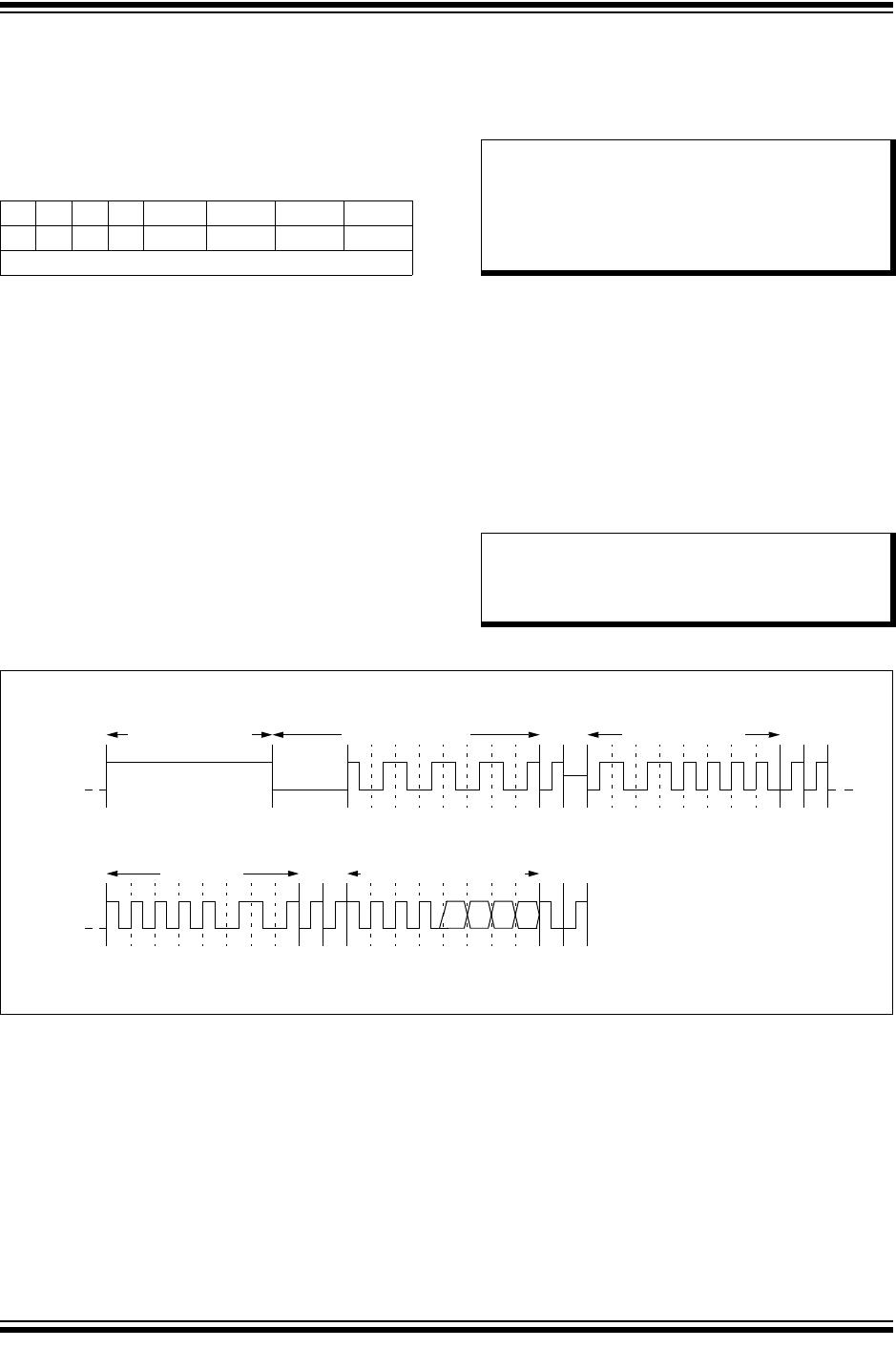

FIGURE 4-8: ERASE ALL COMMAND SEQUENCE

4.8 Set All (SETAL) Instruction

The SETAL instruction allows the user to write ‘0xFF’ to

the entire memory array with one command. Note that

the write enable latch (WEL) must first be set by issuing

the WREN instruction.

Once the write enable latch is set, the user may

proceed with issuing a SETAL instruction (including the

header and device address bytes). Immediately after

the NoMAK bit has been transmitted by the master, the

internal write cycle is initiated, during which time all

words of the memory array are written to ‘0xFF’.

The SETAL instruction is ignored if either of the Block

Protect bits (BP0, BP1) is not ‘0’, meaning 1/4, 1/2 or

all of the array is protected.

FIGURE 4-9: SET ALL COMMAND SEQUENCE

Note: The ERAL instruction must be terminated

with a NoMAK following the command

byte. If a NoMAK is not received at this

point, the command will be considered

invalid, and the device will go into Idle

mode without responding with a SAK or

executing the command.

11010100

Start Header

SCIO

Device Address

MAK

00001010

MAK

Command

11101100

NoMAK

NoSAK

SAK

Standby Pulse

SCIO

SAK

Twc

Note: The SETAL instruction must be terminated

with a NoMAK following the command

byte. If a NoMAK is not received at this

point, the command will be considered

invalid, and the device will go into Idle

mode without responding with a SAK or

executing the command.

11010100

Start Header

SCIO

Device Address

MAK

00001010

MAK

Command

11001101

NoMAK

NoSAK

SAK

Standby Pulse

SCIO

SAK

Twc