13

425112fd

LTC4251/LTC4251-1/

LTC4251-2

For more information www.linear.com/4251

SENSE

The SENSE pin is monitored by the circuit breaker (CB)

comparator, the analog current limit (ACL) amplifier, and

the fast current limit (FCL) comparator. Each of these

three measures the potential of SENSE relative to V

EE

. If

SENSE exceeds 50mV, the CB comparator activates the

230µA TIMER pull-up. At 100mV, the ACL amplifier servos

the MOSFET current, and at 200mV the FCL compara-

tor abruptly pulls GATE low in an attempt to bring the

MOSFET current under control. If any of these conditions

persists long enough for TIMER to charge C

T

to 4V (see

Equation(2)), the LTC4251/LTC4251-1/LTC4251-2 latch

off and pull GATE low.

If the SENSE pin encounters a voltage greater than 100mV,

the ACL amplifier will servo GATE downwards in an attempt

to control the MOSFET current. Since GATE overdrives the

MOSFET in normal operation, the ACL amplifier needs time

to discharge GATE to the threshold of the MOSFET. For a

mild overload, the ACL amplifier can control the MOSFET

current, but in the event of a severe overload the current

may overshoot. At SENSE = 200mV, the FCL comparator

takes over, quickly discharging the GATE pin to near V

EE

potential. FCL then releases, and the ACL amplifier takes

over. All the while TIMER is running. The effect of FCL is

to add a nonlinear response to the control loop in favor

of reducing MOSFET current.

Owing to inductive effects in the system, FCL typically

overcorrects the current limit loop, and GATE undershoots.

A zero in the loop (resistor R

C

in series with the gate

capacitor) helps the ACL amplifier recover.

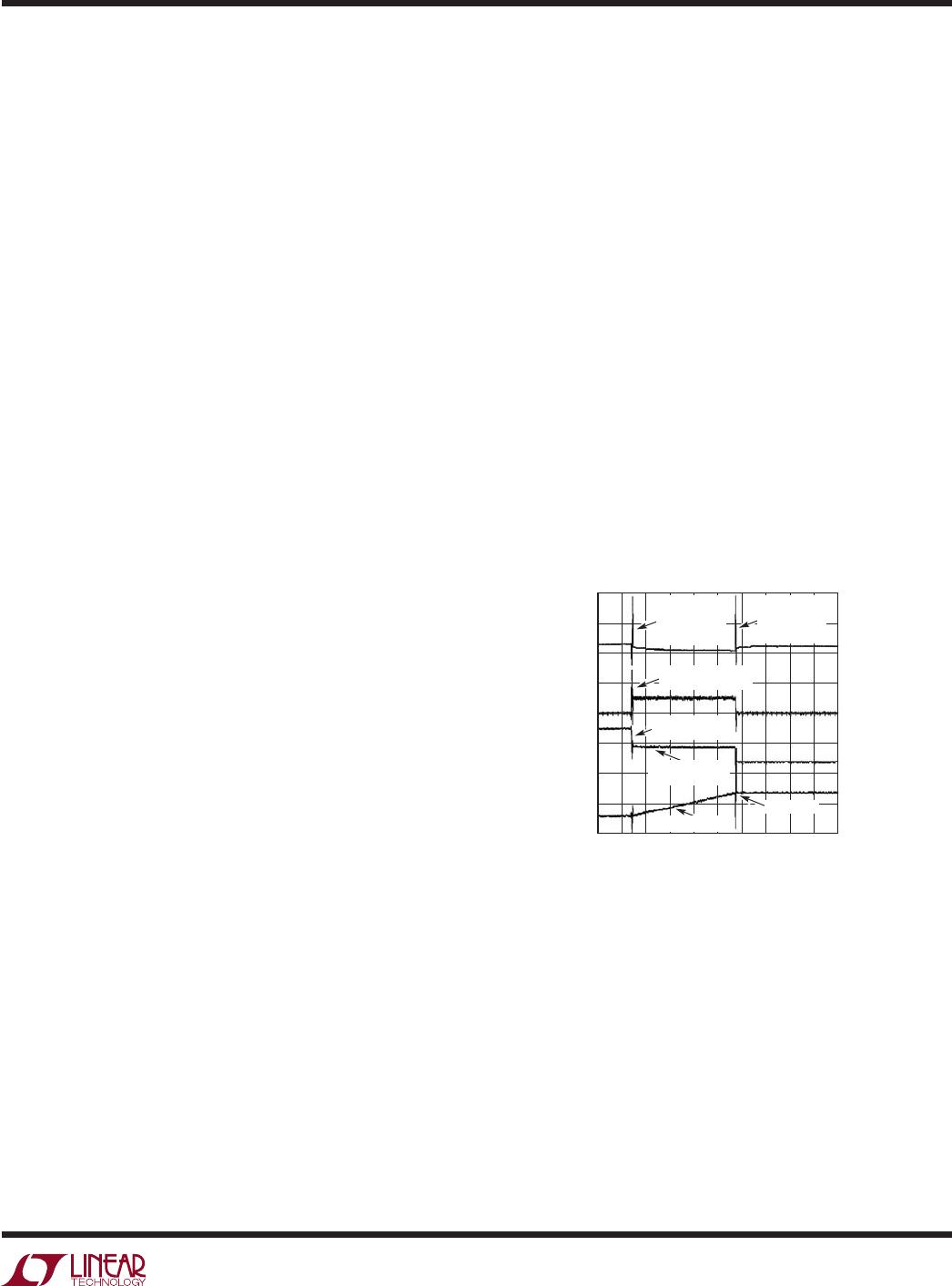

SHORT-CIRCUIT OPERATION

Circuit behavior arising from a load-side low impedance

short is shown in Figure 4. Initially, the current overshoots

the analog current limit level of V

SENSE

= 100mV (Trace 2)

as the GATE pin works to bring V

GS

under control (Trace3).

The overshoot glitches the backplane in the negative

direction, and when the current is reduced to 100mV/R

S

the backplane responds by glitching in the positive

direction.

TIMER commences charging C

T

(Trace 4) while the

analog current limit loop maintains the fault current at

100mV/R

S

, which in this case is 5A (Trace 2). Note that

the backplane voltage (Trace 1) sags under load. When C

T

reaches 4V,

GATE turns off, the load current drops to zero

and the backplane rings up to over 100V. The positive peak

is usually limited by avalanche breakdown in the MOSFET,

and can be further limited by adding a transient voltage

suppressor across the input from – 48V to –48RTN, such

as Diodes Inc. SMAT70A.

A low impedance short on one card may influence the

behavior of others sharing the same backplane. The initial

glitch and backplane sag as seen in Figure 4, Trace 1, can

rob charge from output capacitors on adjacent cards. When

the faulty card shuts down, current flows in to refresh the

capacitors. If LTC4251, LTC4251-1 or

LTC4251-2s

are used

throughout, they respond by limiting the inrush current to

a value of 100mV/R

S

. If C

T

is sized correctly, the capacitors

will recharge long before C

T

times out.

APPLICATIONS INFORMATION

MOSFET SELECTION

The external MOSFET switch must have adequate safe

operating area (SOA) to charge the load capacitance on

start-up and handle short-circuit conditions until TIMER

latchoff. These considerations take precedence over DC

current ratings. A MOSFET with adequate SOA for a given

application can always handle the required current, but

the opposite cannot be said. Consult the manufacturer’s

MOSFET data sheet for safe operating area and effective

transient thermal impedance curves.

Figure 4. Output Short-Circuit Behavior

(All Waveforms are Referenced to V

EE)

GATE

10V/DIV

SENSE

200mV/DIV

–48RTN

50V/DIV

TIMER

5V/DIV

425112 F04

SUPPLY RING

OWING

TO CURRENT

OVERSHOOT

SUPPLY RING

OWING TO

MOSFET

TURN-OFF

ONSET OF OUTPUT

SHORT-CIRCUIT

FAST CURRENT

LIMIT

ANALOG

CURRENT LIMIT

C

TIMER

RAMP

LATCH OFF

TRACE 1

TRACE 2

TRACE 3

TRACE 4

2ms/DIV