Comparator

The common-mode input range extends from 150mV

below the negative rail to within 1.1V of the positive rail.

The bipolar differential inputs of the comparator feature

high input impedance and low input bias currents. The

comparators are designed to maintain low offset volt-

age over the entire operating-temperature, common-

mode, and supply-voltage ranges. In the MAX9000/

MAX9003, the comparator’s inverting input is internally

connected to the reference output.

The CMOS output stage achieves true rail-to-rail opera-

tion; the outputs swing to within a few millivolts of the

supply rails. The comparator’s propagation delay is

185ns and is a function of the overdrive (see

Typical

Operating Characteristics

). TTL/CMOS compatibility is

maintained even with a ±4mA output load. A propri-

etary design of the output stage substantially reduces

the cross-conduction current during output transitions,

thereby minimizing power-supply glitches typical of

most comparators. In addition, the comparator’s ±2mV

of built-in hysteresis provides noise immunity and pre-

vents unstable outputs even with slow-moving input

signals.

Voltage Reference

The 1%-accurate, precision 1.230V internal bandgap

reference in the MAX9000/MAX9001/MAX9003/

MAX9004 achieves an 8ppm/°C temperature coefficient

(tempco). The reference can sink or source 1mA of load

current with excellent load regulation. The output typical-

ly changes only 60µV for a 3V change in input voltage

(line regulation). The reference is stable for capacitive

loads up to 100nF.

Applications Information

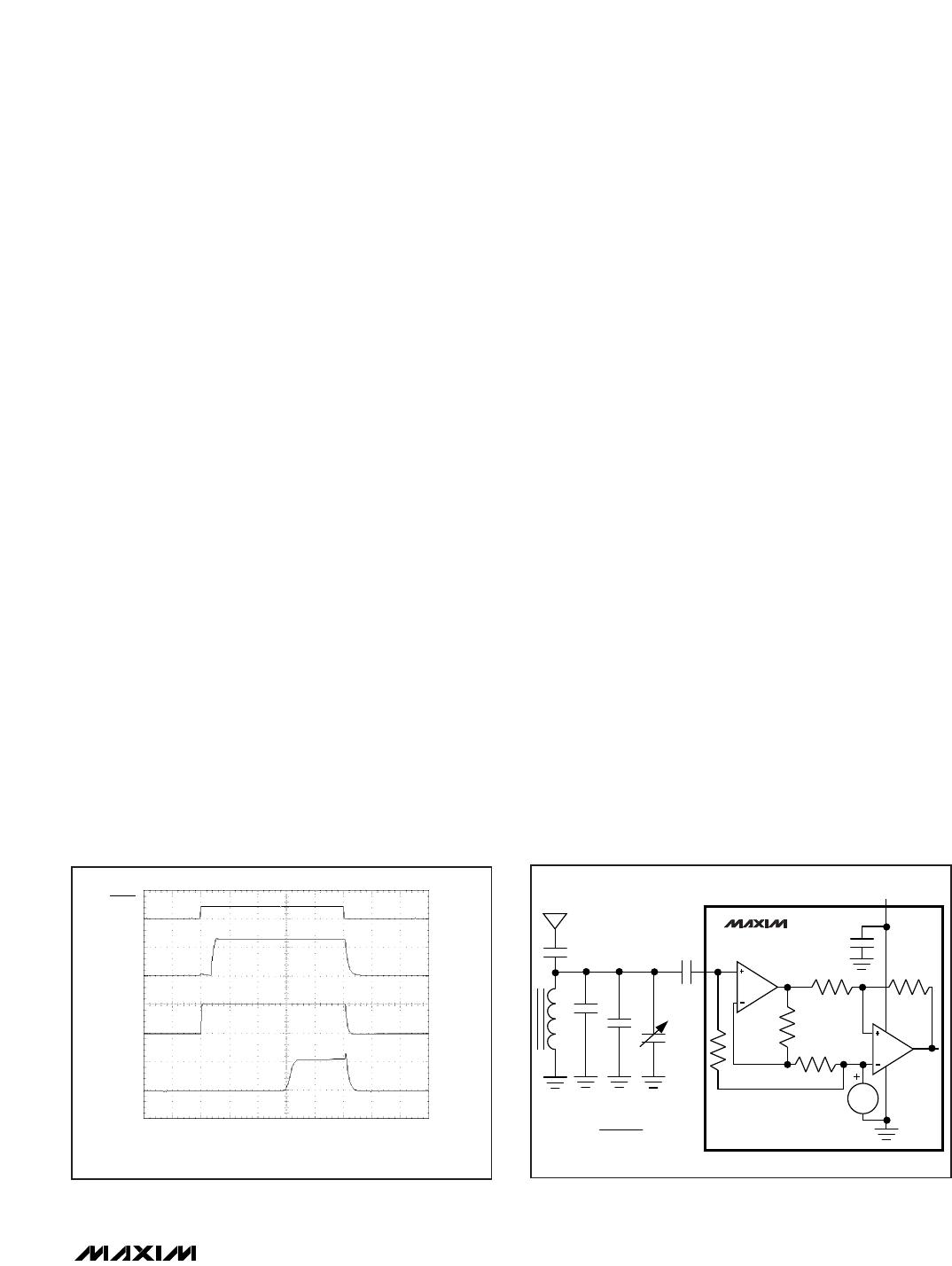

The MAX9000–MAX9005 offer excellent performance

and low power consumption, and are available in

space-saving µMAX packages. The following section

provides some practical application guidelines.

Bypassing and Layout

The MAX9000–MAX9005 operate from a +2.5V to +5.5V

single supply or from ±1.25V to ±2.75V dual supplies.

(In the MAX9000/MAX9001/MAX9003/MAX9004, the

reference voltage is referred to as V

SS

.). For single-

supply operation, bypass the power supply with a

0.1µF capacitor. For dual supplies, bypass each supply

to ground. Bypass with capacitors as close as possible

to the device to minimize lead inductance and noise.

Use a low-inductance ground plane if possible. A print-

ed circuit board with a ground plane is recommended.

Avoid using wire-wrap boards, breadboards, or IC

sockets. For heavy loads at the comparator’s and/or

amplifier’s output, add a 1µF to 10µF power-supply

bypass capacitor.

The device has a high degree of isolation between the

various blocks. To maintain isolation, careful layout is

required. Take special precautions to avoid crossing

signal traces, especially from the outputs to the inputs.

For sensitive applications, shielding might be required.

In addition, stray capacitance may affect the stability

and frequency response of the amplifier. Decrease

stray capacitance by minimizing lead lengths in the

board layout, as well as placing external components

as close to the device as possible.

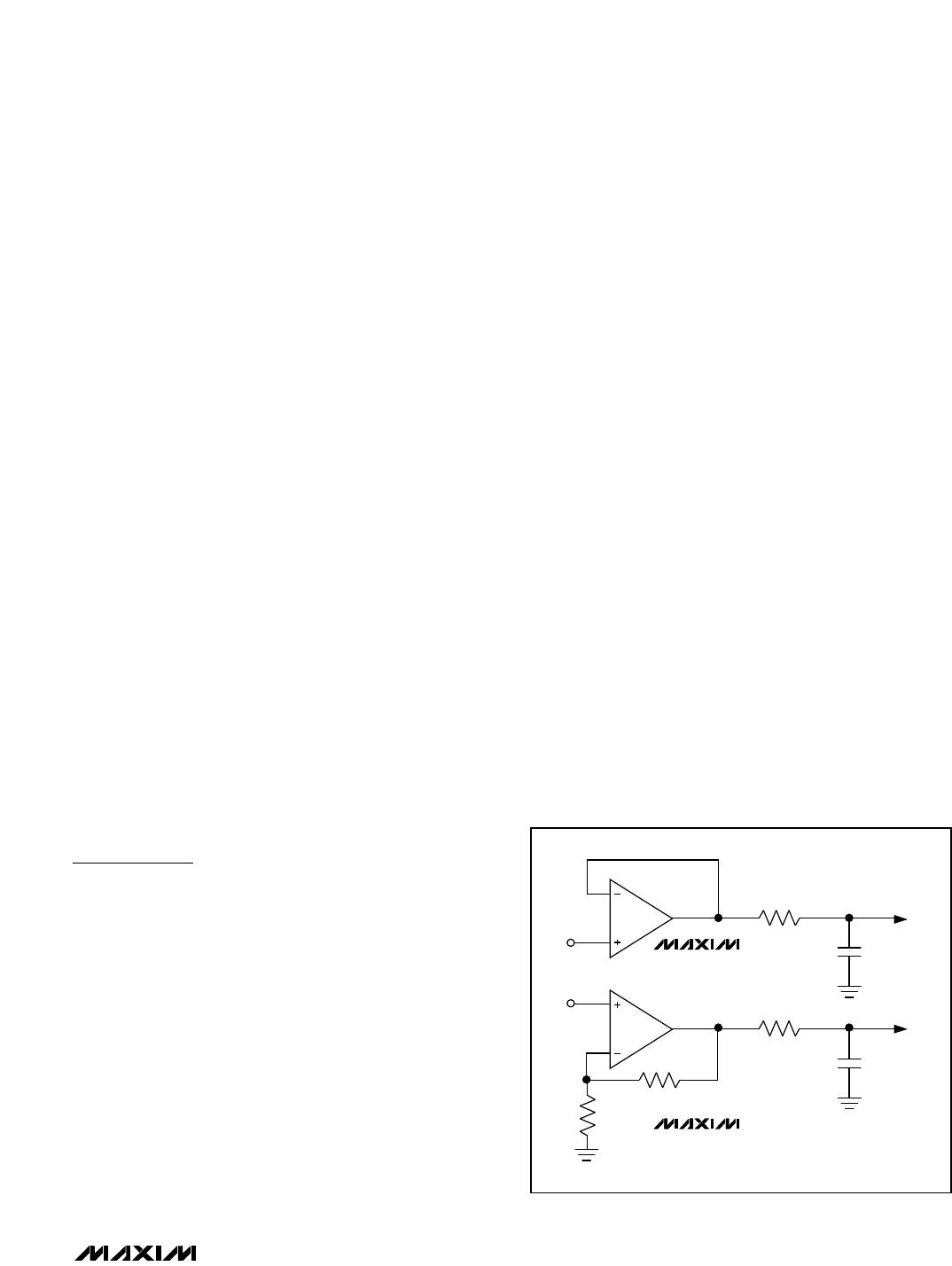

Op-Amp Frequency Stability

Driving large capacitive loads can cause instability in

most low-power, rail-to-rail output amplifiers. These

amplifiers are stable with capacitive loads up to 250pF in

their minimum gain configuration. Stability with higher

capacitive loads can be improved by adding an isolation

resistor in series with the op-amp output, as shown in

Figure 2. This resistor improves the circuit’s phase mar-

gin by isolating the load capacitor from the amplifier’s

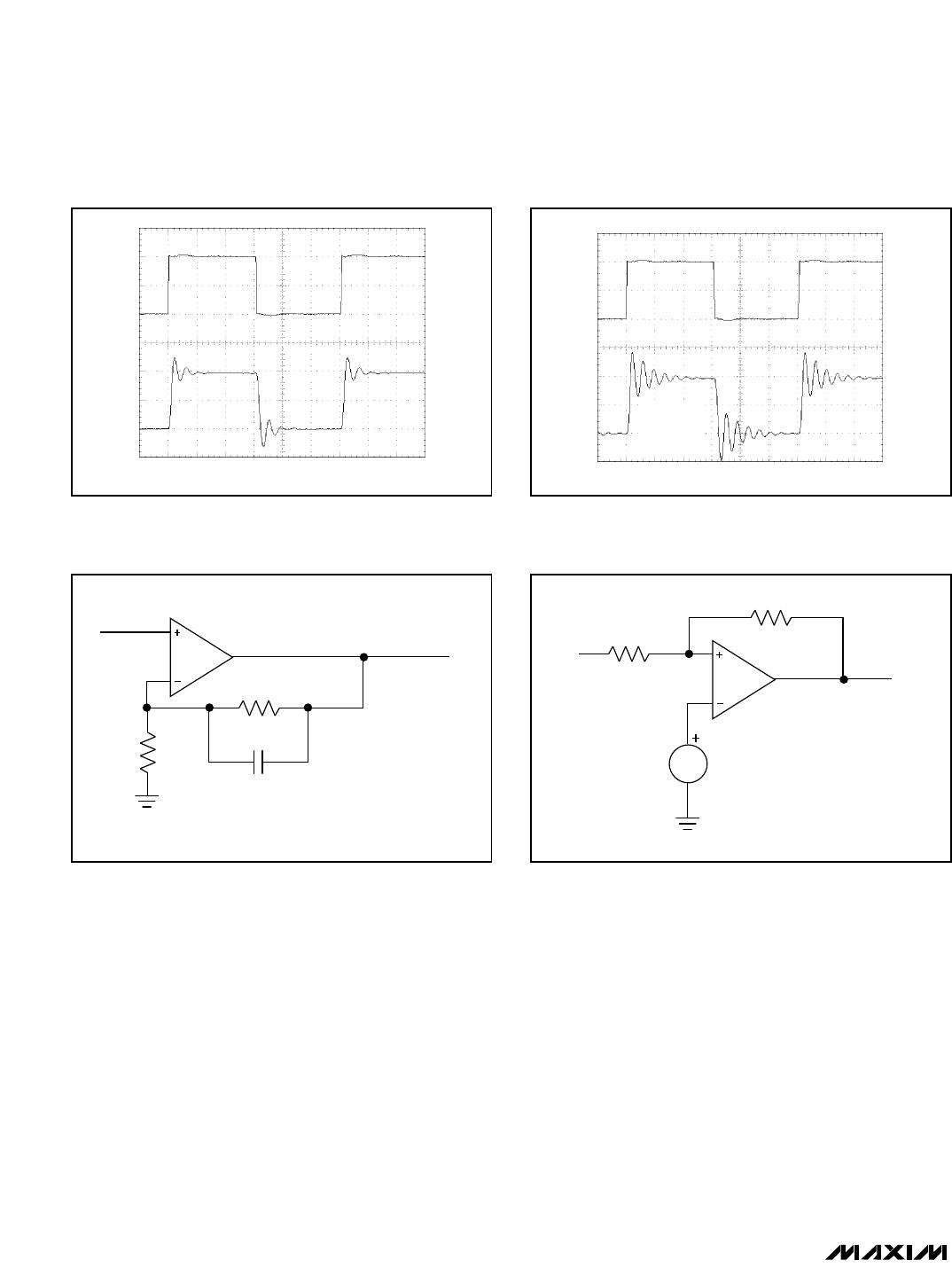

output. Figures 3 and 4 show the response of the ampli-

fier with and without an isolation resistor, respectively.

The total capacitance at the op amp’s inputs (input

capacitance + stray capacitance) along with large-value

feedback resistors can cause additional poles within the

amplifier’s bandwidth, thus degrading the phase margin.

To compensate for this effect, place a 2pF to 10pF

capacitor across the feedback resistor, as shown in

Figure 5.

MAX9000–MAX9005

Low-Power, High-Speed, Single-Supply

Op Amp + Comparator + Reference ICs

______________________________________________________________________________________ 13