3

LT1394

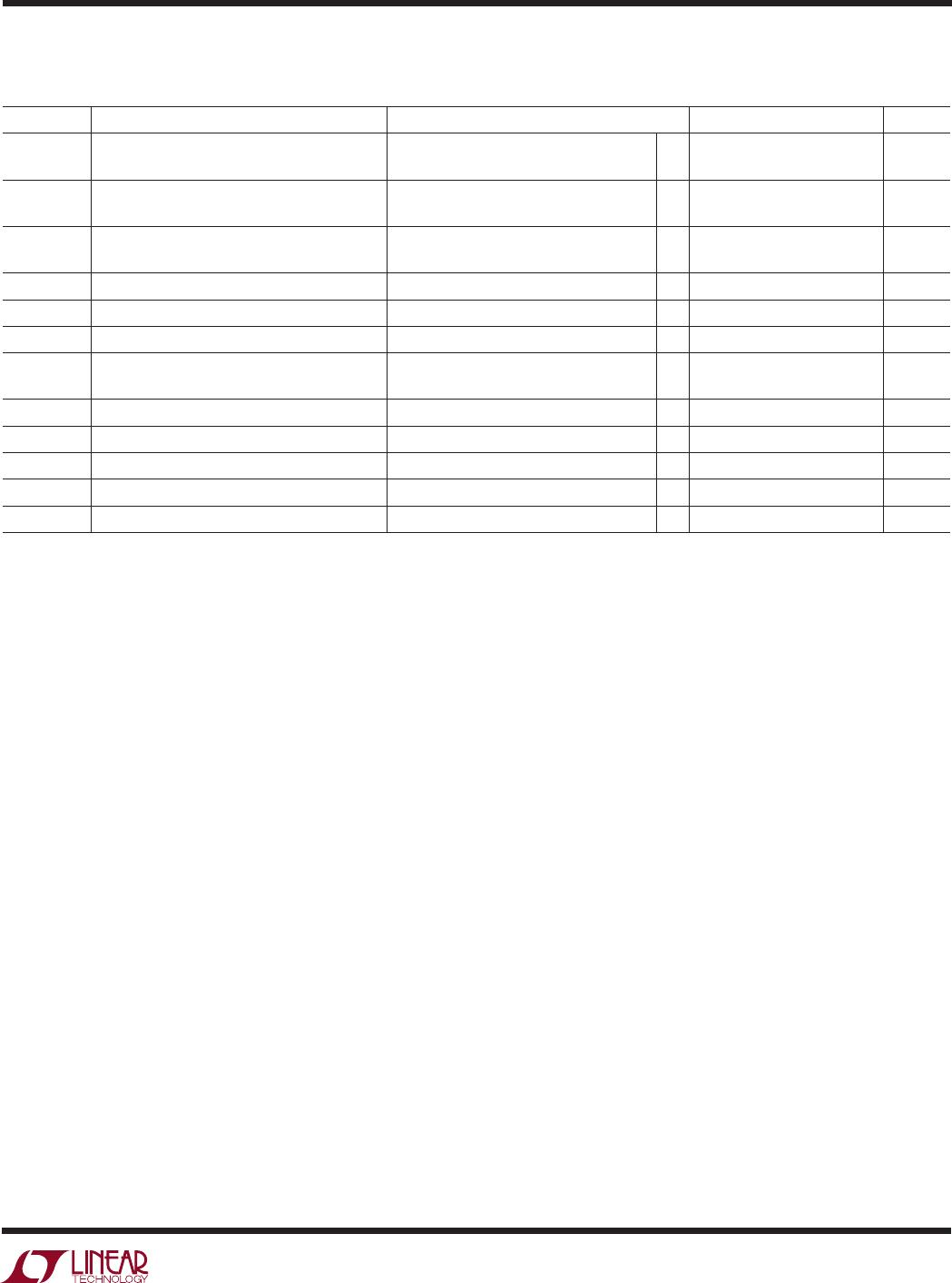

ELECTRICAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OL

Output Voltage Swing Low I

OUT

= –4mA ● 0.3 0.5 V

I

OUT

= –10mA 0.4 V

I

+

Positive Supply Current 6 8.5 mA

● 10.0 mA

I

–

Negative Supply Current 1.2 2.2 mA

● 2.5 mA

V

IH

LATCH Pin High Input Voltage ● 2V

V

IL

LATCH Pin Low Input Voltage ● 0.8 V

I

IL

LATCH Pin Current V

LATCH

= 0V ● –4 –10 µA

t

PD

Propagation Delay (Note 7) ∆V

IN

= 100mV, V

OD

= 5mV 7 9 ns

● 14 ns

∆t

PD

Differential Propagation Delay (Note 7) ∆V

IN

= 100mV, V

OD

= 5mV 0.5 2.2 ns

t

LPD

Latch Propagation Delay (Note 8) 6 ns

t

SU

Latch Setup Time (Note 8) –0.4 ns

t

H

Latch Hold Time (Note 8) 2ns

t

PW(D)

Minimum Disable Pulse Width 3ns

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: This parameter is guaranteed to meet specified perforamnce

through design and characterization. It has not been tested.

Note 3: The LT1394CMS8 and LT1394CS8 are guaranteed to meet

specified performance from 0°C to 70°C and are designed, characterized

and expected to meet these extended temperature limits, but are not tested

at –40°C and 85°C. The LT1394IS8 is guaranteed to meet the extended

temperature limits.

Note 4: Input offset voltage (V

OS

) is defined as the average of the two

voltages measured by forcing first one output, then the other to 1.4V.

Note 5: Input bias current (I

B

) is defined as the average of the two input

currents.

Note 6: Input voltage range is guaranteed in part by CMRR testing and in

part by design and characterization.

Note 7: t

PD

and ∆t

PD

cannot be measured in automatic handling

equipment with low values of overdrive. The LT1394 is 100% tested with a

100mV step and 20mV overdrive. Correlation tests have shown that t

PD

and ∆t

PD

limits can be guaranteed with this test, if additional DC tests are

performed to guarantee that all internal bias conditions are correct.

Propagation delay (t

PD

) is measured with the overdrive added to the actual

V

OS

. Differential propagation delay is defined as:

∆t

PD

= t

PDLH

– t

PDHL

Note 8: Latch propagation delay (t

LPD

) is the delay time for the output to

respond when the LATCH pin is deasserted. Latch setup time (t

SU

) is the

interval in which the input signal must remain stable prior to asserting the

latch signal. Latch hold time (t

H

) is the interval after the latch is asserted in

which the input signal must remain stable.

The ● denotes specifications which apply over the full operating temperature range, otherwise specifications are T

A

= 25°C.

V

+

= 5V, V

–

= –5V, V

OUT

(Q) = 1.4V, V

LATCH

= V

CM

= 0V unless otherwise noted.