© 2006 Microchip Technology Inc. DS21204E-page 7

25AA040/25LC040/25C040

3.0 FUNCTIONAL DESCRIPTION

3.1 Principles of Operation

The 25XX040 is a 512 byte Serial EEPROM designed

to interface directly with the Serial Peripheral Interface

(SPI) port of many of today’s popular microcontroller

families, including Microchip’s PIC16C6X/7X micro-

controllers. It may also interface with microcontrollers

that do not have a built-in SPI port by using discrete

I/O lines programmed properly with the software.

The 25XX040 contains an 8-bit instruction register. The

part is accessed via the SI pin, with data being clocked

in on the rising edge of SCK. The CS

pin must be low

and the HOLD

pin must be high for the entire operation.

The WP

pin must be held high to allow writing to the

memory array.

Table 3-1 contains a list of the possible instruction

bytes and format for device operation. The Most

Significant address bit (A8) is located in the instruction

byte. All instructions, addresses, and data are

transferred MSB first, LSB last.

Data is sampled on the first rising edge of SCK after CS

goes low. If the clock line is shared with other periph-

eral devices on the SPI bus, the user can assert the

HOLD input and place the 25XX040 in ‘HOLD’ mode.

After releasing the HOLD

pin, operation will resume

from the point when the HOLD

was asserted.

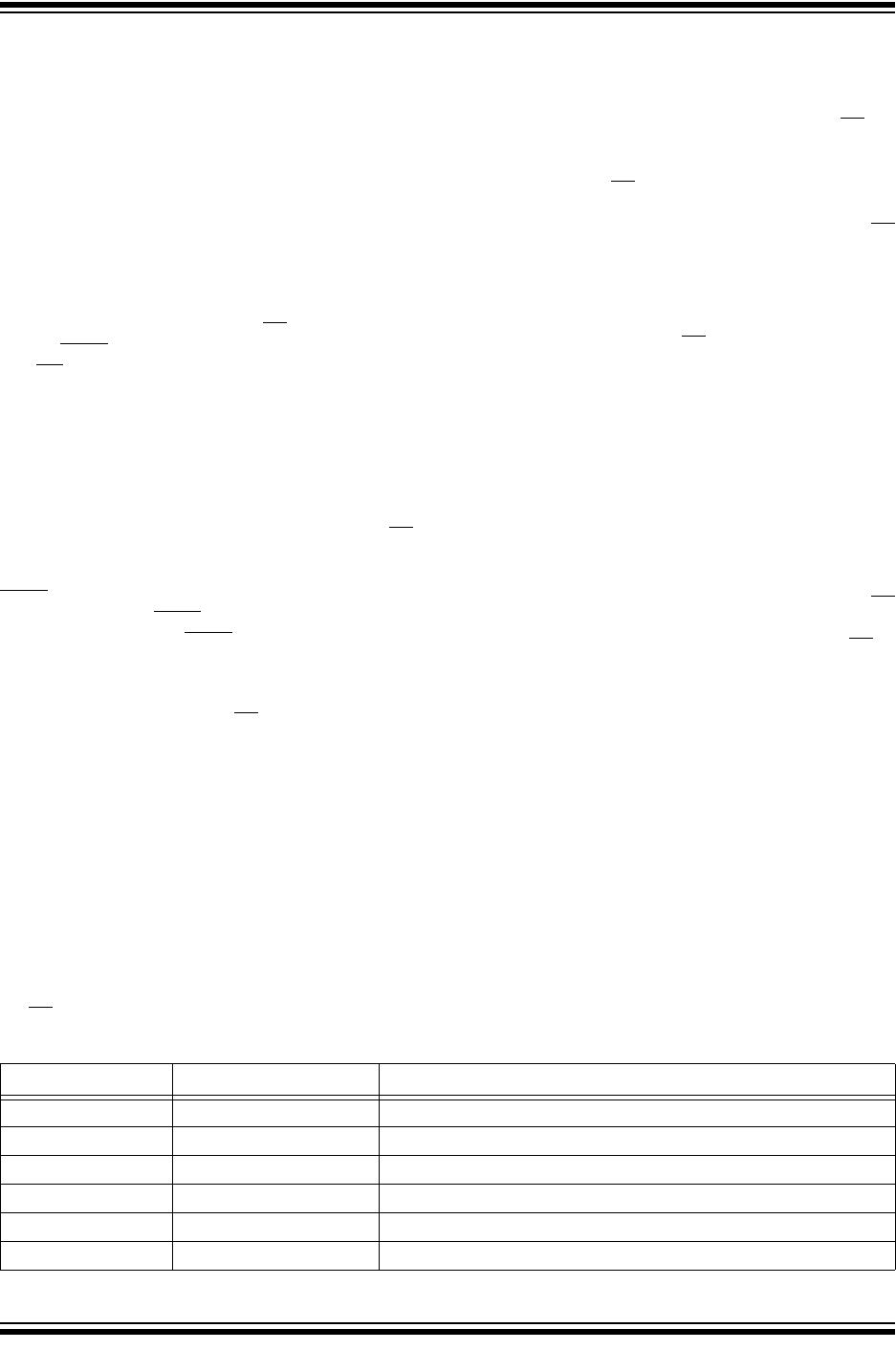

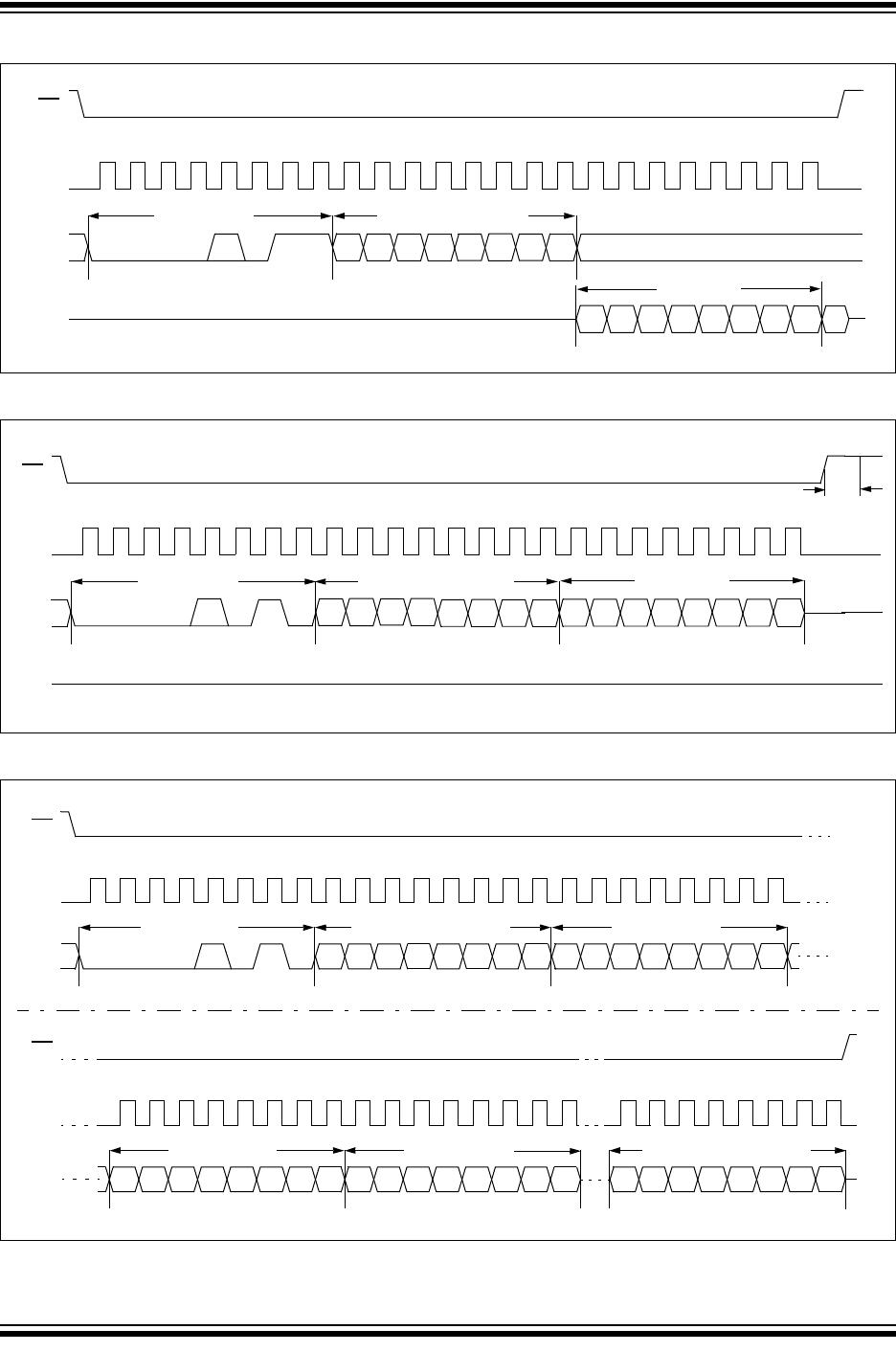

3.2 Read Sequence

The part is selected by pulling CS low. The 8-bit READ

instruction with the A8 address bit is transmitted to the

25XX040 followed by the lower 8-bit address (A7

through A0). After the correct READ instruction and

address are sent, the data stored in the memory at the

selected address is shifted out on the SO pin. The data

stored in the memory at the next address can be read

sequentially by continuing to provide clock pulses. The

internal Address Pointer is automatically incremented

to the next higher address after each byte of data is

shifted out. When the highest address is reached

(01FFh), the address counter rolls over to address

0000h allowing the read cycle to be continued

indefinitely. The read operation is terminated by raising

the CS

pin (Figure 3-1).

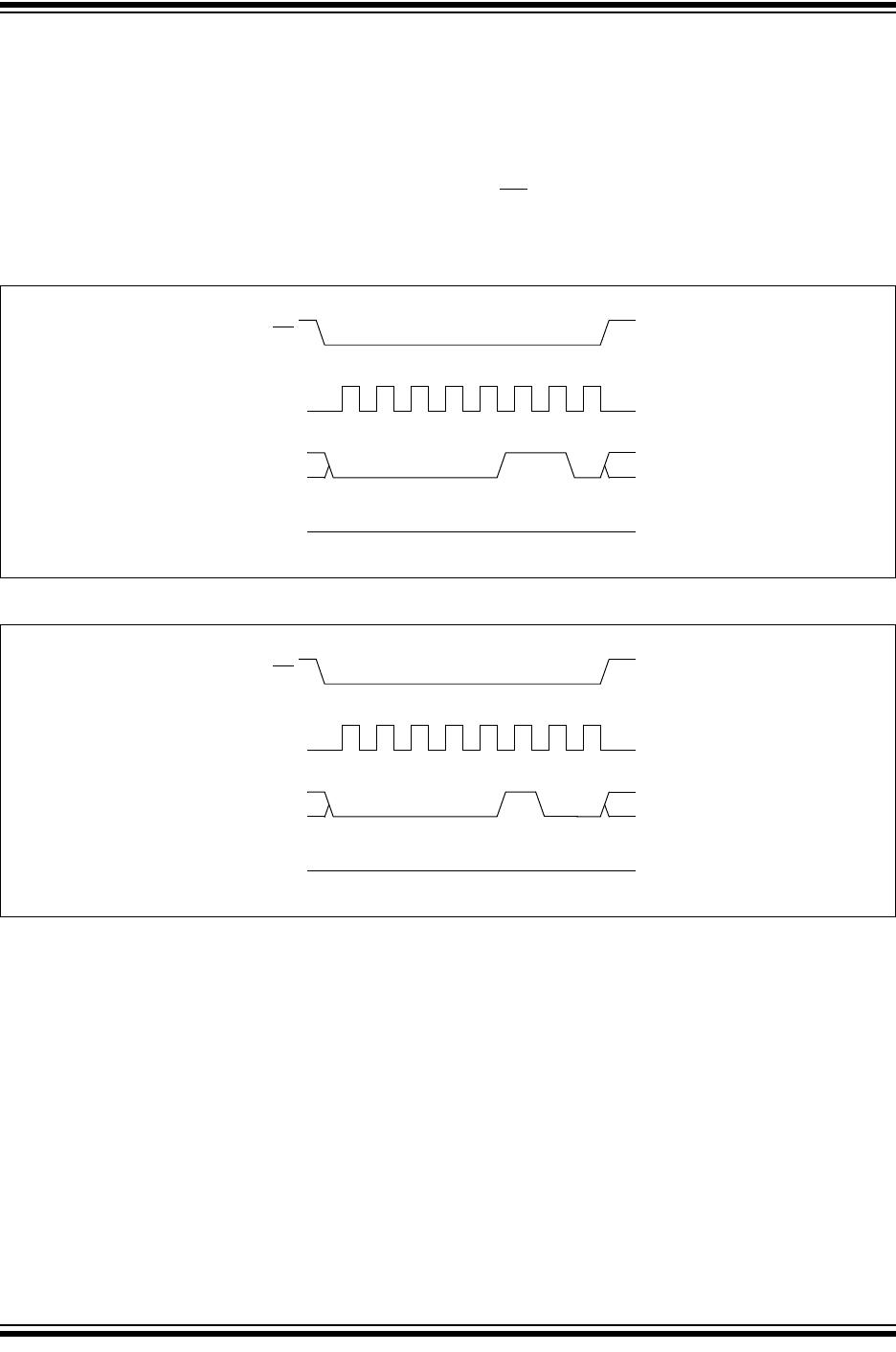

3.3 Write Sequence

Prior to any attempt to write data to the 25XX040, the

write enable latch must be set by issuing the WREN

instruction (Figure 3-4). This is done by setting CS

low

and then clocking out the proper instruction into the

25XX040. After all eight bits of the instruction are

transmitted, the CS

must be brought high to set the

write enable latch. If the write operation is initiated

immediately after the WREN instruction without CS

being brought high, the data will not be written to the

array because the write enable latch will not have been

properly set.

Once the write enable latch is set, the user may

proceed by setting the CS

low, issuing a WRITE

instruction, followed by the address, and then the data

to be written. Keep in mind that the Most Significant

address bit (A8) is included in the instruction byte. Up

to 16 bytes of data can be sent to the 25XX040 before

a write cycle is necessary. The only restriction is that all

of the bytes must reside in the same page. A page

address begins with

XXXX 0000 and ends with XXXX

1111

. If the internal address counter reaches XXXX

1111

and the clock continues, the counter will roll back

to the first address of the page and overwrite any data

in the page that may have been written.

For the data to be actually written to the array, the CS

must be brought high after the least significant bit (D0)

of the n

th

data byte has been clocked in. If CS is

brought high at any other time, the write operation will

not be completed. Refer to Figure 3-2 and Figure 3-3

for more detailed illustrations on the byte write

sequence and the page write sequence respectively.

While the write is in progress, the STATUS register may

be read to check the status of the WIP, WEL, BP1 and

BP0 bits (Figure 3-6). A read attempt of a memory

array location will not be possible during a write cycle.

When the write cycle is completed, the write enable

latch is reset.

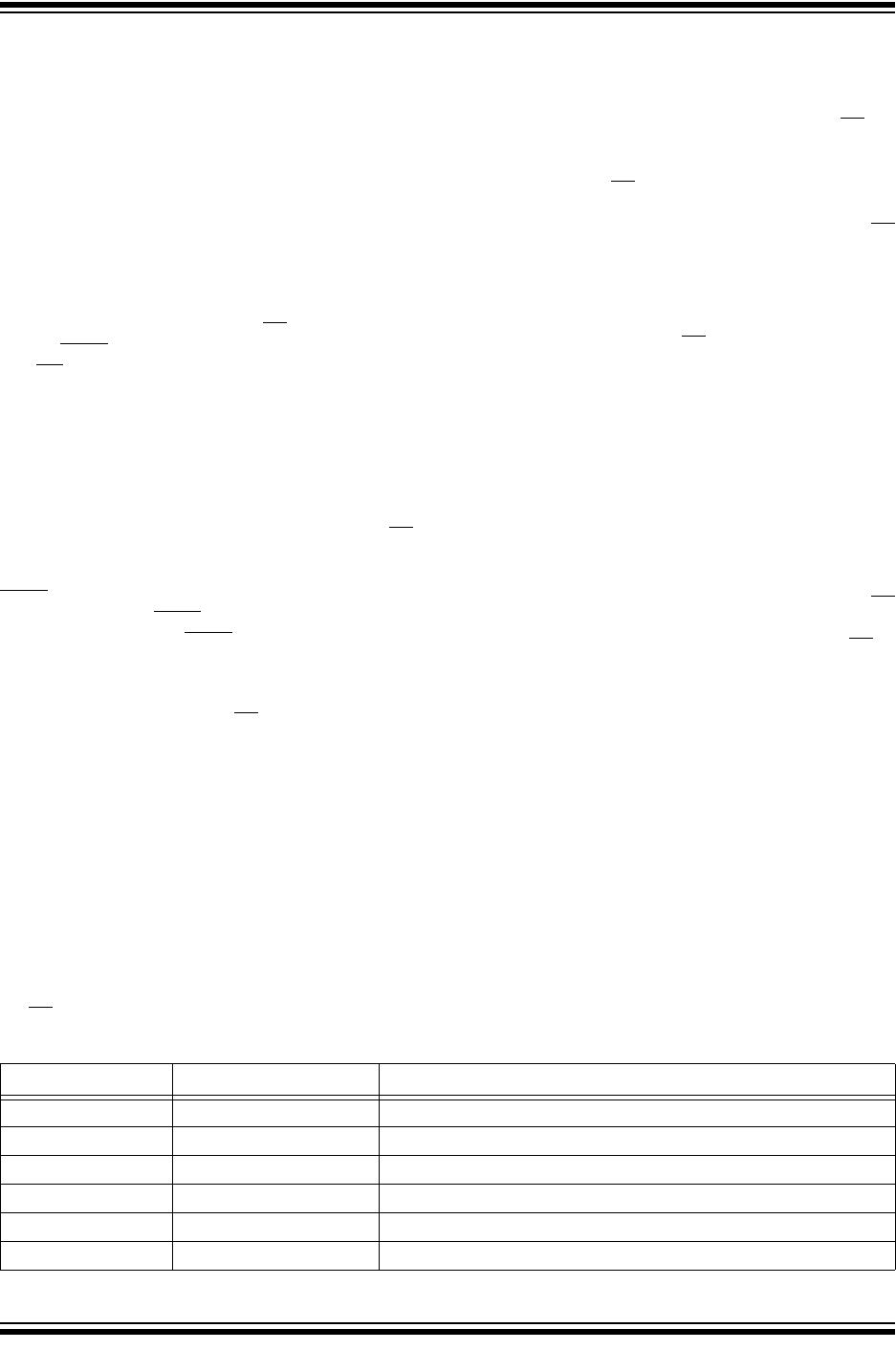

TABLE 3-1: INSTRUCTION SET

Instruction Name Instruction Format Description

READ

0000 A8011

Read data from memory array beginning at selected address

WRITE

0000 A8010

Write data to memory array beginning at selected address

WRDI

0000 0100

Reset the write enable latch (disable write operations)

WREN

0000 0110

Set the write enable latch (enable write operations)

RDSR

0000 0101

Read STATUS register

WRSR

0000 0001

Write STATUS register

Note: A

8 is the 9

th

address bit necessary to fully address 512 bytes.