For example, to choose a Butterworth filter response

with a corner frequency of 5kHz:

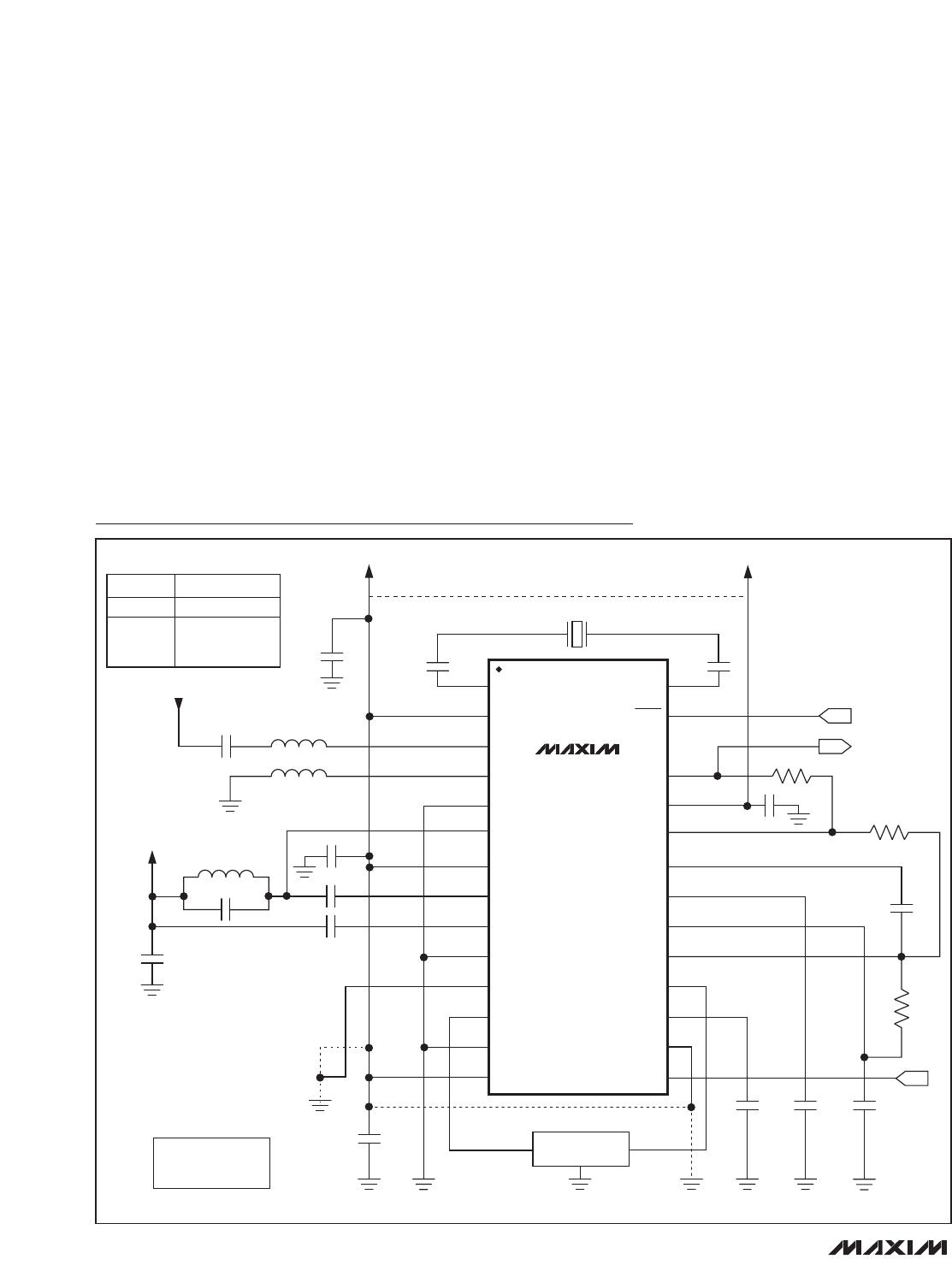

Choosing standard capacitor values changes C5 to

470pF and C6 to 220pF, as shown in the

Typical

Application Circuit

.

Data Slicer

The data slicer takes the analog output of the data filter

and converts it to a digital signal. This is achieved by

using a comparator and comparing the analog input to

a threshold voltage. One input is supplied by the data

filter output. Both comparator inputs are accessible off-

chip to allow for different methods of generating the

slicing threshold, which is applied to the second com-

parator input.

The suggested data slicer configuration uses a resistor

(R1) connected between DSN and DSP with a capaci-

tor (C4) from DSN to DGND (Figure 3). This configura-

tion averages the analog output of the filter and sets the

threshold to approximately 50% of that amplitude. With

this configuration, the threshold automatically adjusts

as the analog signal varies, minimizing the possibility

for errors in the digital data. The values of R1 and C4

affect how fast the threshold tracks to the analog ampli-

tude. Be sure to keep the corner frequency of the RC

circuit much lower than the lowest expected data rate.

Note that a long string of zeros or ones can cause the

threshold to drift. This configuration works best if a cod-

ing scheme, such as Manchester coding, which has an

equal number of zeros and ones, is used.

To prevent continuous toggling of DATAOUT in the

absence of an RF signal due to noise, add hysteresis to

the data slicer as shown in Figure 4.

Peak Detector

The peak-detector output (PDOUT), in conjunction with

an external RC filter, creates a DC output voltage equal

to the peak value of the data signal. The resistor pro-

vides a path for the capacitor to discharge, allowing the

peak detector to dynamically follow peak changes of

the data-filter output voltage. For faster data slicer

response, use the circuit shown in Figure 5.

.

..

.

.