PROGRAMMABLE CLOCK GENERATOR 12 MARCH 3, 2017

5P49V5901 DATASHEET

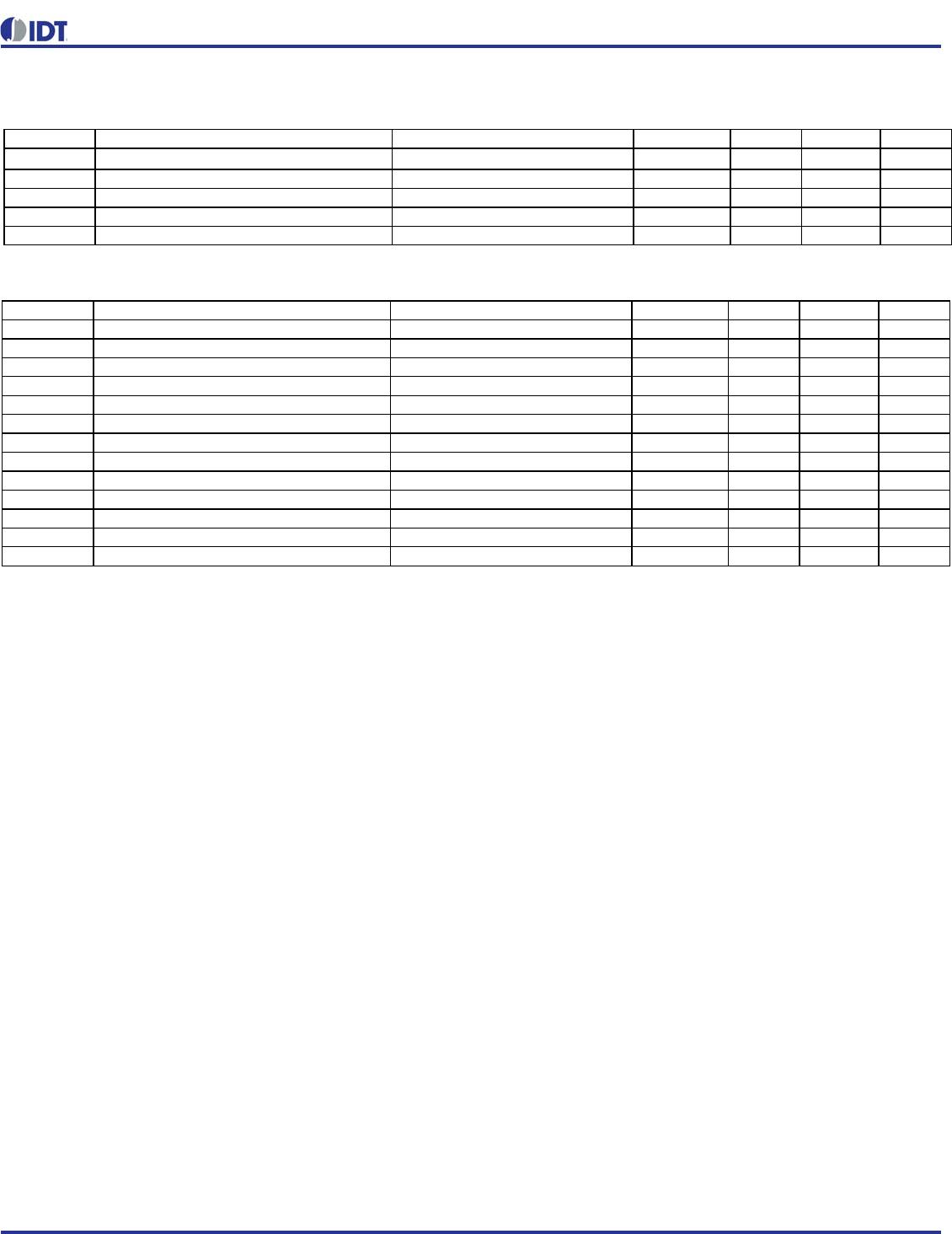

Table 8:Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the 5P49V5901. These ratings, which are standard values for IDT

commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in

the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect

product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

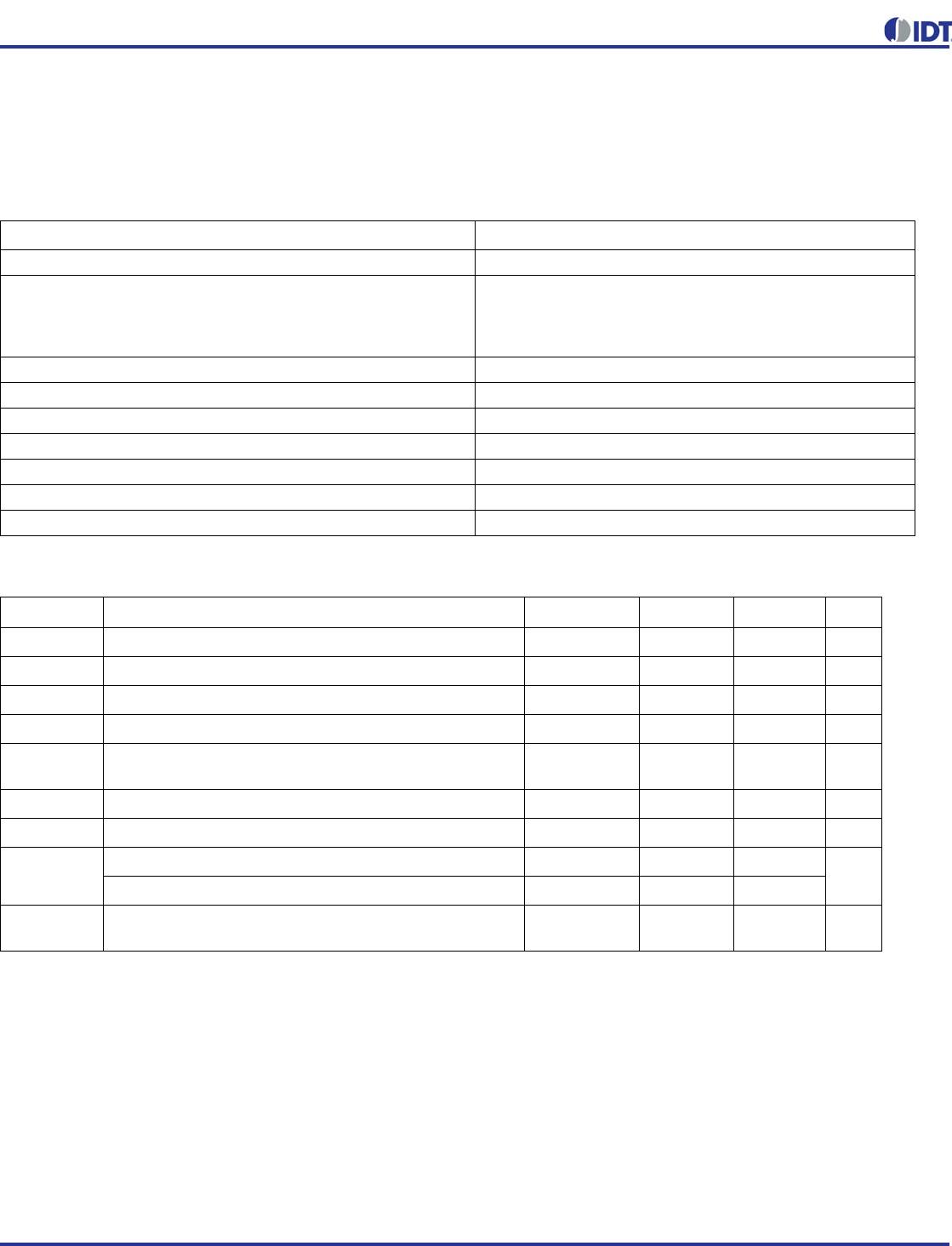

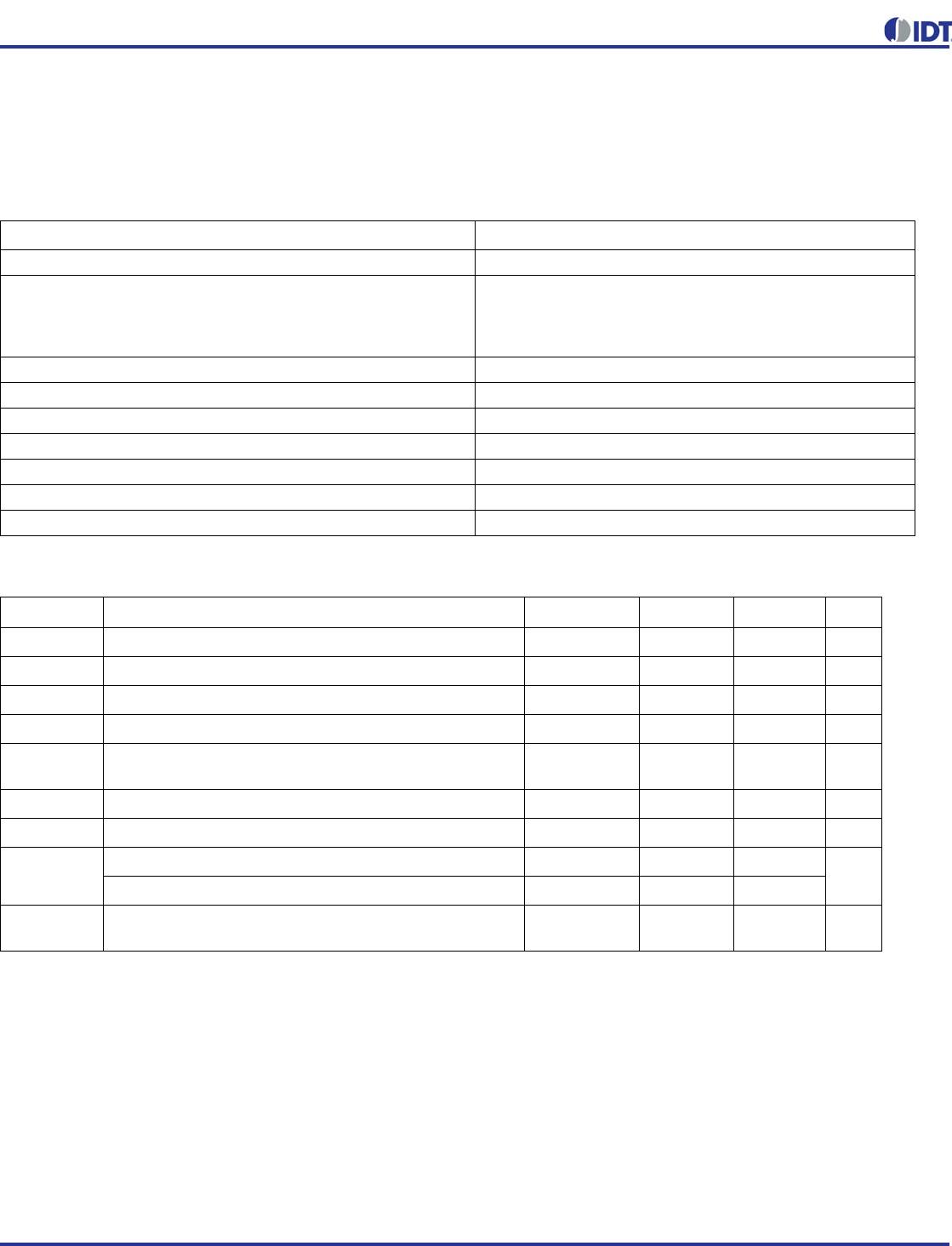

Table 9:Recommended Operation Conditions

Note: V

DDO

1, V

DDO

2, V

DDO

3, and V

DDO

4 must be powered on either before or simultaneously with V

DDD

, V

DDA

and V

DDO

0.

Item Rating

Supply Voltage, V

DDA,

V

DDD,

V

DDO

3.465V

Inputs

XIN/REF

CLKIN, CLKINB

Other inputs

0V to 1.2V voltage swing

0V to 1.2V voltage swing single-ended

-0.5V to V

DDD

Outputs, V

DDO

(LVCMOS) -0.5V to V

DDO

+ 0.5V

Outputs, I

O

(SDA) 10mA

Package Thermal Impedance,

JA

42C/W (0 mps)

Package Thermal Impedance,

JC

41.8C/W (0 mps)

Storage Temperature, T

STG

-65C to 150C

ESD Human Body Model 2000V

Junction Temperature 125°C

Symbol Parameter Min Typ Max Unit

V

DDOX

Power supply voltage for supporting 1.8V outputs

1.71 1.8 1.89 V

V

DDOX

Power supply voltage for supporting 2.5V outputs

2.375 2.5 2.625 V

V

DDOX

Power supply voltage for supporting 3.3V outputs

3.135 3.3 3.465 V

V

DDD

Power supply voltage for core logic functions

1.71 3.465 V

V

DDA

Analog power supply voltage. Use filtered analog power

supply.

1.71 3.465 V

T

A

Operating temperature, ambient

-40 +85 °C

C

LOAD_OUT

Maximum load capacitance (3.3V LVCMOS only)

15 pF

F

IN

External reference crystal

840MHz

External reference clock CLKIN, CLKINB

5350

t

PU

Power up time for all V

DD

s to reach minimum specified

voltage (power ramps must be monotonic)

0.05 5 ms