MARCH 3, 2017 13 PROGRAMMABLE CLOCK GENERATOR

5P49V5901 DATASHEET

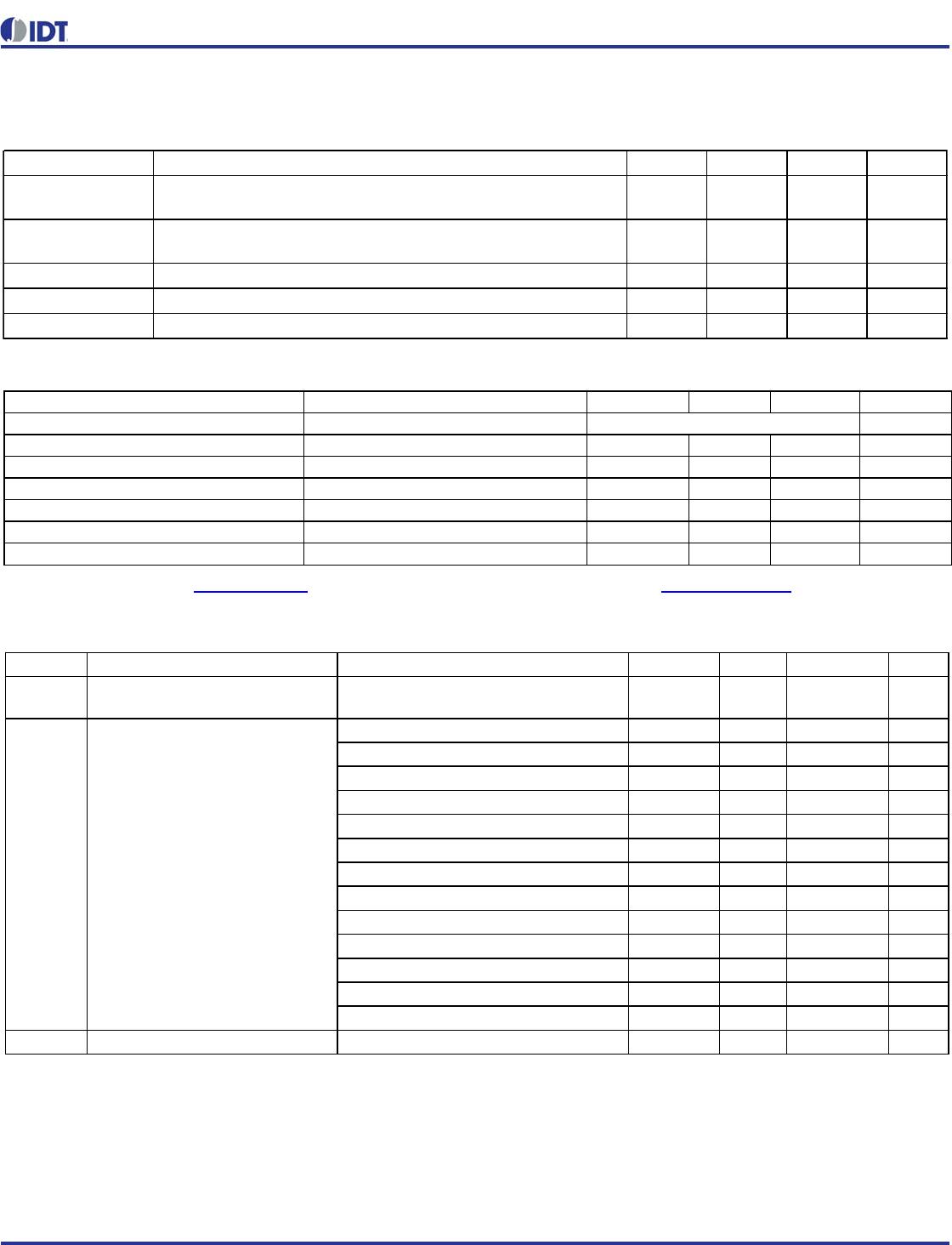

Table 10:Input Capacitance, LVCMOS Output Impedance, and Internal Pull-down

Resistance

(T

A

= +25 °C)

Table 11:Crystal Characteristics

Note: Typical crystal used is FOX 603-25-150. For different reference crystal options please go to www.foxonline.com.

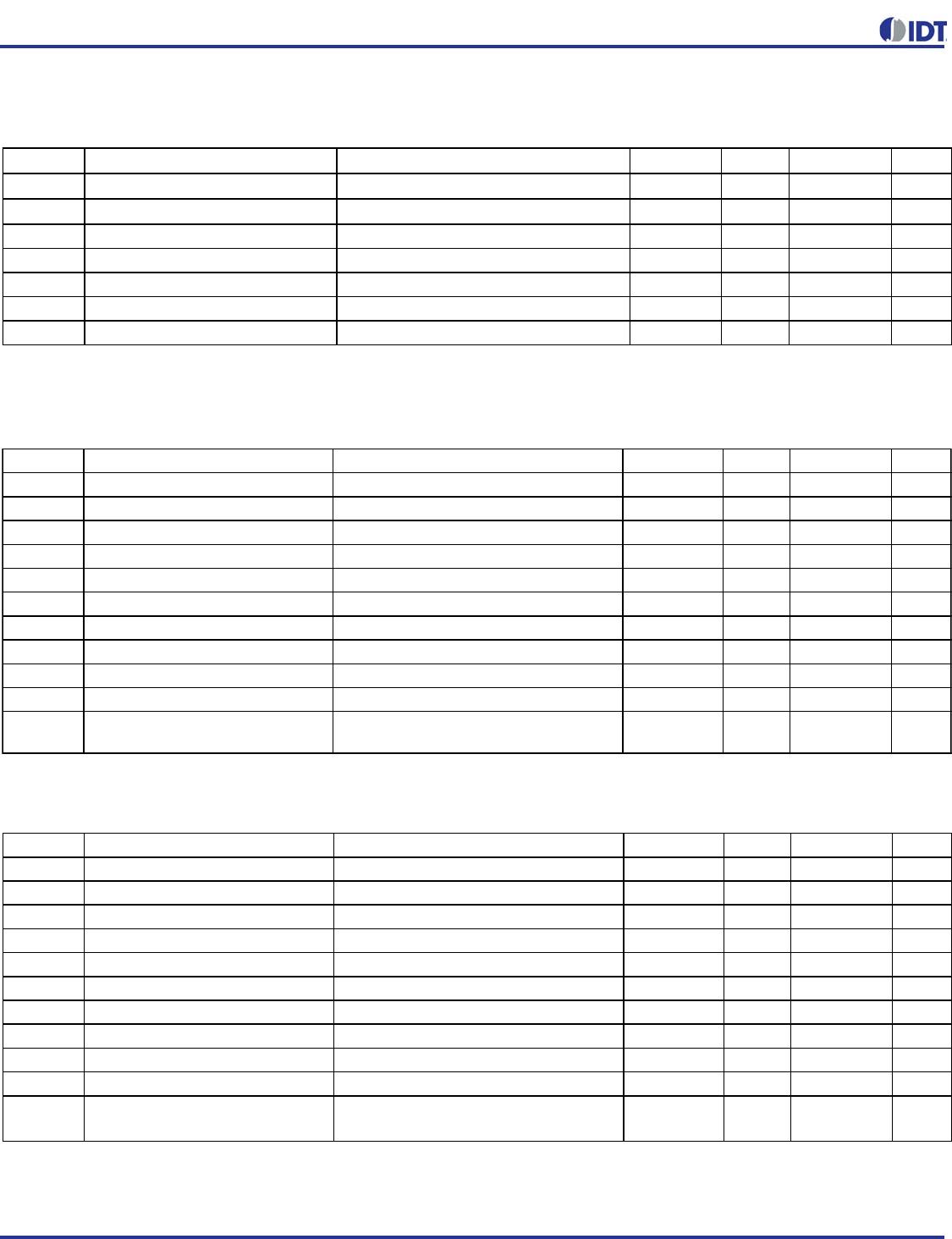

Table 12:DC Electrical Characteristics

Symbol Parameter Min Typ Max Unit

CIN

Input Capacitance (CLKIN, CLKINB, CLKSEL, SD/OE,

SEL1/SDA, SEL0/SCL)

37pF

Pull-down Resistor

CLKSEL, SD/OE, SEL1/SDA, SEL0/SCL, CLKIN, CLKINB,

OUT0_SEL_I2CB

100 300 kΩ

ROUT

LVCMOS Output Driver Impedance (VDDO = 1.8V, 2.5V, 3.3V)

17 Ω

XIN/ RE F

Programmable capacitance at XIN/REF

925pF

XOUT

Programmable capacitance at XOUT

925pF

Parameter Test Conditions Minimum Typical Maximum Units

Mode of Oscillation

Frequency 82540MHz

Equivalent Series Resistance (ESR) 10 100 Ω

Shunt Capacitance 7pF

Load Capacitance (CL) @ <=25 MHz 6 8 12 pF

Load Capacitance (CL) >25M to 40M 6 8 pF

Maximum Crystal Drive Level 100 µW

Fundamental

Symbol Parameter Test Conditions Min Typ Max Unit

Iddcore

3

Core Supply Current

100 MHz on all outputs, 25 MHz

REFCLK

30 34 mA

LVPECL, 350 MHz, 3.3V VDDOx 42 47 mA

LVPECL, 350 MHz, 2.5V VDDOx 37 42 mA

LVDS, 350 MHz, 3.3V VDDOx 18 21 mA

LVDS, 350 MHz, 2.5V VDDOx 17 20 mA

LVDS, 350 MHz, 1.8V VDDOx 16 19 mA

HCSL, 250 MHz, 3.3V VDDOx, 2 pF load 29 33 mA

HCSL, 250 MHz, 2.5V VDDOx, 2 pF load 28 33 mA

LVCMOS, 50 MHz, 3.3V, VDDOx

1,2

16 18 mA

LVCMOS, 50 MHz, 2.5V, VDDOx

1,2

14 16 mA

LVCMOS, 50 MHz, 1.8V, VDDOx

1,2

12 14 mA

LVCMOS, 200 MHz, 3.3V VDDOx

1

36 42 mA

LVCMOS, 200 MHz, 2.5V VDDOx

1,2

27 32 mA

LVCMOS, 200 MHz, 1.8V VDDOx

1,2

16 19 mA

Iddpd Power Down Current SD asserted, I2C Programming 10 14 mA

1. Single CMOS driver active.

2. Measured into a 5” 50 Ohm trace with 2 pF load.

3. Iddcore = IddA+ IddD, no loads.

Iddox Output Buffer Supply Current