NCP1582, NCP1582A, NCP1583

http://onsemi.com

6

DETAILED OPERATING DESCRIPTION

General

The NCP158x is an 8−pin PWM controller intended for

DC−DC conversion from 5.0 V & 12 V buses. The NCP158x

has a 0.7 A internal gate driver circuit designed to drive

N−channel MOSFETs in a synchronous−rectifier buck

topology. The output voltage of the converter can be

precisely regulated down to 800 mV 1.5% when the V

FB

pin

is tied to V

OUT

. The switching frequency is internally set. A

high gain operational transconductance error amplifier

(OTA) is used.

Duty Cycle and Maximum Pulse Width Limits

In steady state DC operation, the duty cycle will stabilize

at an operating point defined by the ratio of the input to the

output voltage. The NCP158x can achieve an 80% duty

cycle. There is a built in off−time which ensures that the

bootstrap supply is charged every cycle. The NCP158x,

which is capable of a 100 nsec pulse width (min.), can allow

a 12 V to 0.8 V conversion at 350 kHz.

Input Voltage Range (V

CC

and BST)

The input voltage range for both V

CC

and BST is 4.5 V to

13.2 V with respect to GND and PHASE, respectively.

Although BST is rated at 13.2 V with respect to PHASE, it

can also tolerate 26.5 V with respect to GND.

External Enable/Disable

When the Comp pin voltage falls or is pulled externally

below the 400 mv threshold, it disables the PWM Logic and

the gate drive outputs. In this disabled mode, the operational

transconductance error amplifier’s (EOTA) output source

current is reduced and limited to the Soft Start current of 10 mA.

Normal Shutdown Behavior

Normal shutdown occurs when the IC stops switching

because the input supply reaches UVLO threshold. In this

case, switching stops, the internal SS is discharged, and all

GATE pins go low. The switch node enters a high impedance

state and the output capacitors discharge through the load

with no ringing on the output voltage.

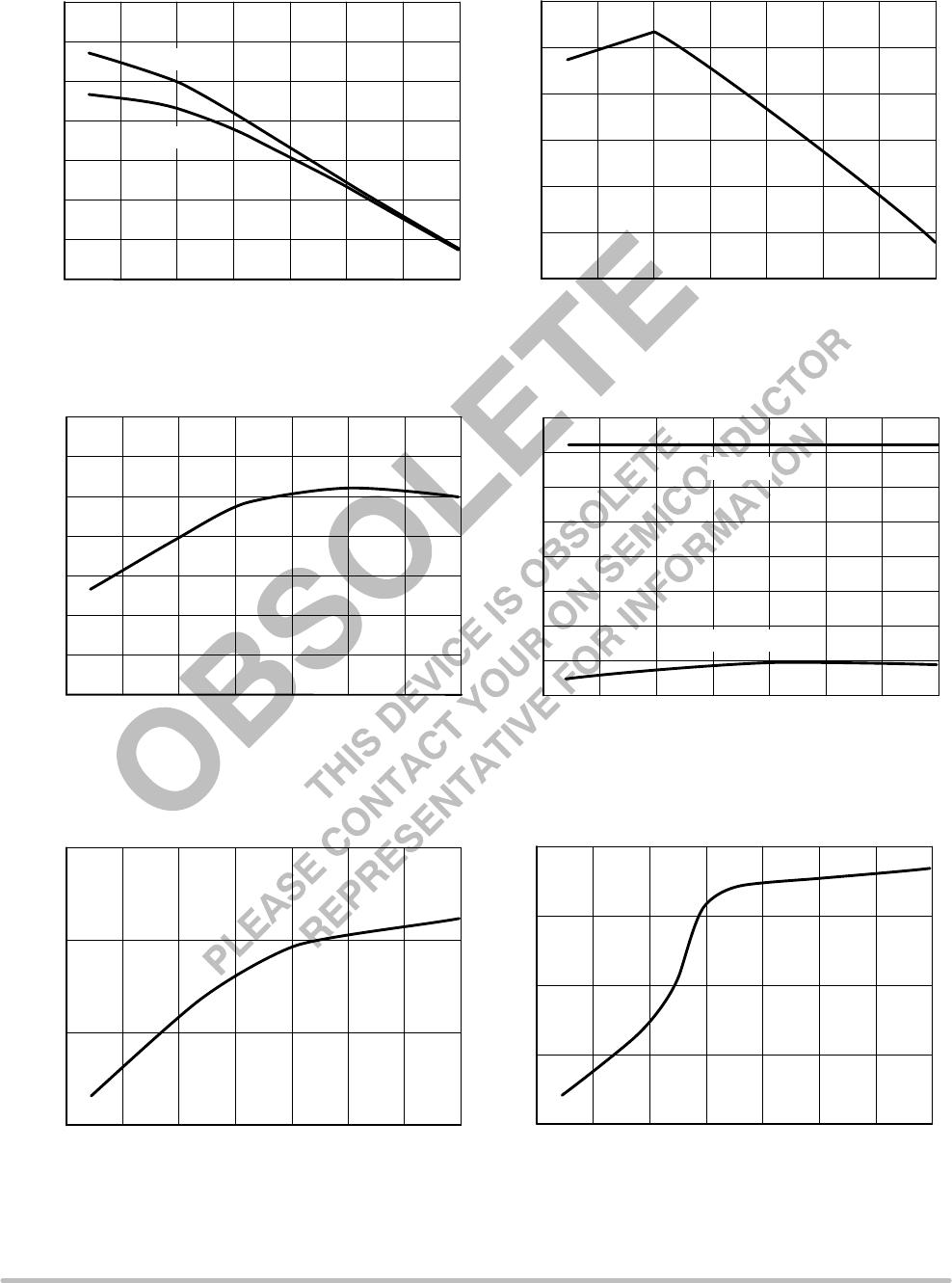

External Soft Start

The NCP158x features an external soft start function,

which reduces inrush current and overshoot of the output

voltage. Soft start is achieved by using the internal current

source of 10 mA. (typ), which charges the external integrator

capacitor of the transconductance amplifier. Figure 10 is a

typical soft start sequence. This sequence begins once V

CC

surpasses its UVLO threshold. During Soft Start, as the

Comp Pin rises through 400 mV, the PWM Logic and gate

drives are enabled. When the feedback voltage crosses

800 mV, the EOTA will be given control to switch to its

higher regulation mode output current of 120 mA. In the

event of an overcurrent during soft start, the overcurrent

logic will override the soft start sequence and will shut down

the PWM logic and both the high side and low side gates.

Figure 10. Soft Start Implementation

0.4 V

1.1 V

0.4 V

V

comp

Enable

V

fb

10 mA

10 mA

120 mA

Isource/

Sink

SS

-10 mA

Start Up Normal

Timing Diagram NCP1582: Enable Sequence

UVLO

Under Voltage Lockout (UVLO) is provided to ensure that

unexpected behavior does not occur when V

CC

is too low to

support the internal rails and power the converter. For the

NCP158x, the UVLO is set to ensure that the IC will start up

when V

CC

reaches 4.2 V and shutdown when V

CC

drops

below 3.7 V. This permits operation when converting from

a 5.0 input voltage.

Current Limit Protection

In case of a short circuit or overload, the low−side (LS)

FET will conduct large currents. The controller will shut

down the regulator in this situation for protection against

overcurrent. The low−side R

DSon

sense is implemented by

comparing the voltage at the Phase node when BG starts

going low to an internally generated fixed voltage. If the

phase voltage is lower than SCP trip voltage, an overcurrent

condition occurs and a counter is initiated. When the counter

completes, the PWM logic and both HS−FET and LS−FET

are turned off. The controller will retry to see if the short

circuit or overload condition is removed through the soft

start cycle. The minimum turn−on time of the LS−FET is set

to be 500 ns. The trip thresholds have a −95 mV, +45 mV

process and temperature variation.

Drivers

The NCP158x includes 0.7 A gate drivers to switch

external N−channel MOSFETs. This allows the NCP158x to

address high−power as well as low−power conversion

requirements. The gate drivers also include adaptive

non−overlap circuitry. The non−overlap circuitry increase

efficiency, which minimizes power dissipation, by

minimizing the body diode conduction time.

A detailed block diagram of the non−overlap and gate

drive circuitry used in the chip is shown in Figure 11.