ADADC71

Rev. C | Page 10 of 12

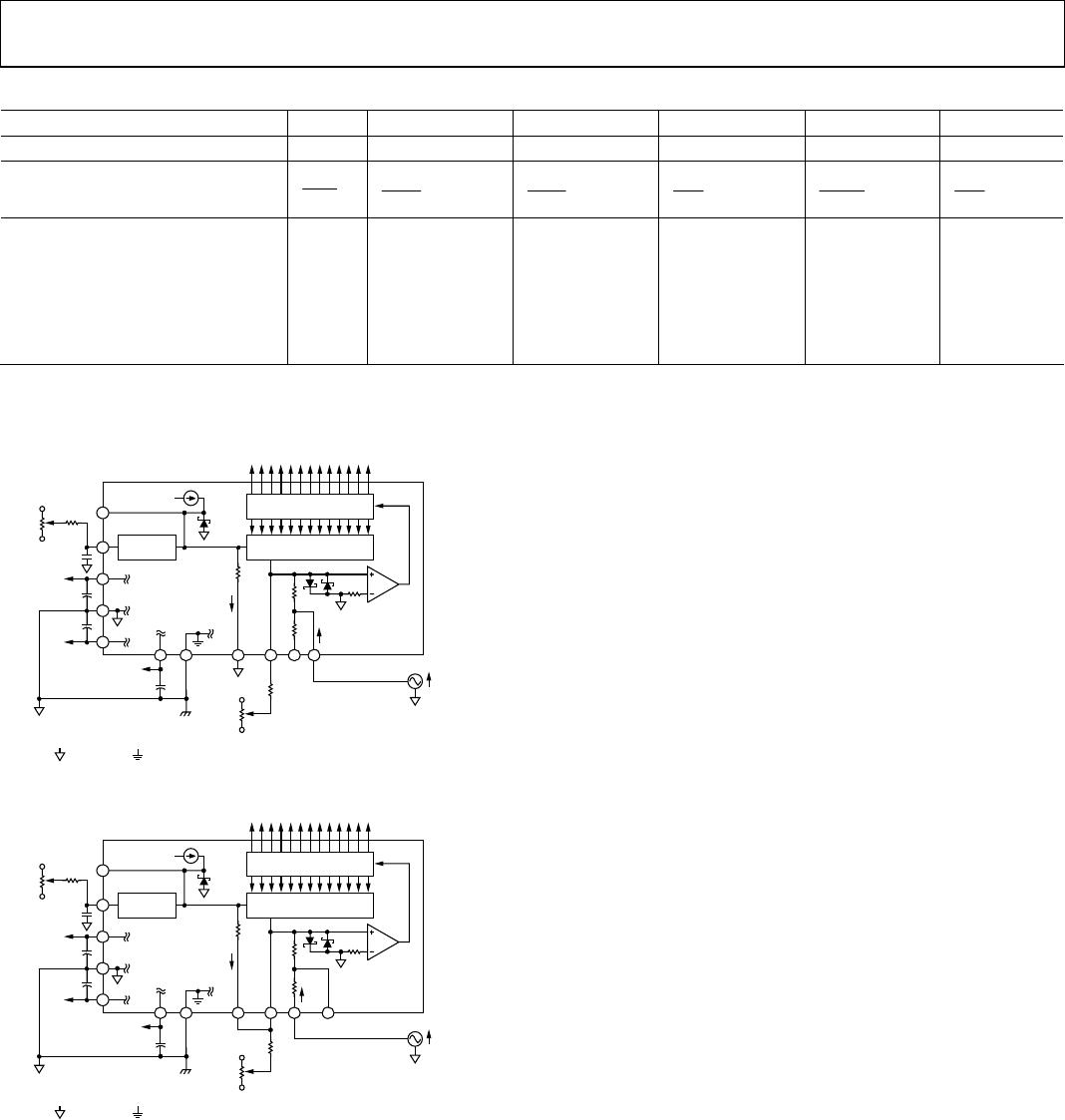

GROUNDING, DECOUPLING, AND LAYOUT

CONSIDERATIONS

Many data-acquisition components have two or more ground

pins, which are not connected together within the device. These

grounds are usually referred to as the DIGITAL COMMON

(logic power return), ANALOG COMMON (analog power

return), or analog signal ground. These grounds (Pin 19 and

Pin 22) must be tied together at one point as close as possible to

the converter. Ideally, a single solid analog ground plane under

the converter would be desirable. Current flows through the

wires and etch stripes of the circuit card, and since these paths

have resistance and inductance, hundreds of millivolts can be

generated between the system analog ground point and the

ground pins of the ADADC71. Separate wide conductor stripe

ground returns should be provided for high resolution

converters to minimize noise and IR losses from the current

flow in the path from the converter to the system ground point.

In this way the ADADC71 supply currents and other digital

logic-gate return currents are not summed into the same return

path as analog signals where they would cause measurement

errors.

Each of the ADADC71’s supply terminals should be capacitively

decoupled as close to the ADADC71 as possible. A large value,

such as 1 μF, capacitor in parallel with a 0.1 μF capacitor is

usually sufficient. Analog supplies are to be bypassed to the

ANALOG COMMON (analog power return) Pin 22 and the

logic supply is bypassed to DIGITAL COMMON (logic power

return) Pin 19.

The metal cover is internally grounded with respect to the

power supplies, grounds and electrical signals. Do not

externally ground the cover.

T/H REQUIREMENTS FOR HIGH RESOLUTION

APPLICATIONS

The characteristics required for high resolution track-and-hold

amplifiers are low feedthrough, low pedestal shifts with changes

of input signal or temperature, high linearity, low temperature

coefficients, and minimal droop rate.

The aperture jitter is a result of noise within the switching

network that modulates the phase of the hold command, and is

manifested in the variations in the value of the analog input that

has been held. The aperture error which results from this jitter

is directly related to the dV/dt of the analog input.

The T/H amplifier slew rate determines the maximum

frequency tracking rate and part of the settling time when

sampling pulses and square waves. The feedthrough from input

to output while in the hold mode should be less than 1 LSB. The

amplitude of 1 LSB of the companion ADC for a given input

range will vary from 610 μV for a 14-bit ADC using a 0 V to

+10 V input range to 4.88 mV for a 12-bit ADC using a ±10 V

input range. The hold mode droop rate should produce less

than 1 LSB of droop in the output during the conversion time of

the ADC. For 610 μV/LSB, as noted in the example above, for a

50 μs 14-bit ADC, the maximum droop rate is 610 μV/50 μs or

12 μV/μs during the 50 μs conversion period.

Minimal thermal tail effects are another requirement of high

resolution applications. The self-heating errors induced by the

changing current levels in the output stages of T/H amps may

cause more than 1 LSB of error due to thermal tail effects.

The linearity error should be less than 1 LSB over the transfer

function, as set by the resolution of the ADC. The T/H

acquisition time and T/H settling time along with the

conversion time of the ADC determines the highest sampling

rate. This in turn determines the highest input signal frequency

that can be sampled at twice a cycle.

The maximum input frequency is constrained by the Nyquist

sampling theorem to be half of the maximum throughput rate.

Input frequencies higher than half the maximum throughput

rate result in under sampling or aliasing errors of the input

signal.

The pedestal shift due to input signal changes should either be

linear, to be seen as a gain error, or negligible, as with the

feedthrough specification. The temperature coefficients for drift

would be low enough such that full accuracy is maintained over

some minimum temperature range. The droop rate and

pedestal shift increases above +70

o

C (+158

o

F). For commercial

and industrial users, these shifts only appear above the highest

temperatures their equipment might expect to experience. Most

precision instrumentation is installed only in human

inhabitable work spaces or in controlled enclosures if the area

has a hostile environment. Thus, the ADADC71 used with a

sample-and-hold amplifier offers high accuracy sampling in

high precision applications.