ADADC71

Rev. C | Page 7 of 12

DESCRIPTION OF OPERATION

On receipt of a CONVERT START command, the ADADC71

converts the voltage at its analog input into an equivalent 16-bit

binary number. This conversion is accomplished as follows: the

16-bit successive-approximation register (SAR) has its 16-bit

outputs connected both to the device bit output pins and to the

corresponding bit inputs of the feedback DAC. The analog

input is successively compared to the feedback DAC output, one

bit at a time (MSB first, LSB last). The decision to keep or reject

each bit is then made at the completion of each bit comparison

period, depending on the state of the comparator at that time.

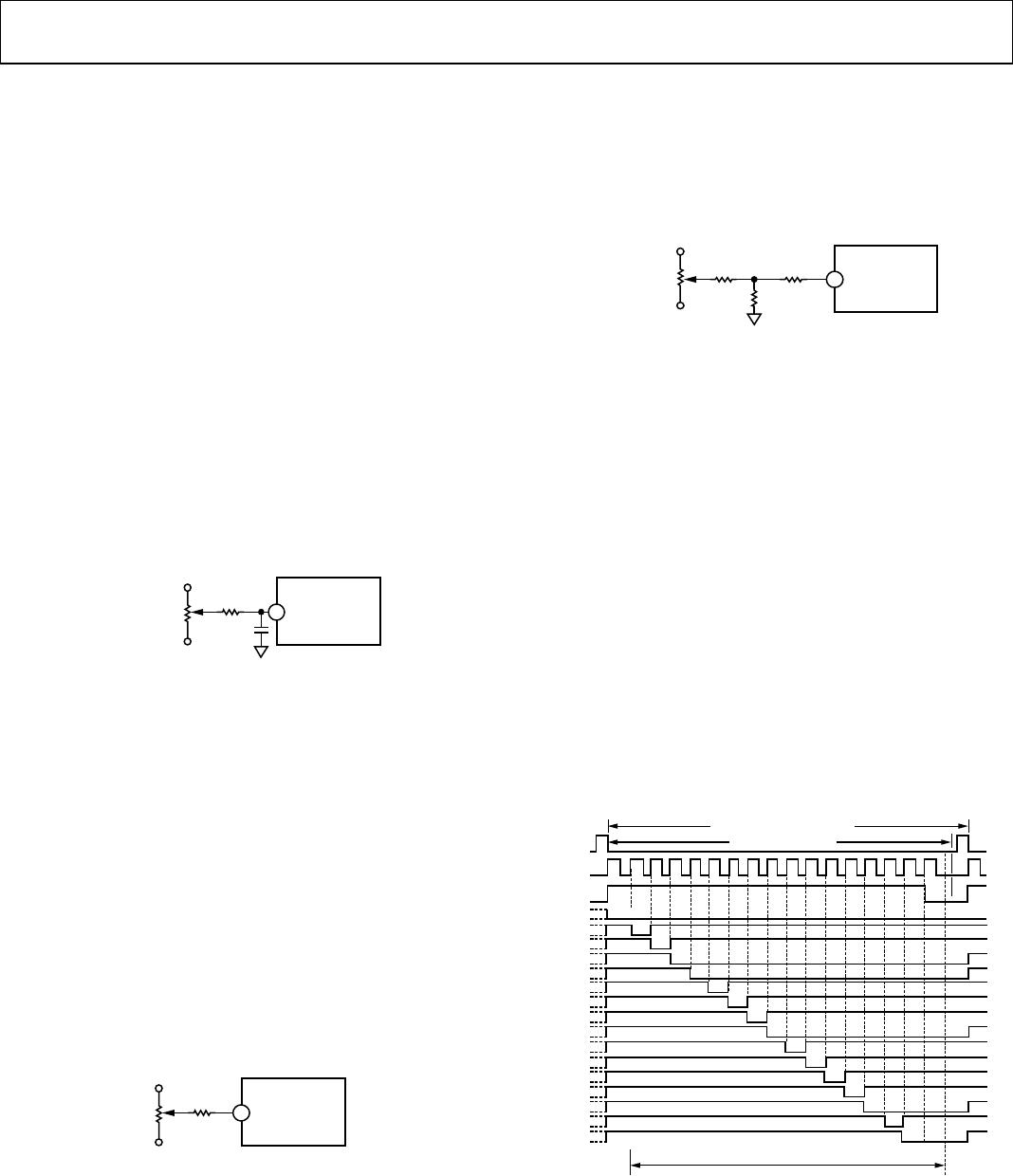

GAIN ADJUSTMENT

The gain adjustment circuit consists of a 100 ppm/

o

C poten-

tiometer connected across ±V

S

with its slider connected

through a 510 kΩ resistor to Pin 29 (GAIN ADJUST), as shown

in

Figure 5.

If no external trim adjustment is desired, Pin 27

(COMPARATOR IN) and Pin 29 may be left open.

03537-005

ADADC71

29

0.01μF

270kΩ

+15V

10kΩ

TO

100kΩ

100ppm/°C

–15V

Figure 5. Gain Adjustment Circuit

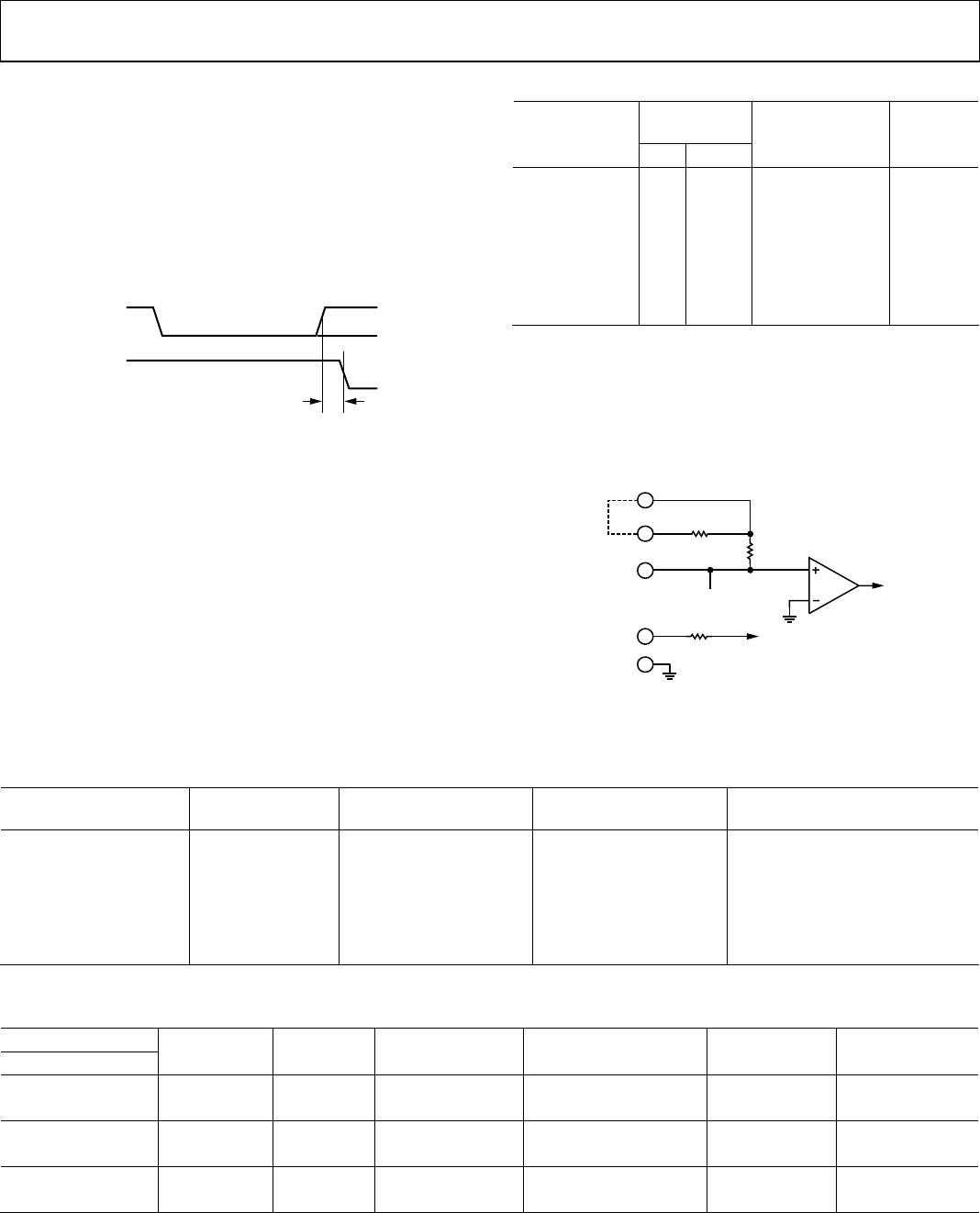

ZERO OFFSET ADJUSTMENT

The zero offset adjustment circuit consists of a 100 ppm/

o

C

potentiometer connected across ±V

S

with its slider connected

through a 1.8 MΩ resistor to Pin 27 for all ranges. As shown in

Figure 6, the tolerance of this fixed resistor is not critical; a

carbon composition type is generally adequate. Using a carbon

composition resistor with a −1200 ppm/

o

C temperature

coefficient contributes a worst-case offset temperature

coefficient of 32 LSB

B

14

× 61 ppm/ LSB

14

× 1200 ppm/ C =

2.3 ppm/ C of FSR, if the offset adjustment potentiometer is set

at either end of its adjustment range. Since the maximum offset

adjustment required is typically no more than ±16 LSB

o

o

14

, use of

a carbon composition offset summing resistor typically

contributes no more than 1 ppm/ C of FSR offset temperature

coefficient.

o

03537-006

ADADC71

27

1.8MΩ

+15V

10kΩ

TO

100kΩ

–15V

Figure 6. Zero Offset Adjustment Circuit

An alternate offset adjustment circuit, which contributes

negligible offset temperature coefficient if metal film resistors

(temperature coefficient < 100 ppm/

o

C) are used, is shown in

Figure 7.

In either adjustment circuit, the fixed resistor connected to

Pin 27 should be located close to this pin to keep the pin

connection runs short. Pin 27 is quite sensitive to external noise

pick-up.

03537-007

ADADC71

27

22kΩ M.F.

180kΩ M.F.

180kΩ M.F.

+15V

10kΩ

TO

100kΩ

OFFSET

ADJ

–15V

Figure 7. Low Temperature Coefficient Zero Adjustment Circuit

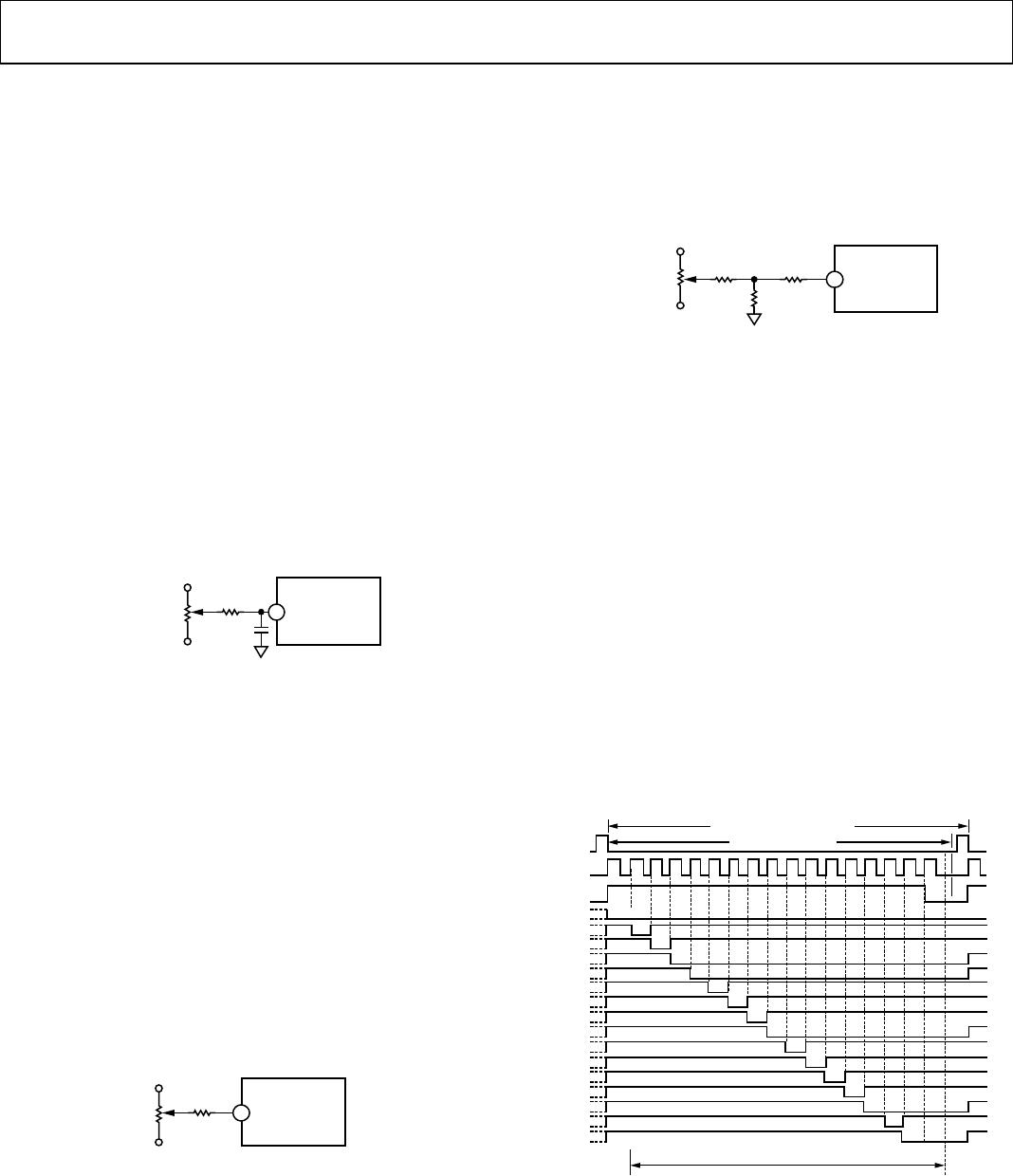

TIMING

The timing diagram is shown in Figure 8. Receipt of a

CONVERT START signal sets the STATUS flag, indicating

conversion in progress. This in turn removes the inhibit applied

to the gated clock, permitting it to run through 17 cycles. All

the SAR parallel bits, STATUS flip-flops, and the gated clock

inhibit signal are initialized on the trailing edge of the

CONVERT START signal. At time t

0

, B

1

is reset and B

2

to B

16

are

set unconditionally. At t

1

the Bit 1 decision is made (keep) and

Bit 2 is reset unconditionally. This sequence continues until the

Bit 16 (LSB) decision (keep) is made at t

16

. The STATUS flag is

reset, indicating that the conversion is complete and that the

parallel output data is valid. Resetting the STATUS flag restores

the gated clock inhibit signal, forcing the clock output to the

low Logic 0 state. Note that the clock remains low until the next

conversion.

Corresponding parallel data bits become valid on the same

positive-going clock edge.

03537-008

t

0

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

t

12

t

13

t

14

t

15

t

16

t

17

(4)

(3)

(1)

01 1 0 01 110 1 11 1 0 10

0

1

1

0

0

1

1

1

0

1

1

1

1

0

1

0

MSB

STATUS

INTERNAL

CLOCK

CONVERT

START

BIT 2

BIT 3

BIT 4

BIT 5

BIT 6

BIT 7

BIT 8

BIT 9

BIT 10

BIT 11

BIT 12

BIT 13

BIT 14

BIT 15

LSB

LSBMSB

MAXIMUM THROUGHPUT TIME

CONVERSION TIME (2)

NOTES:

1. THE CONVERT START PULSEWIDTH IS 50ns MIN AND MUST REMAIN LOW DURING A

CONVERSION. THE CONVERSION IS INITIATED BY THE TRAILING EDGE OF THE

CONVERT COMMAND.

2. 50μs FOR 14 BITS AND 45μs FOR 13 BITS (MAX).

2. MSB DECISION.

3. CLOCK REMAINS LOW AFTER LAST BIT DECISION.

Figure 8. Timing Diagram (Binary Code 0110011101111010)