LTC4370

12

4370f

In Figure 2b, 0.5I

L

• R

DS(ON)

is 125mV. The higher R

DS(ON)

rails the servo amplifier high as it cannot regulate the 25mV

V

FR(MIN)

across the lower supply’s MOSFET. Compared

to Figure 2a, the sharing capture range shrinks by 100mV

(125mV – 25mV) to ±400mV. However, the ΔV

IN

over

which currents are shared partially stays the same at

500mV + I

L

• R

S

. Even when not maximizing sharing range,

I

L

• R

DS(ON)

should be kept below 75mV for optimum

performance.

The peak power dissipation in the MOSFET occurs when

the entire load current is being sourced by one supply

with the maximum forward regulation voltage dropped

across the MOSFET (as shown in Figure 2a). Therefore,

the P

D(MAX)

rating of the MOSFET should satisfy:

P

D(MAX)

≥ I

L

• V

FR(MAX)

(3)

Table 1 provides starting guidelines for the type of

MOSFET package and heat sink required at various levels

of power dissipation. These are typical ranges for a room

temperature ambient with no air flow.

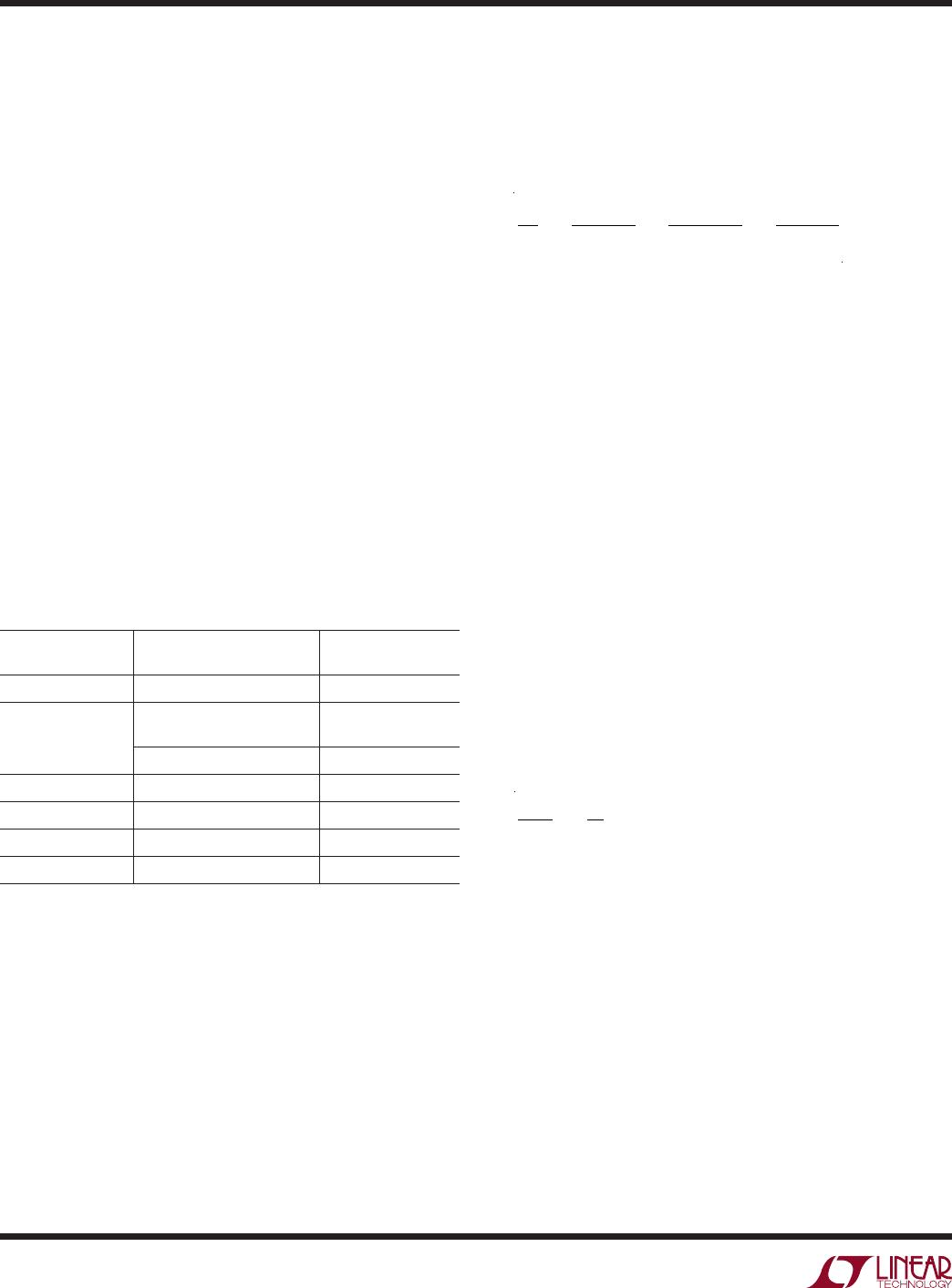

Table 1. Guidelines for MOSFET Power Dissipation

MAXIMUM POWER

DISSIPATED MOSFET PACKAGE HEAT SINK

0.5W to 1W SO-8 PCB

1W to 2W SO-8 With Exposed Pad,

D-Pak (TO-252)

PCB

TO-220 Standing in Free Air

2W to 4W DD-Pak (TO-263), TO-220 PCB

4W to 10W TO-220 Stamping

10W to 20W TO-220 Casting, Extrusion

20W to 50W TO-247, TO-3P Extrusion

Sense Resistor Selection

The sense resistor voltage drop dictates the current sharing

accuracy. Sharing error, due to the error amplifier input

offset, decreases with increasing sense voltage as:

ΔI

I

L

=

|I

1

– I

2

|

I

L

=

| V

EA(OS)

|

I

L

• R

S

=

2mV

I

L

• R

S

(4)

I

1

and I

2

are the two supply currents, I

L

is the load current

(I

1

+ I

2

= I

L

), R

S

is the sense resistor value, and V

EA(OS)

is the input offset of the internal error amplifier. A 25mV

sense resistor voltage drop with half of the load cur-

rent flowing through it (i.e., I

L

• R

S

= 50mV) gives a 4%

sharing error. A larger sense resistance may also be

needed if there is a connector in between the OUT pins

and the load to minimize the effect of its resistance. At

larger sense voltages the accuracy will be limited by the

sense resistor tolerance.

If sharing accuracy requirements can be relaxed, power

dissipated in the sense resistor can be reduced by selecting

a lower resistance. Worst-case power dissipation happens

at full load, i.e., when load current is not being shared.

While reducing the sense resistance, note that the sharing

loop does not close for load currents below V

EA(OS)

/R

S

.

The two sense resistors can have different values if the

application does not require the load current to be shared

equally between the supplies. In such a case:

R

S1

R

S2

=

I

2

I

1

(5)

CPO Capacitor Selection

The recommended value of the capacitor between the CPO

and V

IN

pins is approximately 10× the input capacitance C

ISS

of the MOSFET. A larger capacitor takes a correspondingly

longer time to be charged by the internal charge pump. A

smaller capacitor suffers more voltage drop during a fast

gate turn-on event as it shares charge with the MOSFET

gate capacitance.

applicaTions inForMaTion