REV. B

AD7470/AD7472

–11–

ADC TRANSFER FUNCTION

The output coding of the AD7470/AD7472 is straight binary.

The designed code transitions occur midway between succes-

sive integer LSB values (0.5 LSB, 1.5 LSB, etc). The LSB

size is equal to (REF IN)/4096 for the AD7472 and to (REF

IN)/1024 for the AD7470. The ideal transfer characteristic for

the AD7472 is shown in Figure 6.

111...111

111...110

111...000

011...111

000...010

000...001

000...000

ADC CODE

0V 0.5LSB V

REF

–1.5LSB

ANALOG INPUT

1LSB = V

REF

/4096

Figure 6. Transfer Characteristic for 12 Bits

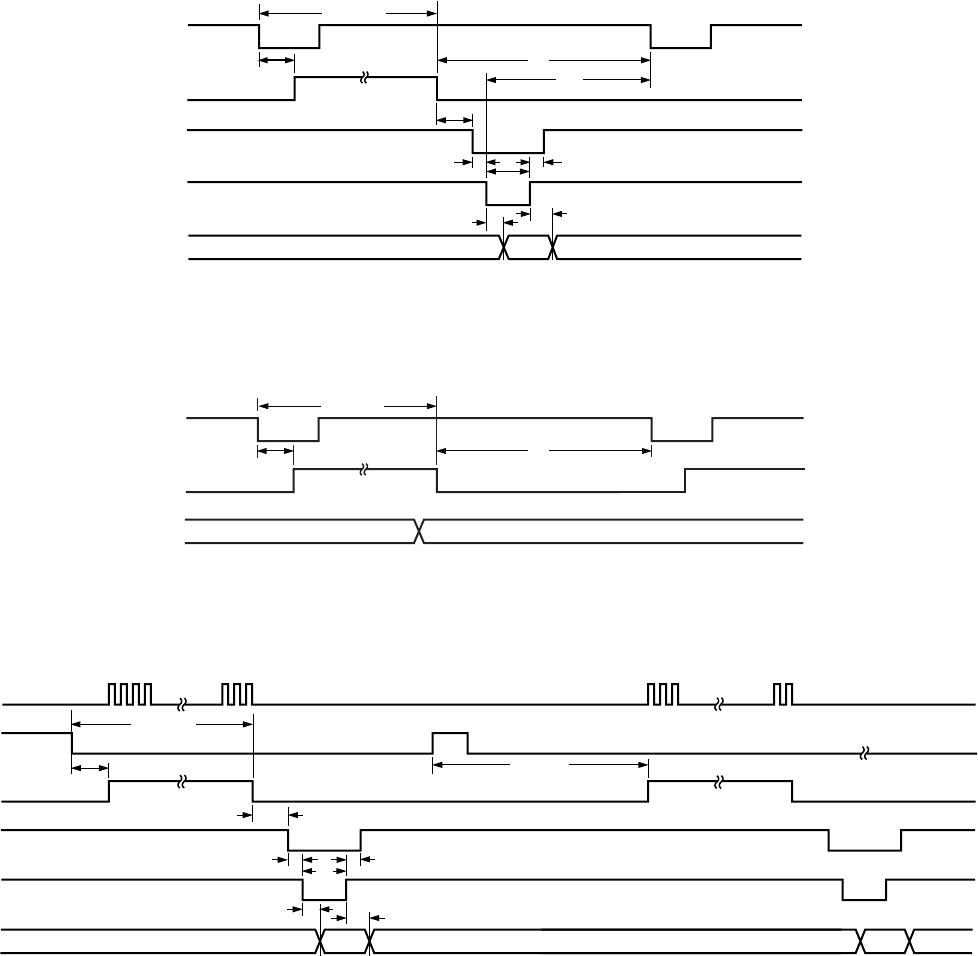

AC ACQUISITION TIME

In ac applications it is recommended to always buffer analog

input signals. The source impedance of the drive circuitry must

be kept as low as possible to minimize the acquisition time of

the ADC. Large values of impedance at the V

IN

pin of the ADC

will cause the THD to degrade at high input frequencies.

The AD8021, AD8047, AD8051, AD9631, and AD797 are

some of the op amps that could be used to buffer the analog

input. Figure 7 shows the AD7470/AD7472 performance for

some of those recommended input buffers.

TYPICAL AMPLIFIER

INPUT SNR THD CURRENT

BUFFERS 500kHz 500kHz CONSUMPTION

AD8047 70 78 5.8mA

AD9631 69.5 80 17mA

AD8051 68.6 78 4.4mA

AD797 70 84 8.2mA

AD7470/AD7472

DYNAMIC

PERFORMANCE

SPECIFICATIONS

Figure 7. Recommended Input Buffers

Reference Input

The following references are best suited for use with the

AD7470/AD7472.

ADR291

AD780

REF192

ADR421

For optimum performance, a 2.5 V reference is recommended.

The parts can function with a reference up to 3 V and down to

2 V, but the performance deteriorates.

DC ACQUISITION TIME

The ADC starts a new acquisition phase at the end of a conver-

sion and ends it on the falling edge of the CONVST signal. At

the end of conversion there is a settling time associated with the

sampling circuit. This settling time lasts approximately 135 ns.

The analog signal on V

IN

is also being acquired during this

settling time; therefore, the minimum acquisition time needed is

approximately 135 ns.

Figure 8 shows the equivalent charging circuit for the sampling

capacitor when the ADC is in its acquisition phase. R3 repre-

sents the source impedance of a buffer amplifier or resistive

network, R1 is an internal switch resistance, R2 is for bandwidth

control, and C1 is the sampling capacitor. C2 is back-plate

capacitance and switch parasitic capacitance.

During the acquisition phase the sampling capacitor must be

charged to within ±1 LSB of its final value.

R3

R1

125⍀

V

IN

C1

22pF

C2

8pF

R2

636⍀

Figure 8. Equivalent Sampling Circuit

ANALOG INPUT

Figure 9 shows the equivalent circuit of the analog input struc-

ture of the AD7470/AD7472. The two diodes, D1 and D2,

provide ESD protection for the analog inputs. The capacitor C3

is typically about 4 pF and can be primarily attributed to pin

capacitance. The resistor R1 is an internal switch resistance.

This resistor is typically about 125 Ω. The capacitor C1 is the

sampling capacitor, while R2 is used for bandwidth control.

R1

125⍀

V

IN

C1

22pF

C2

8pF

R2

636⍀

D1

D2

C3

4pF

V

DD

Figure 9. Equivalent Analog Input Circuit

CLOCK SOURCES

The max CLK specification for the AD7470 is 30 MHz, and for

the AD7472, it is 26 MHz. These frequencies are not standard

off-the-shelf oscillator frequencies. Many manufacturers pro-

duce oscillator modules close to these frequencies; a typical one

being 25.175 MHz from IQD Limited. AEL Crystals Limited

produces a 25 MHz oscillator module in various packages. Crys-

tal oscillator manufacturers will produce 26 MHz and 30 MHz

oscillators to order. Of course any clock source can be used, not

just crystal oscillators.