REV. B

AD7470/AD7472

–6–

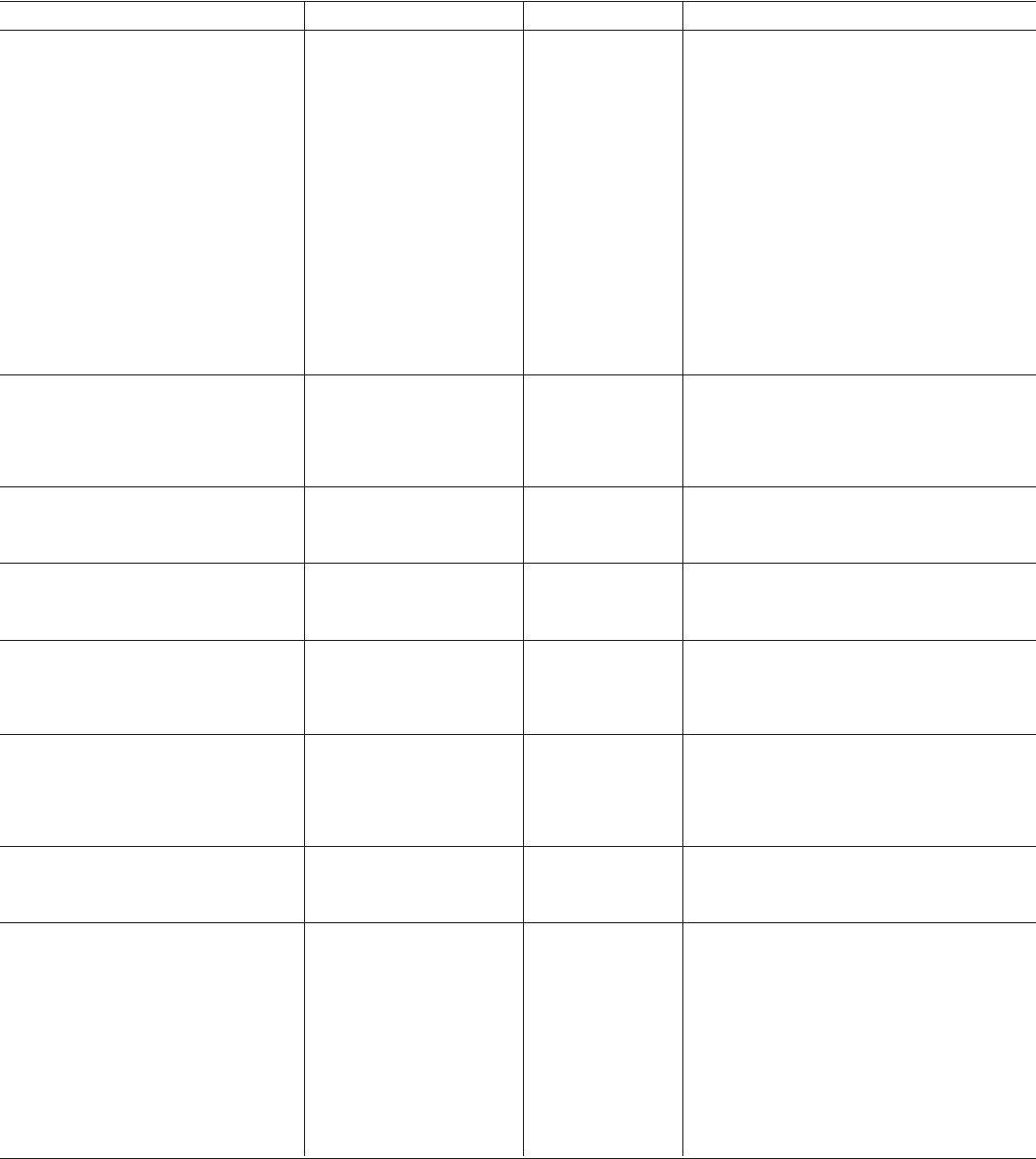

ORDERING GUIDE

Temperature Resolution Package Package

Model Range (Bits) Options

1

Description

AD7470ARU –40°C to +85°C10 RU-24 TSSOP

AD7470ARU-REEL –40°C to +85°C10 RU-24 TSSOP

AD7470ARU-REEL7 –40°C to +85°C10 RU-24 TSSOP

AD7472AR –40°C to +85°C12 R-24 SOIC

AD7472AR-REEL –40°C to +85°C12 R-24 SOIC

AD7472AR-REEL7 –40°C to +85°C12 R-24 SOIC

AD7472ARU –40°C to +85°C12 RU-24 TSSOP

AD7472ARU-REEL –40°C to +85°C12 RU-24 TSSOP

AD7472ARU-REEL7 –40°C to +85°C12 RU-24 TSSOP

AD7472BR –40°C to +85°C12 R-24 SOIC

AD7472BR-REEL –40°C to +85°C12 R-24 SOIC

AD7472BRU –40°C to +85°C12 RU-24 TSSOP

AD7472BRU-REEL –40°C to +85°C12 RU-24 TSSOP

AD7472BRU-REEL7 –40°C to +85°C12 RU-24 TSSOP

AD7472YR –40°C to +125°C12 R-24 SOIC

AD7472YR-REEL –40°C to +125°C12 R-24 SOIC

AD7472YRU –40°C to +125°C12 RU-24 TSSOP

AD7472YRU-REEL –40°C to +125°C12 RU-24 TSSOP

AD7472YRU-REEL7 –40°C to +125°C12 RU-24 TSSOP

EVAL-AD7470CB

2

Evaluation Board

EVAL-AD7472CB

2

Evaluation Board

EVAL CONTROL BRD2

3

Controller Board

NOTES

1

R = SOIC; RU = TSSOP.

2

This can be used as a standalone evaluation board or in conjunction with the EVAL-CONTROL BOARD for evaluation/demonstration purposes.

3

This board is a complete unit allowing a PC to control and communicate with all Analog Devices evaluation boards ending in the CB designators.

To order a complete evaluation kit, you need to order the specific ADC evaluation board, for example, EVAL-AD7472CB, the EVAL CONTROL

BRD2, and a 12 V ac transformer. See the relevant evaluation board application note for more information.

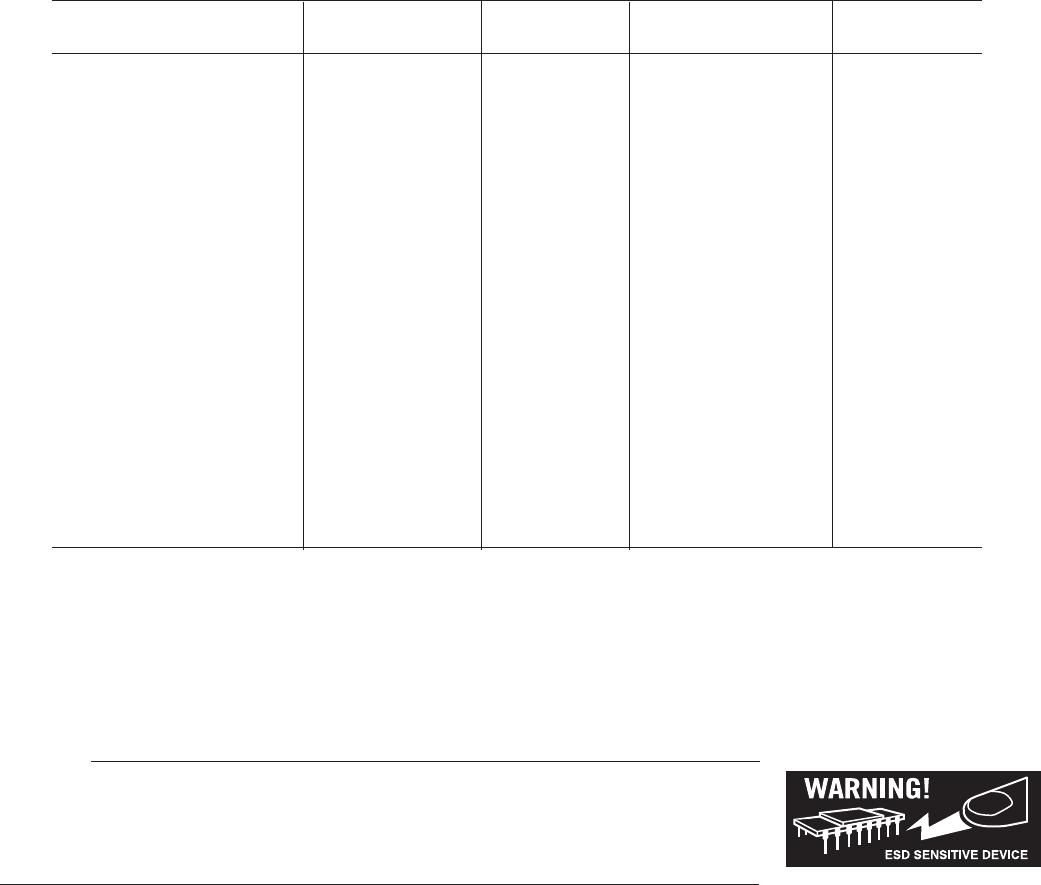

ABSOLUTE MAXIMUM RATINGS

1

(T

A

= 25°C unless otherwise noted.)

AV

DD

to AGND/DGND . . . . . . . . . . . . . . . . . –0.3 V to +7 V

DV

DD

to AGND/DGND . . . . . . . . . . . . . . . . . –0.3 V to +7 V

V

DRIVE

to AGND/DGND . . . . . . . . . . . . . . . . –0.3 V to +7 V

AV

DD

to DV

DD

. . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

V

DRIVE

to DV

DD

. . . . . . . . . . . . . . . –0.3 V to DV

DD

+ 0.3 V

AGND to DGND . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

Analog Input Voltage to AGND . . . . –0.3 V to AV

DD

+ 0.3 V

Digital Input Voltage to DGND . . . . –0.3 V to DV

DD

+ 0.3 V

REF IN to AGND . . . . . . . . . . . . . . . –0.3 V to AV

DD

+ 0.3 V

Input Current to Any Pin Except Supplies

2

. . . . . . . . ± 10 mA

Operating Temperature Range

Commercial (A and B Versions) . . . . . . . . . –40°C to +85°C

Industrial (Y Version) . . . . . . . . . . . . . . . –40°C to +125°C

Storage Temperature Range . . . . . . . . . . . –65°C to +150°C

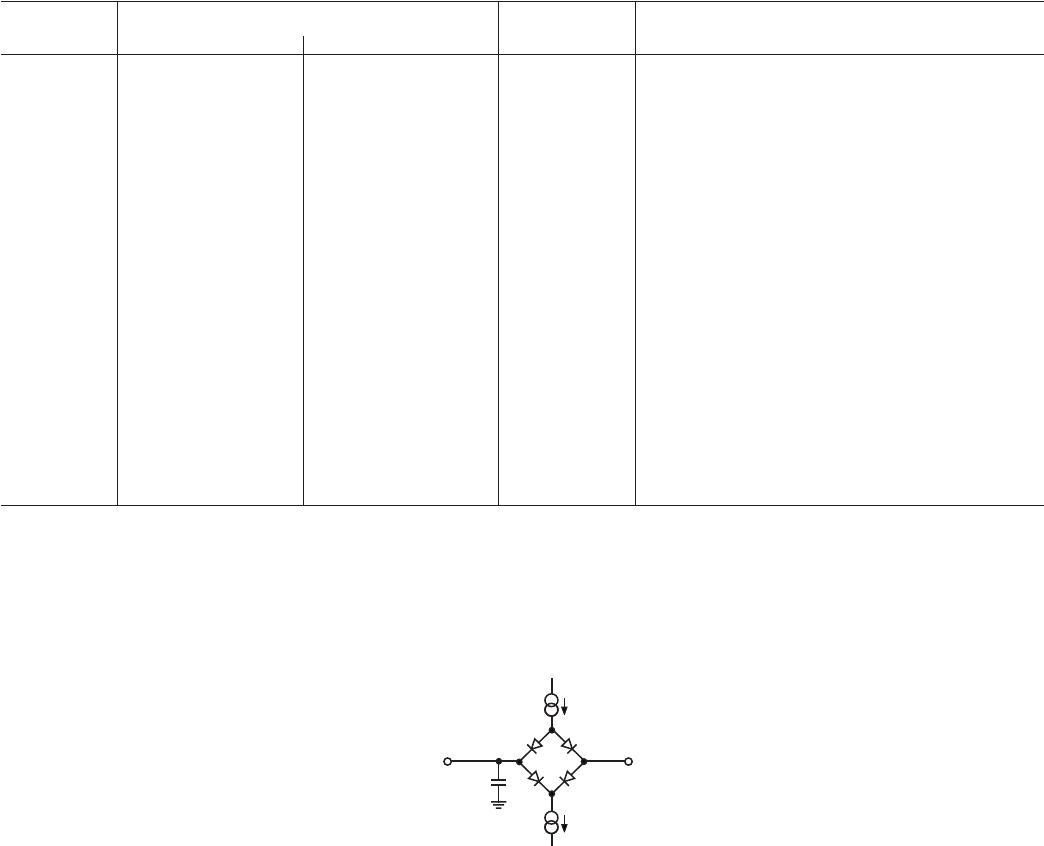

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7470/AD7472 features proprietary ESD protection circuitry, permanent dam-

age may occur on devices subjected to high energy electrostatic discharges. Therefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

θ

JA

Thermal Impedance . . . . . . . . . . . . . . . 75°C/W (SOIC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115°C/W (TSSOP)

θ

JC

Thermal Impedance . . . . . . . . . . . . . . . 25°C/W (SOIC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35°C/W (TSSOP)

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

ESD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5 kV

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Transient currents of up to 100 mA will not cause SCR latch-up.