REV. D

AD641

–11–

Unused pins (excluding Pins 8, 10 and 11) such as the attenua-

tor and applications resistors should be grounded close to the

package edge. BL1 (Pin 6) and BL2 (Pin 9) are internal bias

lines a volt or two above the –V

S

node; access is provided solely

for the addition of decoupling capacitors, which should be con-

nected exactly as shown (not all of them connect to the ground).

Use low impedance ceramic 0.1 µF capacitors (for example,

Erie RPE113-Z5U-105-K50V). Ferrite beads may be used

instead of supply decoupling resistors in cases where the supply

voltage is low.

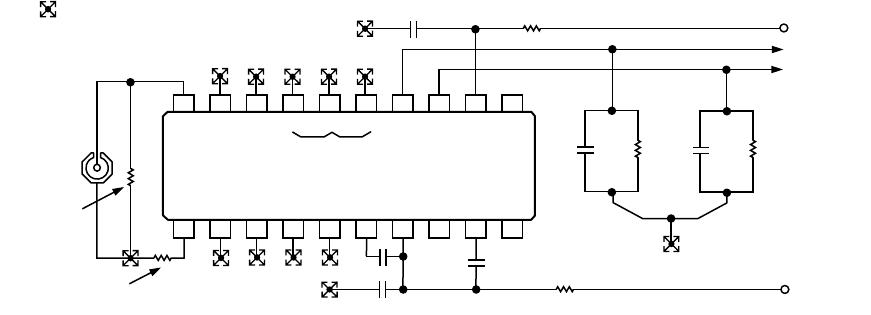

Active Current-to-Voltage Conversion

The compliance at LOG OUT limits the available output volt-

age swing. The output of the AD641 may be converted to a

larger, buffered output voltage by the addition of an operational

amplifier connected as a current-to-voltage (transresistance)

stage, as shown in Figure 21. Using a 2 kΩ feedback resistor

(R2) the 50 µA/dB output at LOG OUT is converted to a volt-

age having a slope of +100 mV/dB, that is, 2 V per decade.

This output ranges from roughly –0.4 V for zero signal inputs

to the AD641, crosses zero at a dc input of precisely +1 mV

(or –1 mV) and is +4 V for a dc input of 100 mV. A passive

prefilter, formed by R1 and C1, minimizes the high frequency

energy conveyed to the op amp. The corner frequency is here

shown as 10 MHz. The AD846 is recommended for this appli-

cation because of its excellent performance in transresistance

modes. Its bandwidth of 35 MHz (with the 2 kΩ feedback resis-

tor) will exceed the baseband response of the system in most

applications. For lower bandwidth applications other op amps

and multipole active filters may be substituted.

Effect of Frequency on Calibration

The slope and intercept of the AD641 are calibrated during

manufacture using a 2 kHz square wave input. Calibration

depends on the gain of each stage being 10 dB. When the input

frequency is an appreciable fraction of the 350 MHz bandwidth

of the amplifier stages, their gain becomes less precise and the

logarithmic slope and intercept are no longer as calibrated.

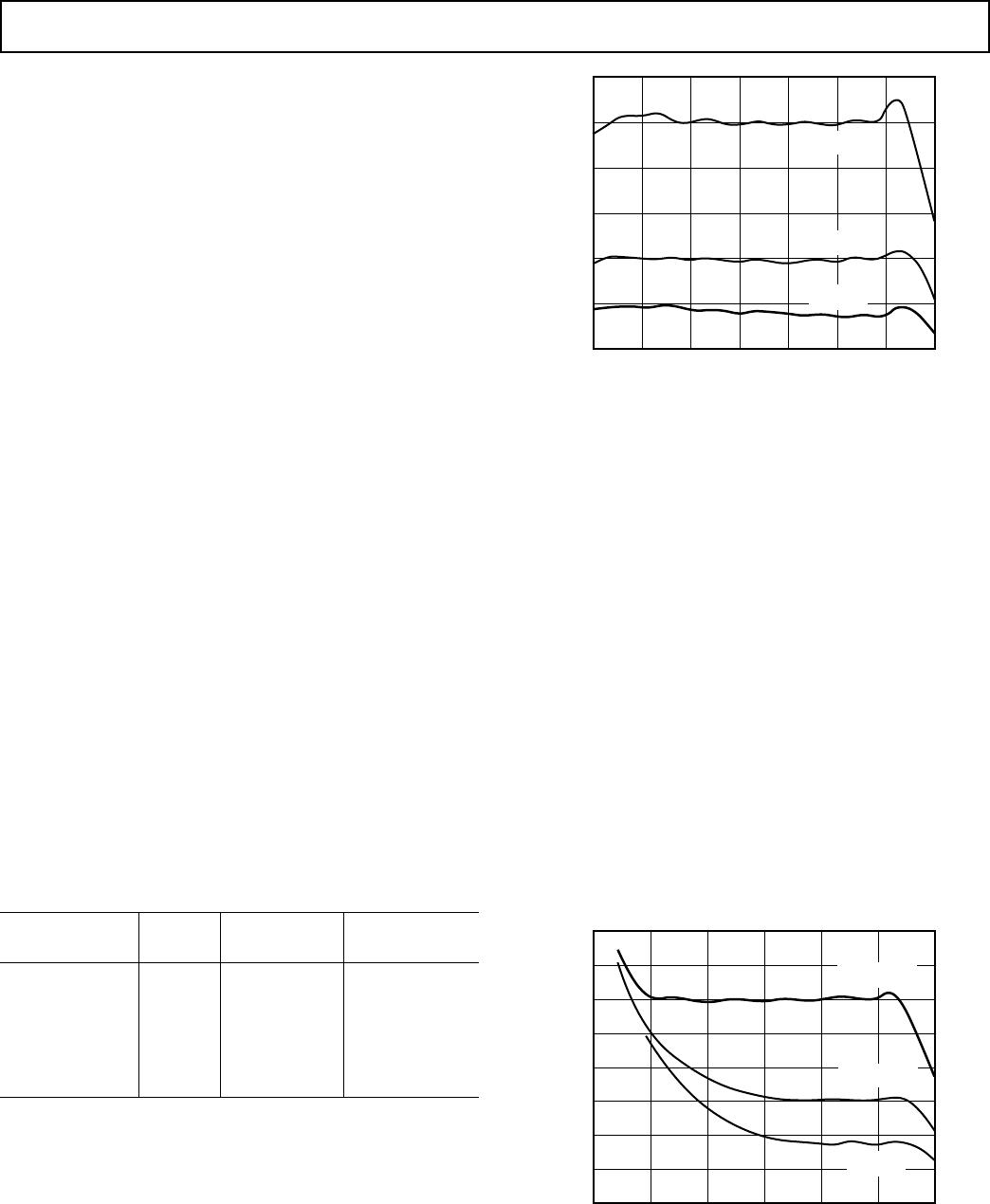

Figure 10 shows the averaged output current versus input level

at 50 MHz, 150 MHz, 190 MHz, 210 MHz, and 250 MHz.

Figure 11 shows the absolute error in the response at 200 MHz

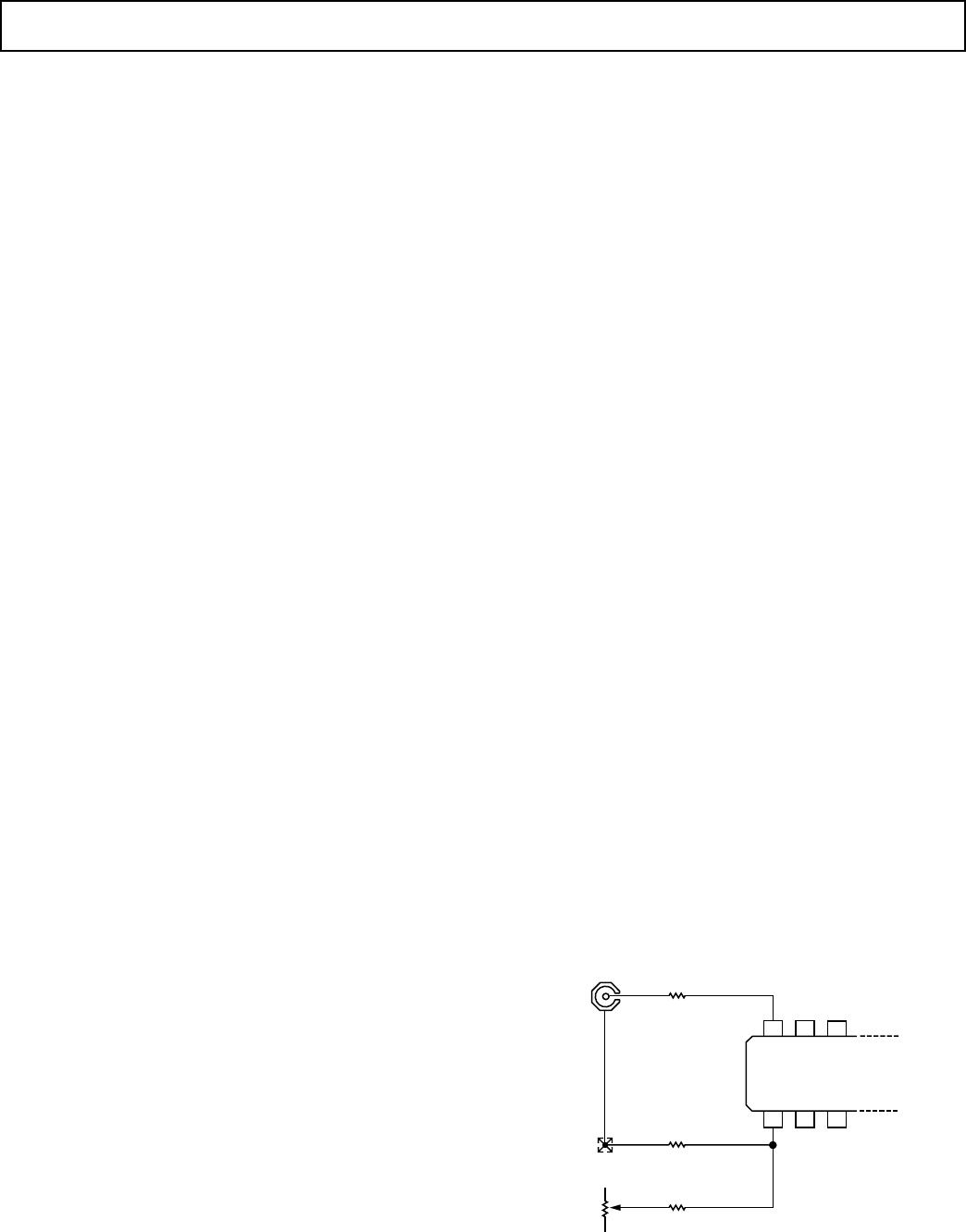

and at temperatures of –55°C, +25°C and +125°C. Figure 12

shows the variation in the slope current, and Figure 13 shows

the variation in the intercept level (sinusoidal input) versus

frequency.

If absolute calibration is essential, or some other value of slope

or intercept is required, there will usually be some point in the

user’s system at which an adjustment may be easily introduced.

For example, the 5% slope deficit at 50 MHz (see Figure 12)

may be restored by a 5% increase in the value of the load resis-

tor in the passive loading scheme shown in Figure 24, or by

inserting a trim potentiometer of 100 Ω in series with the feed-

back resistor in the scheme shown in Figure 21. The intercept

can be adjusted by adding or subtracting a small current to the

output. Since the slope current is 1 mA/decade, a 50 µA incre-

ment will move the intercept by 1 dB. Note that any error in

this current will invalidate the calibration of the AD641. For

example, if one of the 5 V supplies were used with a resistor to

generate the current to reposition the intercept by 20 dB, a

±10% variation in this supply will cause a ±2 dB error in the

absolute calibration. Of course, slope calibration is unaffected.

Source Resistance and Input Offset

The bias currents at the signal inputs (Pins 1 and 20) are typi-

cally 7 µA. These flow in the source resistances and generate

input offset voltages which may limit the dynamic range because

the AD641 is direct coupled and an offset is indistinguishable

from a signal. It is good practice to keep the source resistances

as low as possible and to equalize the resistance seen at each

input. For example, if the source resistance to Pin 20 is 100 Ω, a

compensating resistor of 100 Ω should be placed in series with

Pin 1. The residual offset is then due to the bias current offset,

which is typically under 1 µA, causing an extra offset uncertainty

of 100 µV in this example. For a single AD641 this will rarely be

troublesome, but in some applications it may need to be nulled

out, along with the internal voltage offset component. This may

be achieved by adding an adjustable voltage of up to ±250 µV

at the unused input. (Pins 1 and 20 may be interchanged with

no change in function.)

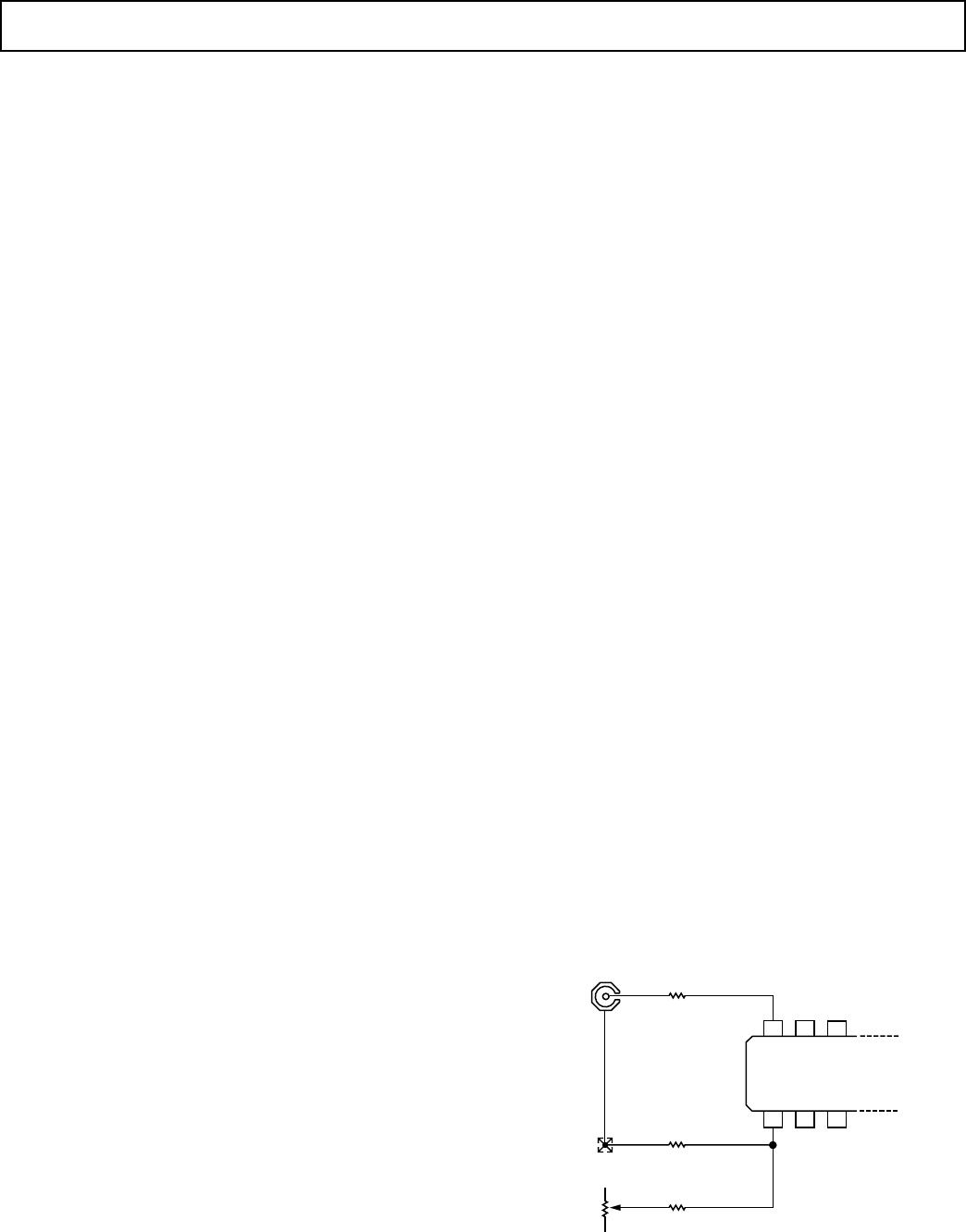

In most applications there will be no need to use any offset

adjustment. However, a general offset trimming circuit is shown

in Figure 25. R

S

is the source resistance of the signal. Note: 50

Ω

rf sources may include a blocking capacitor and have no dc path to

ground, or may be transformer coupled and have a near zero resis-

tance to ground. Determine whether the source resistance is zero,

25 Ω or 50 Ω (with the generator terminated in 50 Ω) to find

the correct value of bias compensating resistor, R

B

, which

should optimally be equal to R

S

, unless R

S

= 0, in which case

use R

B

= 5 Ω. The value of R

OS

should be set to 20,000 R

B

to

provide a ±250 µV trim range. To null the offset, set the source

voltage to zero and use a DVM to observe the logarithmic out-

put voltage. Recall that the LOG OUT current of the AD641

exhibits an absolute value response to the input voltage, so the

offset potentiometer is adjusted to the point where the logarithmic

output “turns around” (reaches a local maximum or minimum).

At high frequencies it may be desirable to insert a coupling

capacitor and use a choke between Pin 20 and ground, when

Pin 1 should be taken directly to ground. Alternatively, trans-

former coupling may be used. In these cases, there is no added

offset due to bias currents. When using two dc-coupled AD641s

(overall gain 100,000), it is impractical to maintain a sufficiently

low offset voltage using a manual nulling scheme. The section

CASCADED OPERATION explains how the offset can be

automatically nulled to submicrovolt levels by the use of a nega-

tive feedback network.

–5V

(SOURCE

RESISTANCE

OF

TERMINATED

GENERATOR)

R

B

2

19

1

20

R

OS

R

S

+5V

20kV

AD641

Figure 25. Optional Input Offset Voltage Nulling Circuit;

See Text for Component Values