REV. D

AD641

–13–

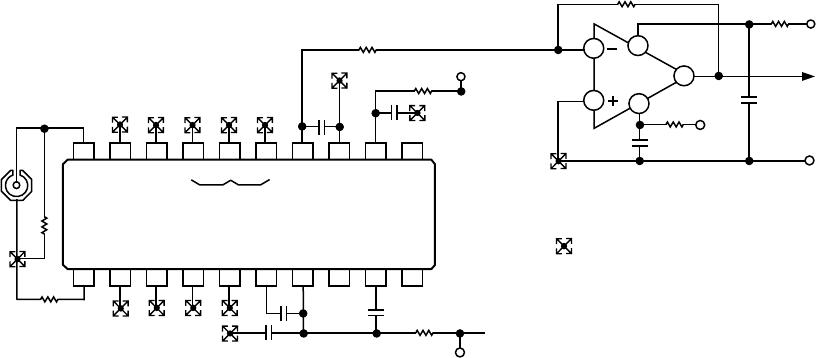

OPERATION OF CASCADED AD641S

Frequently, the dynamic range of the input will be 50 dB or

more. Two AD641s can be cascaded, as shown in Figure 27.

The balanced signal output from U1 becomes the input to U2.

Resistors are included in series with each LOG OUT pin and

capacitors C1 and C2 are placed directly between Pins 13 and 14

to provide a local path for the RF current at these output pairs.

C1 through C3 are chosen to provide the required low pass

corner in conjunction with the load R

L

. Board layout and

grounding disciplines are critically important at the high gain

(X100,000) and bandwidth (~ 150 MHz) of this system.

The intercept voltage is calculated as follows. First, note that if

its LOG OUT is disconnected, U1 simply inserts 50 dB of gain

ahead of U2. This would lower the intercept by 50 dB, to

–110 dBV for square wave calibration. With the LOG OUT of

U1 added in, there is a finite zero signal current which slightly

shifts the intercept. With the intercept temperature compensa-

tion on U1 disabled this zero signal output is –270 µA equiva-

lent to a 5.4 dB upward shift in the intercept, since the slope is

50 µA/dB. Thus, the intercept is at –104.6 dBV (–88 dBm for

50 Ω sine calibration). ITC may be disabled by grounding Pin 8

of either U1 or U2.

Cascaded AD641s can be used in dc applications, but input

offset voltage will limit the dynamic range. The dc intercept is

6 µV. The offset should not be confused with the intercept, which is

found by extrapolating the transfer function from its central “log

linear” region. This can be understood by referring to Equation

(1) and noting that an input offset is simply additive to the value

of V

IN

in the numerator of the logarithmic argument; it does not

affect the denominator (or intercept) V

X

. In dc coupled applica-

tions of wide dynamic range, special precautions must be taken

to null the input offset and minimize drift due to input bias

offset. It is recommended that the input attenuator be used,

providing a practical input range of –74 dBV (±200 µV dc) to

+6 dBV (±2 V dc) when nulled using the adjustment circuit

shown in Figure 25.

1920

21

U2

12

11

910

U1

1920

21

U2

12

11

910

U1

(a)

b

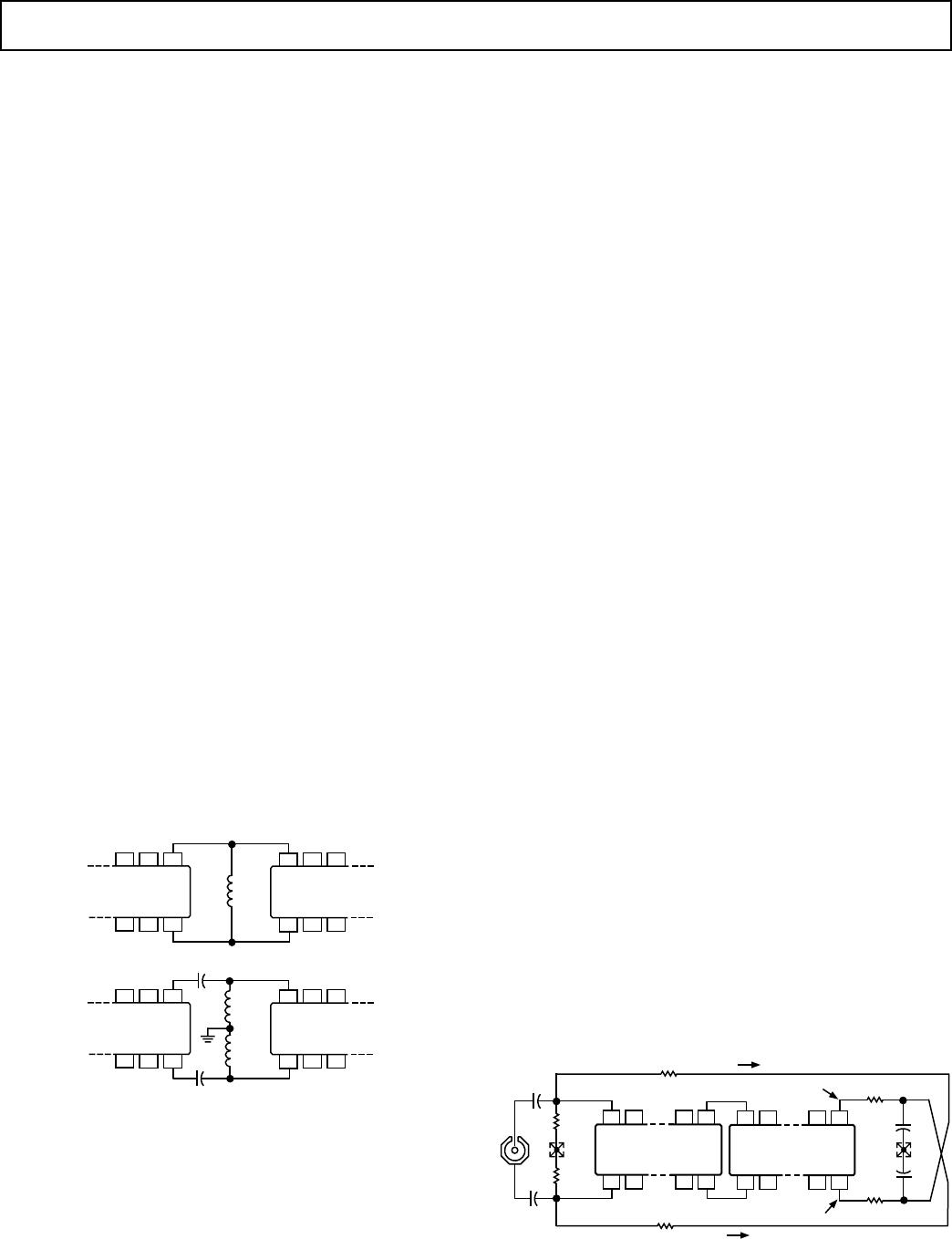

Figure 28. Two Methods for AC Coupling AD641s

Eliminating the Effect of First Stage Offset

Usually, the input signal will be sinusoidal and U1 and U2 can

be ac coupled. Figure 28a shows a low resistance choke at the

input of U2 which shorts the dc output of U1 while preserving

the hf response. Coupling capacitors may be inserted (Figure

28b) in which case two chokes are used to provide bias paths for

U2. These chokes must exhibit high impedance over the operat-

ing frequency range.

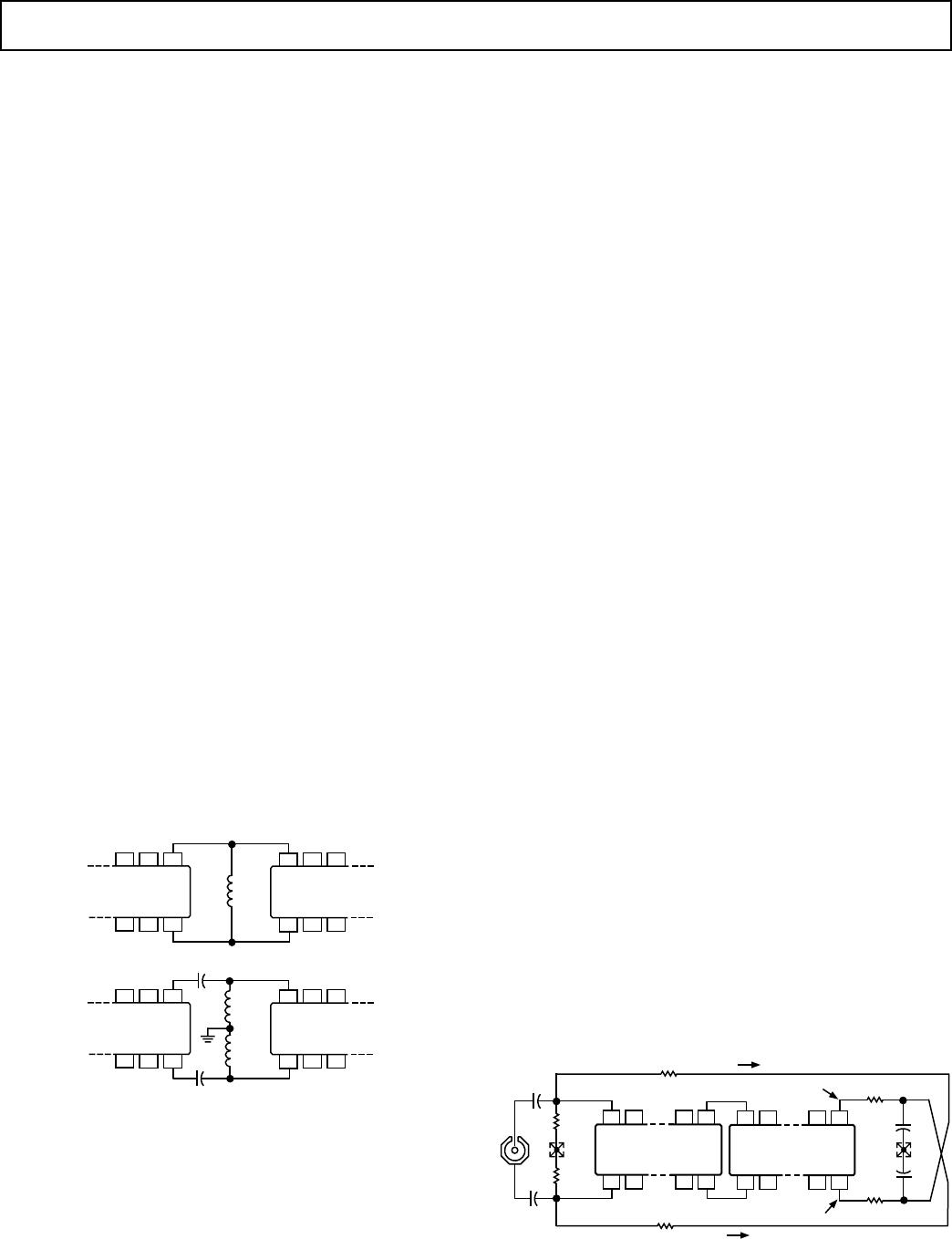

Alternatively, the input offset can be nulled by a negative feed-

back network from the SIG OUT nodes of U2 to the SIG IN

nodes of U1, as shown in Figure 29. The low pass response of

the feedback path transforms to a closed-loop high pass response.

The high gain (×100,000) of the signal path results in a com-

mensurate reduction in the effective time constant of this net-

work. For example, to achieve a high pass corner of 100 kHz,

the low pass corner must be at 1 Hz.

In fact, it is somewhat more complicated than this. When the ac

input sufficiently exceeds that of the offset, the feedback be-

comes ineffective and the response becomes essentially dc

coupled. Even for quite modest inputs the last stage will be

limiting and the output (Pins 10 and 11) of U2 will be a square

wave of about ±180 mV amplitude, dwelling approximately

equal times at its two limit values, and thus having a net average

value near zero. Only when the input is very small does the high

pass behavior of this nulling loop become apparent. Consequently,

the low pass time constant can usually be reduced considerably

without serious performance degradation.

The resistor values are chosen such that the dc feedback is

adequate to null the worst case input offset, say, 500 µV. There

must be some resistance at Pins 1 and 20 across which the offset

compensation voltage is developed. The values shown in the

figure assume that we wish to terminate a 50 Ω source at Pin 20.

The 50 Ω resistor at Pin 1 is essential, both to minimize offsets

due to bias current mismatch and because the outputs at Pins

10 and 11 can only swing negatively (from ground to –180 mV)

whereas we need to cater for input offsets of either polarity.

For a sine input of 1 µV amplitude (–120 dBV) and in the ab-

sence of offset, the differential voltage at Pins 10 and 11 of U2

would be almost sinusoidal but 100,000 times larger, or 100 mV.

The last limiter in U2 would be entering saturation. A 1 µV

input offset added to this signal would put the last limiter well

into saturation, and its output would then have a different aver-

age value, which is extracted by the low pass network and deliv-

ered back to the input. For larger signals, the output approaches a

square wave for zero input offset and becomes rectangular when

offset is present. The duty cycle modulation of this output now

produces the nonzero average value. Assume a maximum re-

quired differential output of 100 mV (after averaging in C1 and

C2) as shown in Figure 29. R3 through R6 can now be chosen

to provide ±500 µV of correction range, and with these values

the input offset is reduced by a factor of 500. Using 4.7 µF

capacitors, the time constant of the network is about 1.2 ms,

and its corner frequency is at 13.5 Hz. The closed loop high

pass corner (for small signals) is, therefore, at 1.35 MHz.

20

110

11

U1

A

VE

= –140mV

INPUT

20

110

11

U2

R1

50V

R2

50V

C1

C2

A

VE

= –140mV

R3

4.99kV

R5

4.99kV

–200mV

–700mV

4mA

14mA

R4

4.99kV

R6

4.99kV

Figure 29. Feedback Offset Correction Network