BD8153EFV

Technical Note

15/17

www.rohm.com

2009.07 - Rev.B

© 2009 ROHM Co., Ltd. All rights reserved.

●Operation Notes

1) Absolute maximum ratings

Use of the IC in excess of absolute maximum ratings such as the applied voltage or operating temperature range may

result in IC damage. Assumptions should not be made regarding the state of the IC (short mode or open mode) when such

damage is suffered. A physical safety measure such as a fuse should be implemented when use of the IC in a special

mode where the absolute maximum ratings may be exceeded is anticipated.

2) GND potential

Ensure a minimum GND pin potential in all operating conditions.

3) Setting of heat

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

4) Pin short and mistake fitting

Use caution when orienting and positioning the IC for mounting on printed circuit boards. Improper mounting may result in

damage to the IC. Shorts between output pins or between output pins and the power supply and GND pins caused by the

presence of a foreign object may result in damage to the IC.

5) Actions in strong magnetic field

Use caution when using the IC in the presence of a strong magnetic field as doing so may cause the IC to malfunction.

6) Testing on application boards

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress.

Always discharge capacitors after each process or step. Ground the IC during assembly steps as an antistatic measure,

and use similar caution when transporting or storing the IC. Always turn the IC's power supply off before connecting it to or

removing it from a jig or fixture during the inspection process.

7) Ground wiring patterns

When using both small signal and large current GND patterns, it is recommended to isolate the two ground patterns,

placing a single ground point at the application's reference point so that the pattern wiring resistance and voltage

variations caused by large currents do not cause variations in the small signal ground voltage. Be careful not to change the

GND wiring patterns of any external components.

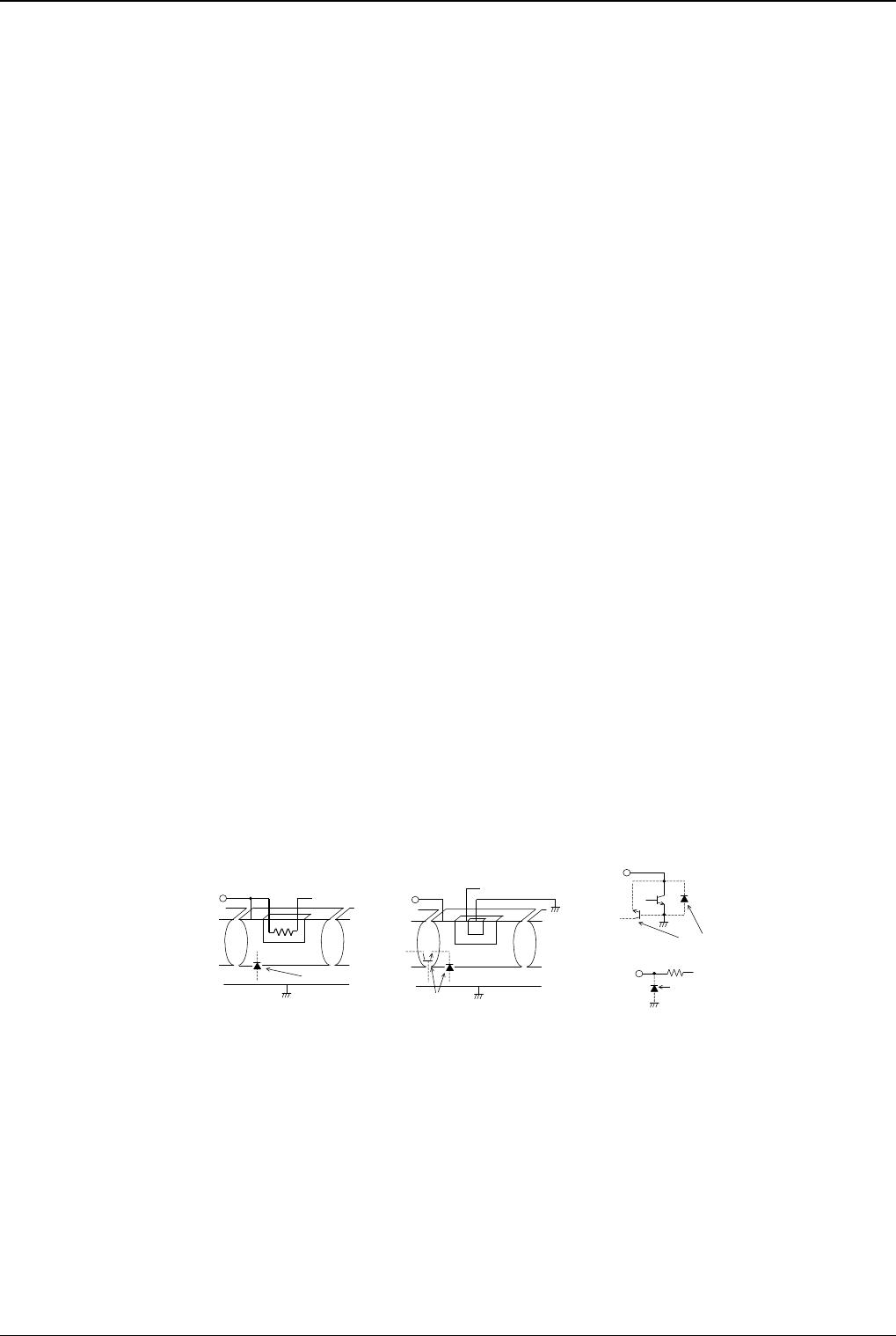

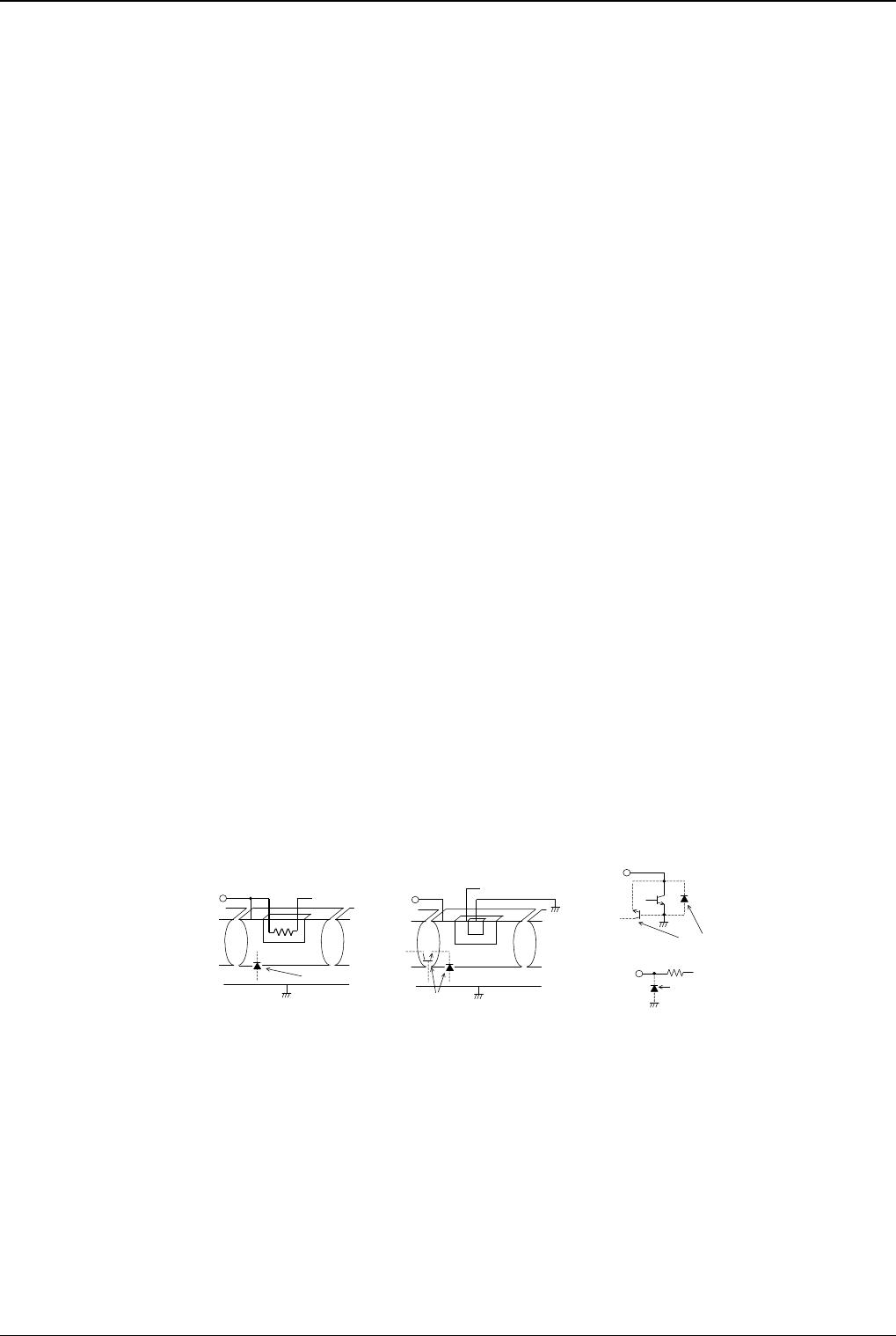

8) This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated.

P/N junctions are formed at the intersection of these P layers with the N layers of other elements to create a variety of

parasitic elements.

For example, when the resistors and transistors are connected to the pins as shown in Fig. 44, a parasitic diode or a

transistor operates by inversing the pin voltage and GND voltage.

The formation of parasitic elements as a result of the relationships of the potentials of different pins is an inevitable result

of the IC's architecture. The operation of parasitic elements can cause interference with circuit operation as well as IC

malfunction and damage. For these reasons, it is necessary to use caution so that the IC is not used in a way that will

trigger the operation of parasitic elements, such as the application of voltages lower than the GND (P board) voltage to

input and output pins.

9) Overcurrent protection circuits

An over current protection circuit designed according to the output current is incorporated for the prevention of IC

destruction that may result in the event of load shorting. This protection circuit is effective in preventing damage due to

sudden and unexpected accidents. However, the IC should not be used in applications characterized by the continuous

operation or transitioning of the protection circuits. At the time of thermal designing, keep in mind that the current capability

has negative characteristics to temperatures.

Pin A

GND

N

P

N N

P+ P+

Resistor

Parasitic element

P

~

~

Parasitic elements

Pin B

~

~

GND

C

B

E

Parasitic element

GND

Pin A

~

~

GND

N

P

N N

P+

P

+

Parasitic elements

P substrate

Pin B

C

B

E

Transistor (NPN)

~

~

N

GND

Fig.44 Example of a Simple Monolithic IC Architecture