BD8153EFV

Technical Note

8/17

www.rohm.com

2009.07 - Rev.B

© 2009 ROHM Co., Ltd. All rights reserved.

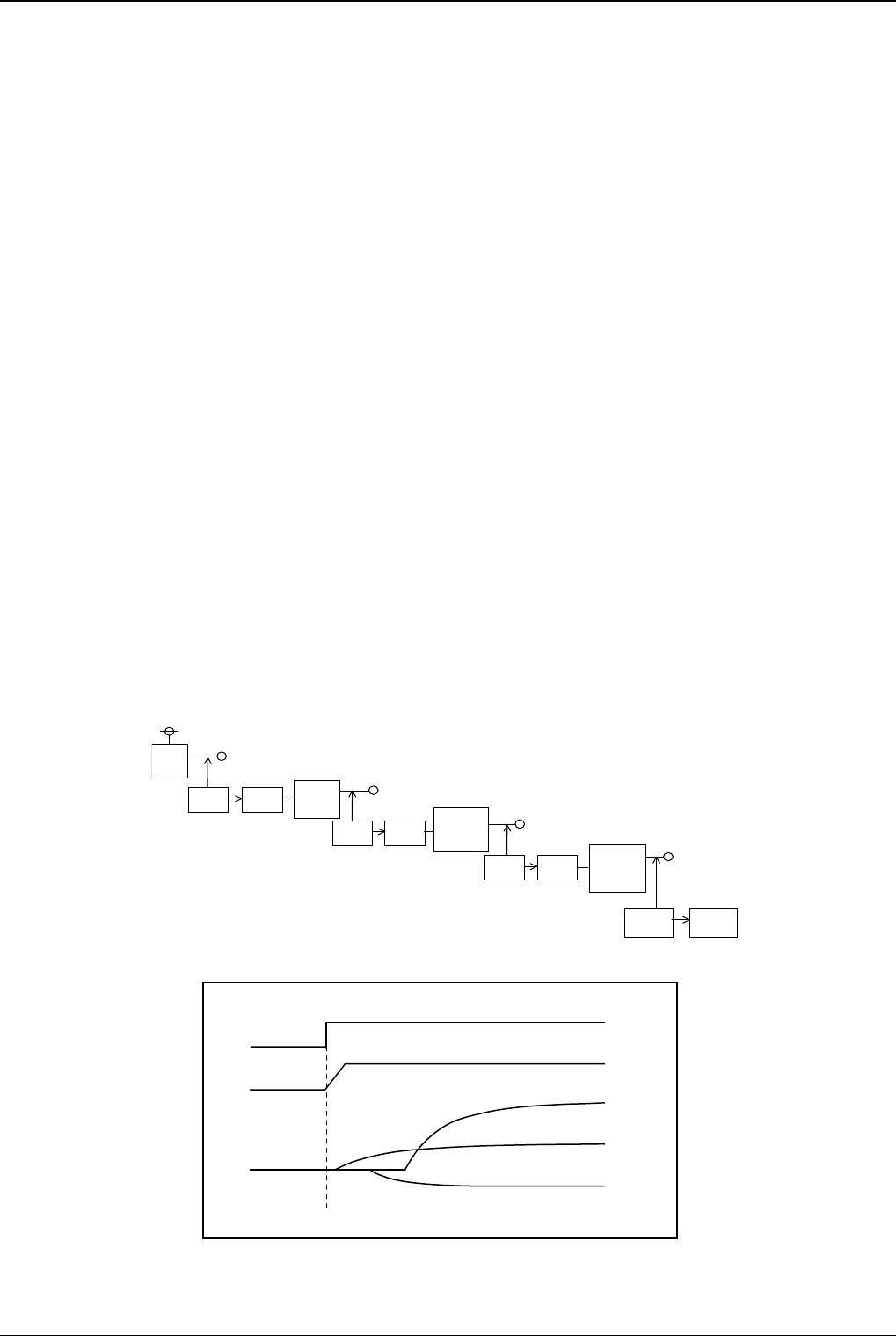

●Selecting Application Components

(1) Setting the Output L Constant

The coil to use for output is decided by the rating current I

LR and input current maximum value IINMAX of the coil.

Adjust so that I

INMAX +∆IL does not reach the rating current value ILR. At this time, ∆IL can be obtained by the following equation.

ΔI

L =

1

VCC

Vo-VCC

1

L VCC f

Set with sufficient margin because the coil value may have the dispersion of 30%. If the coil current exceeds the rating

current I

LR of the coil, it may damage the IC internal element.

BD8153EFV uses the current mode DC/DC converter control and has the optimized design at the coil value. A coil

inductance (L) of 4.7 µH to 15 µH is recommended from viewpoints of electric power efficiency, response, and stability.

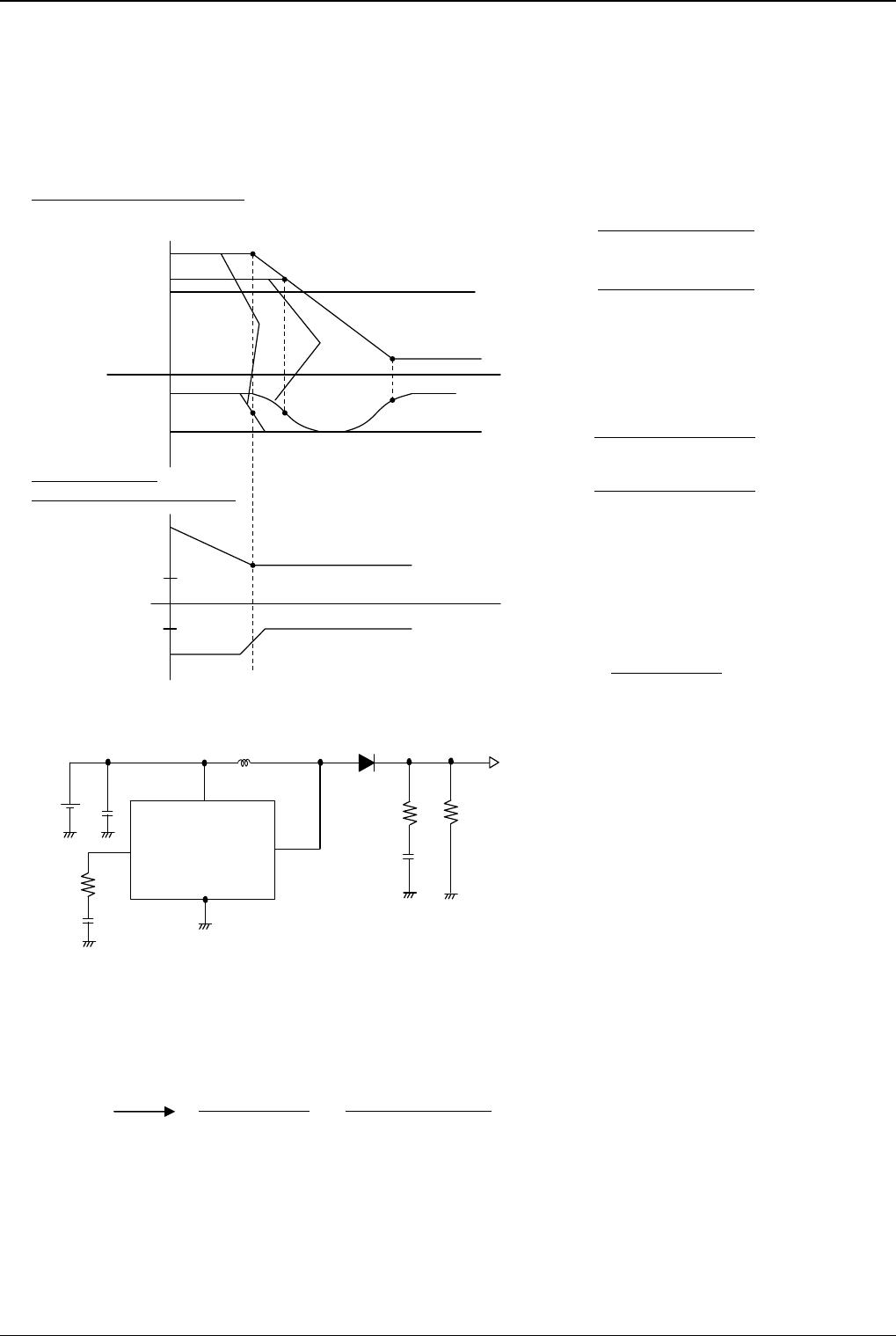

(2) Output Capacity Settings

For the capacitor to use for the output, select the capacitor which has the larger value in the ripple voltage V

PP

allowance value and the drop voltage allowance value at the time of sudden load change. Output ripple voltage is

decided by the following equation.

ΔV

PP = ILMAX RESR +

1

VCC

(ILMAX -

ΔI

L

)

fCo Vo 2

Perform setting so that the voltage is within the allowable ripple voltage range.

For the drop voltage during sudden load change; V

DR, please perform the rough calculation by the following equation.

VDR =

ΔI

10 us [V]

Co

However, 10 µs is the rough calculation value of the DC/DC response speed. Please set the capacitance considering

the sufficient margin so that these two values are within the standard value range.

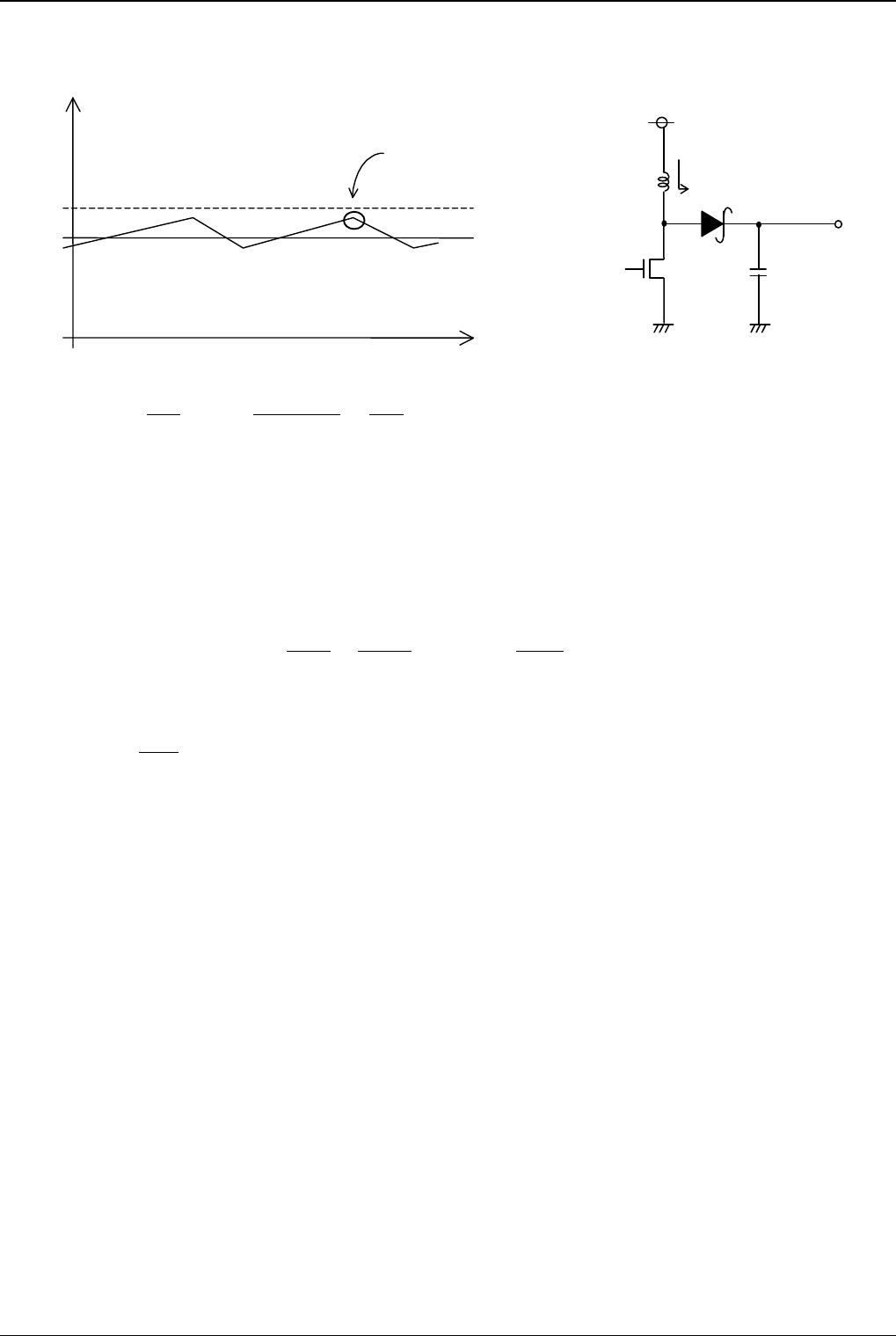

(3) Selecting the Input Capacitor

Since the peak current flows between the input and output at the DC/DC converter, a capacitor is required to install at

the input side. For the reason, the low ESR capacitor is recommended as an input capacitor which has the value more

than 10 µF and less than 100 m. If a capacitor out of this range is selected, the excessive ripple voltage is superposed

on the input voltage, accordingly it may cause the malfunction of IC.

However these conditions may vary according to the load current, input voltage, output voltage, inductance and

switching frequency. Be sure to perform the margin check using the actual product.

[A] Here, f is the switching frequency.

[V] Here, f is the switching frequency.

Fig. 27 Coil Current Waveform

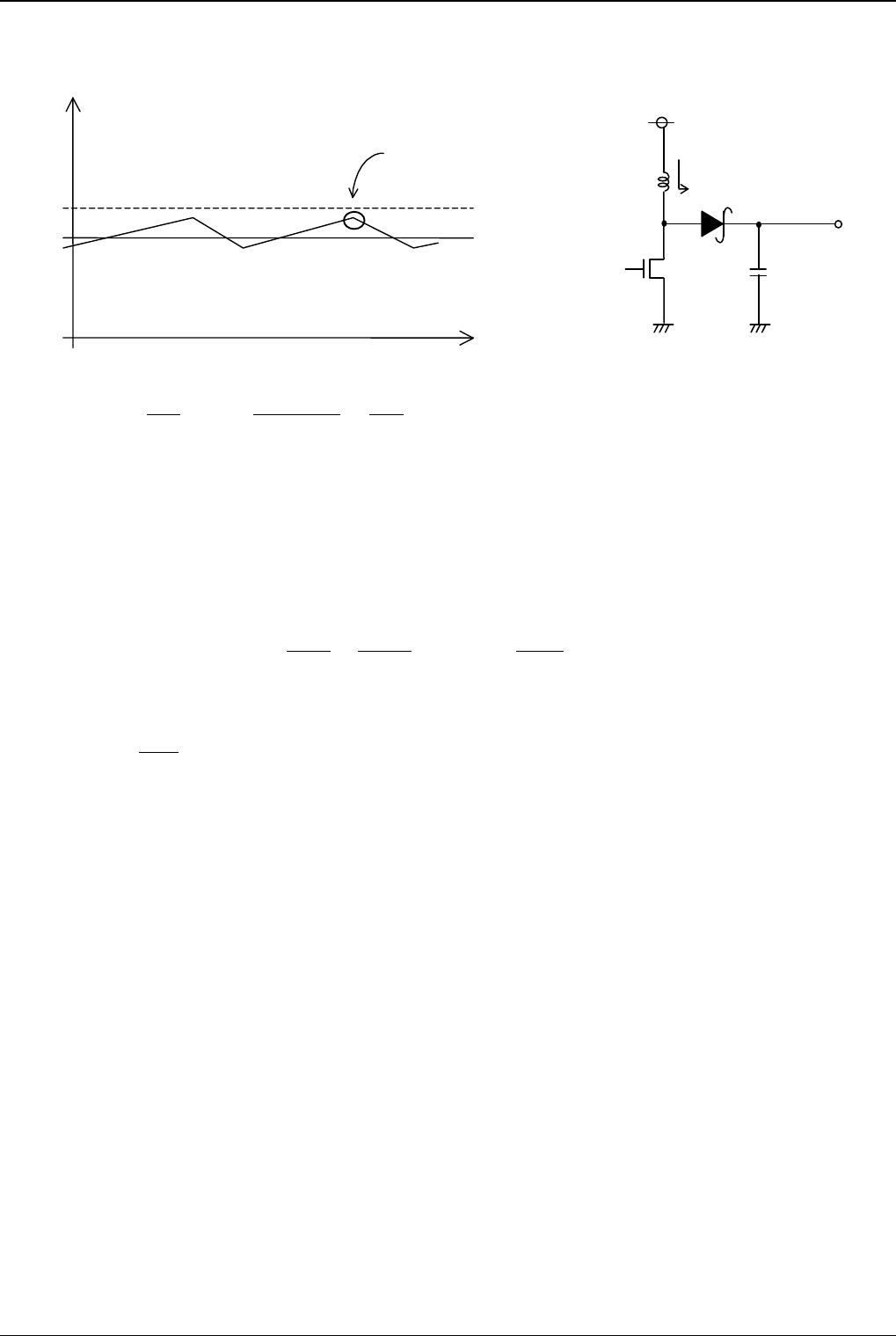

Fig. 28 Output Application Circuit Diagram

L

VCC

I

L

Vo

Co

IL

IINMAX + ∆IL should not reach

the rating value level

ILR

IINMAX

average current