AD7894

–6–

REV. 0

CONVERTER DETAILS

The AD7894 is a fast, 14-bit single supply A/D converter. It

provides the user with signal scaling, track/hold, A/D converter

and serial interface logic functions on a single chip. The A/D

converter section of the AD7894 consists of a conventional

successive-approximation converter based around an R-2R

ladder structure. The signal scaling on the AD7894-10 and

AD7894-3 allows the part to handle ±10 V and ±2.5 V input

signals respectively while operating from a single +5␣ V supply.

The AD7894-2 accepts an analog input range of 0 V to +2.5 V.

The part requires an external +2.5 V reference. The reference

input to the part is buffered on-chip. The AD7894 has two

operating modes, the high sampling mode and the “auto-sleep”

mode where the part automatically goes into sleep after the end

of conversion. These modes are discussed in more detail in the

Timing and Control Section.

A major advantage of the AD7894 is that it provides all of the

above functions in an 8-lead SOIC package. This offers the user

considerable space saving advantages over alternative solutions.

The AD7894 typically consumes only 20␣ mW, making it ideal

for battery powered applications.

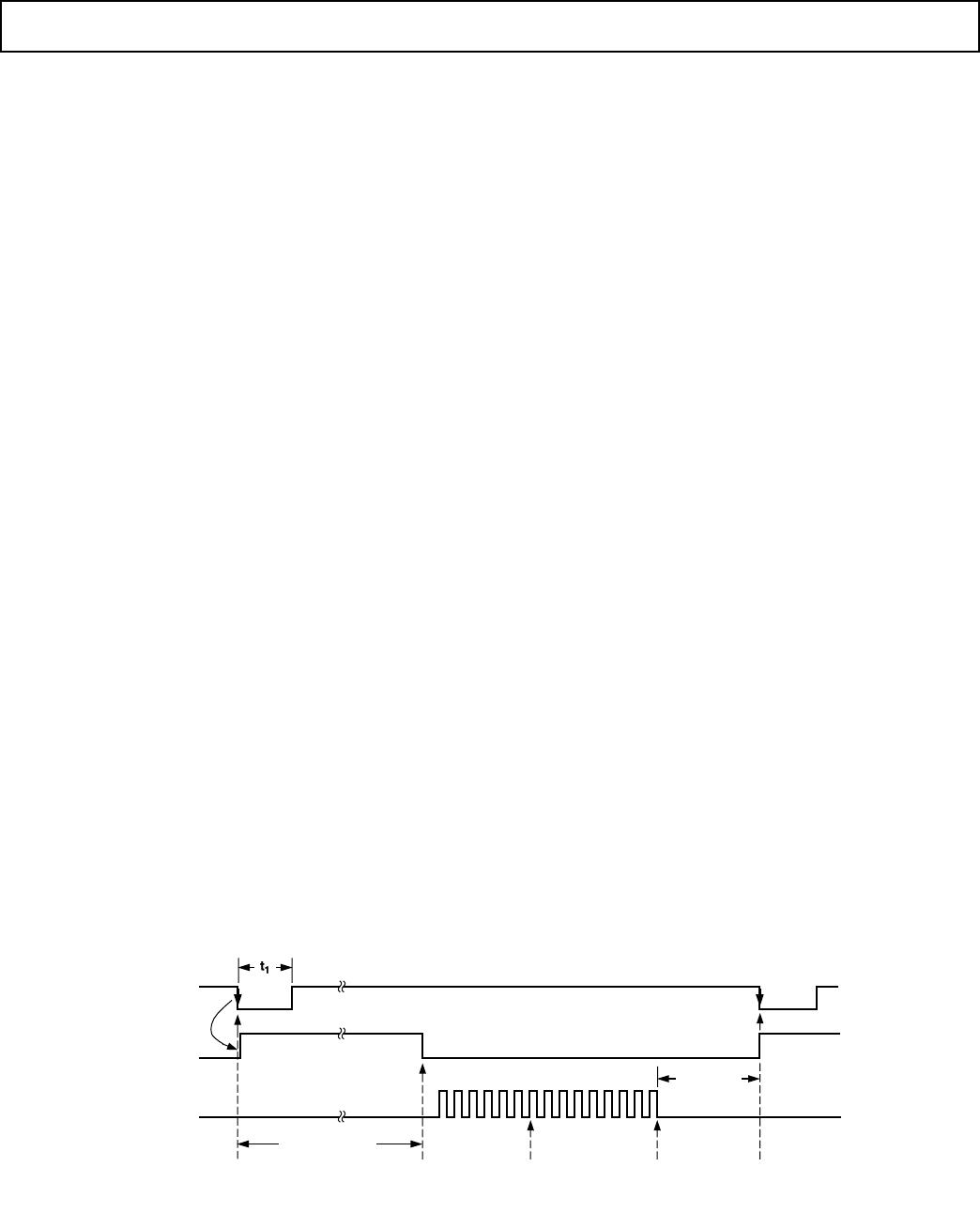

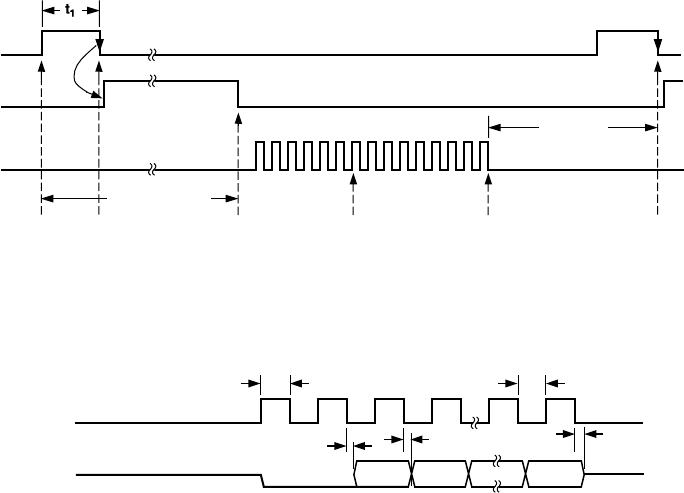

Conversion is initiated on the AD7894 by pulsing the CONVST

input. On the falling edge of CONVST, the on-chip track/hold

goes from track-to-hold mode and the conversion sequence is

started. The conversion clock for the part is generated internally

using a laser-trimmed clock oscillator circuit. Conversion time for

the AD7894 is 5␣ µs in the high sampling mode (10 µs for the auto

sleep mode), and the track/hold acquisition time is 0.35␣ µs. To

obtain optimum performance from the part, the read operation

should not occur during the conversion or during 250 ns prior

to the next conversion. This allows the part to operate at through-

put rates up to 160 kHz and achieve data sheet specifications.

CIRCUIT DESCRIPTION

Analog Input Section

The AD7894 is offered as three part types, the AD7894-10,

which handles a ±10 V input voltage range, the AD7894-3,

which handles input voltage range ±2.5 V and the AD7894-2,

which handles a 0␣ V to +2.5␣ V input voltage range.

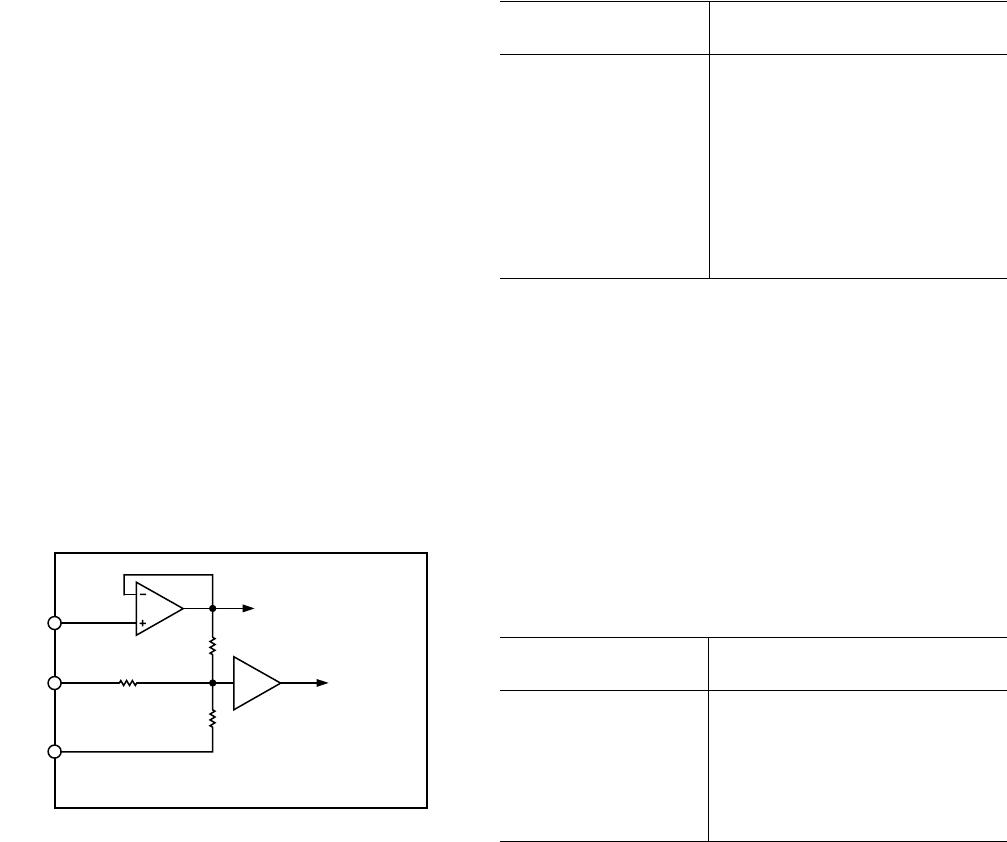

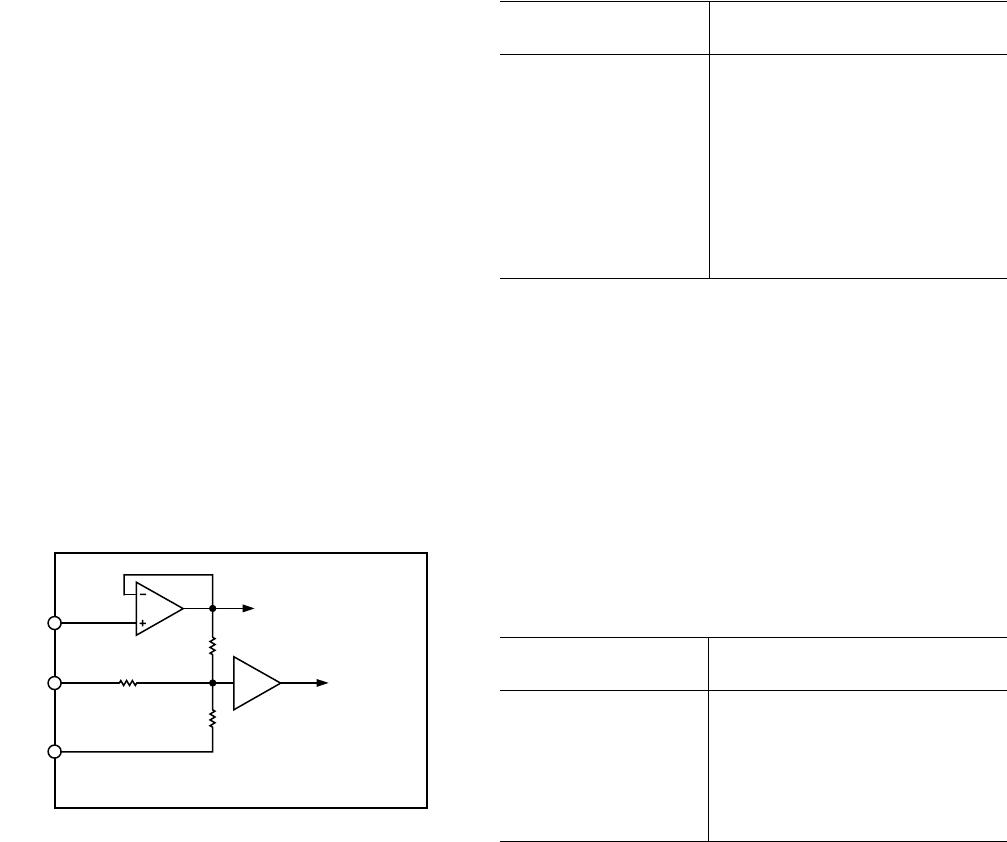

TRACK/

HOLD

AD7894-10/AD7894-3

REF IN

V

IN

GND

R1

R2

R3

TO ADC

REFERENCE

CIRCUITRY

TO INTERNAL

COMPARATOR

Figure 2. AD7894-10/AD7894-3 Analog Input Structure

Figure 2 shows the analog input section for the AD7894-10 and

AD7894-3. The analog input range of the AD7894-10 is ±10 V

and the analog input range for the AD7894-3 is ±2.5 V. This

input is benign, with no dynamic charging currents as the resis-

tor stage is followed by a high input impedance stage of the

track/hold amplifier. For the AD7894-10, R1 = 8 kΩ, R2 = 2 kΩ

and R3 = 2 kΩ. For the AD7894-3, R1 = R2 = 2 kΩ and R3

is open circuit. The current flowing in the analog input is di-

rectly related to the analog input voltage. The maximum input

current flows when the analog input is at negative full scale.

For the AD7894-10 and AD7894-3, the designed code transi-

tions occur on successive integer LSB values (i.e., 1 LSB, 2 LSBs,

3 LSBs . . .). Output coding is twos complement binary with

1 LSB = FS/16384. The ideal input/output transfer function for

the AD7894-10 and AD7894-3 is shown in Table I.

Table I. Ideal Input/Output Code Table for the AD7894-10/

AD7894-3

Digital Output

Analog Input

l

Code Transition

+FSR/2 – 1 LSB

2

011 . . . 110 to 011 . . . 111

+FSR/2 – 2 LSBs 011 . . . 101 to 011 . . . 110

+FSR/2 – 3 LSBs 011 . . . 100 to 011 . . . 101

GND + 1 LSB 000 . . . 000 to 000 . . . 001

GND 111 . . . 111 to 000 . . . 000

GND – 1 LSB 111 . . . 110 to 111 . . . 111

–FSR/2 + 3 LSBs 100 . . . 010 to 100 . . . 011

–FSR/2 + 2 LSBs 100 . . . 001 to 100 . . . 010

–FSR/2 + 1 LSB 100 . . . 000 to 100 . . . 001

NOTES

1

FSR is full-scale range = 20 V (AD7894-10) and = 5 V (AD7894-3) with

REF IN = +2.5 V.

2

1 LSB = FSR/16384 = 1.22 mV (AD7894-10) and 0.3 mV (AD7894-3) with

REF IN = +2.5 V.

The analog input section for the AD7894-2 contains no biasing

resistors and the V

IN

pin drives the input directly to the track/

hold amplifier. The analog input range is 0 V to +2.5 V into a

high impedance stage with an input current of less than 500␣ nA.

This input is benign, with no dynamic charging currents. Once

again, the designed code transitions occur on successive integer

LSB values. Output coding is straight (natural) binary with

1 LSB = FS/16384 = 2.5 V/16384 = 0.15 mV. Table II shows

the ideal input/output transfer function for the AD7894-2.

Table II. Ideal Input/Output Code Table for AD7894-2

Digital Output

Analog Input

1

Code Transition

+FSR – 1 LSB

2

111 . . . 110 to 111 . . . 111

+FSR – 2 LSB 111 . . . 101 to 111 . . . 110

+FSR – 3 LSB 111 . . . 100 to 111 . . . 101

GND + 3 LSB 000 . . . 010 to 000 . . . 011

GND + 2 LSB 000 . . . 001 to 000 . . . 010

GND + 1 LSB 000 . . . 000 to 000 . . . 001

NOTES

1

FSR is full-scale range and is 2.5 V for AD7894-2 with VREF = +2.5 V.

2

1 LSB = FSR/16384 and is 0.15 mV for AD7894-2 with VREF = +2.5 V.