Si595

6 Rev. 1.4

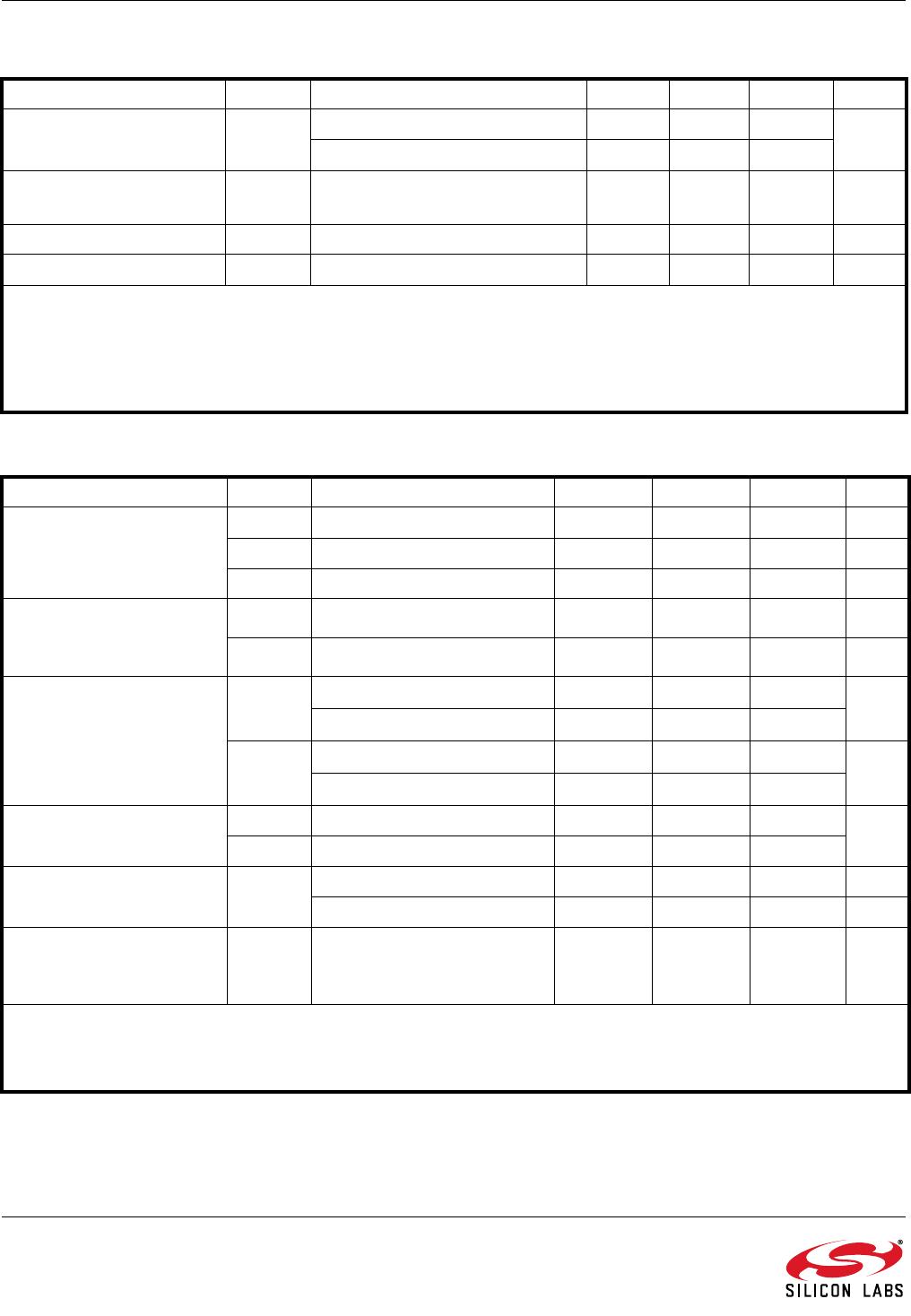

Table 8. Environmental Compliance and Package Information

Parameter Conditions/Test Method

Mechanical Shock MIL-STD-883, Method 2002

Mechanical Vibration MIL-STD-883, Method 2007

Solderability MIL-STD-883, Method 2003

Gross and Fine Leak MIL-STD-883, Method 1014

Resistance to Solder Heat MIL-STD-883, Method 2036

Contact Pads Gold over Nickel

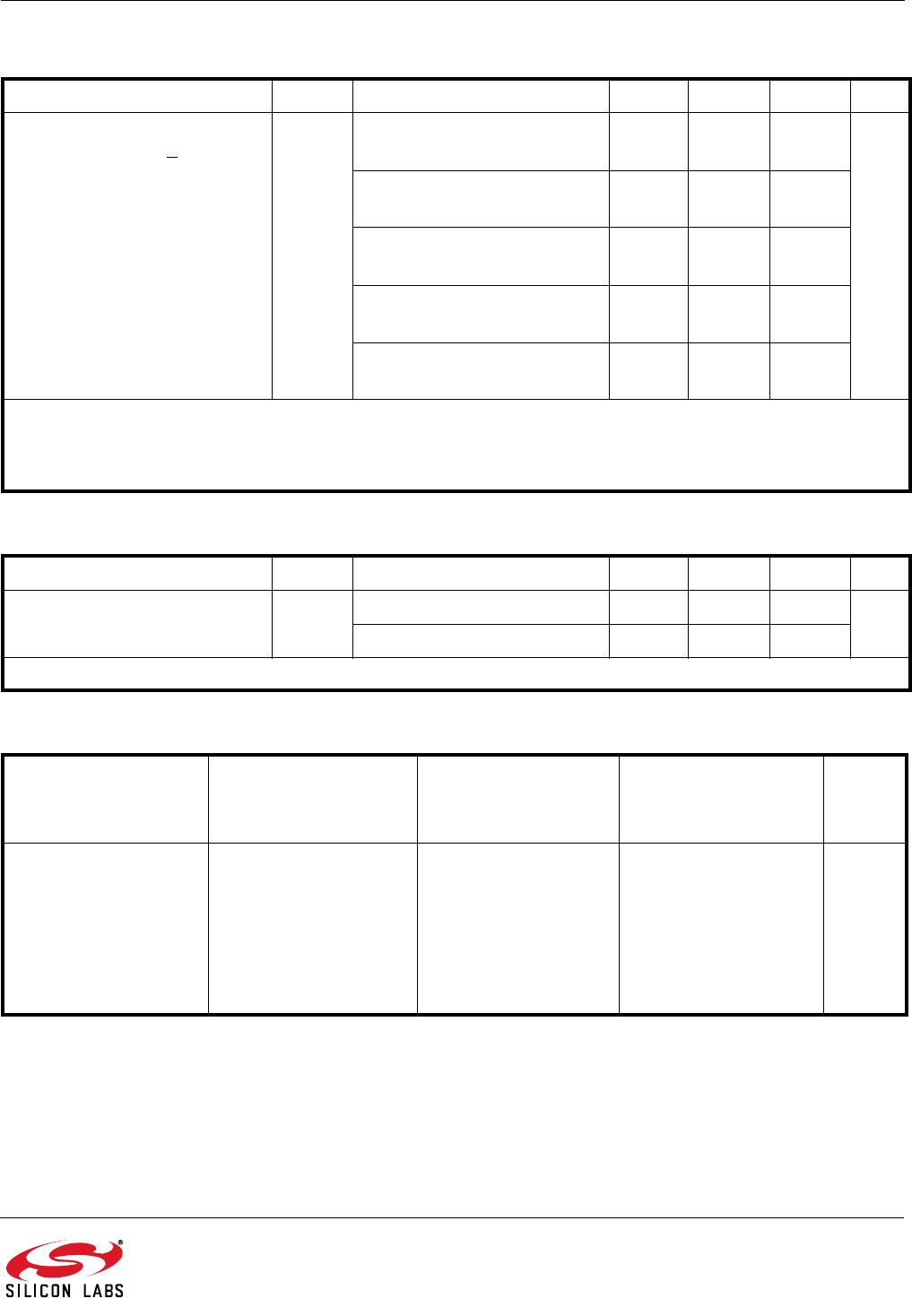

Table 9. Thermal Characteristics

(Typical values TA = 25 ºC, V

DD

=3.3V)

Parameter Symbol Test Condition Min Typ Max Unit

5x7mm, Thermal Resistance Junction to

Ambient

JA

Still Air — 84.6 — °C/W

5x7mm, Thermal Resistance Junction to

Case

JC

Still Air — 38.8 — °C/W

3.2x5mm, Thermal Resistance Junction to

Ambient

JA

Still Air — 31.1 — °C/W

3.2x5mm, Thermal Resistance Junction to

Case

JC

Still Air — 13.3 — °C/W

Ambient Temperature T

A

–40 — 85 °C

Junction Temperature T

J

——125°C

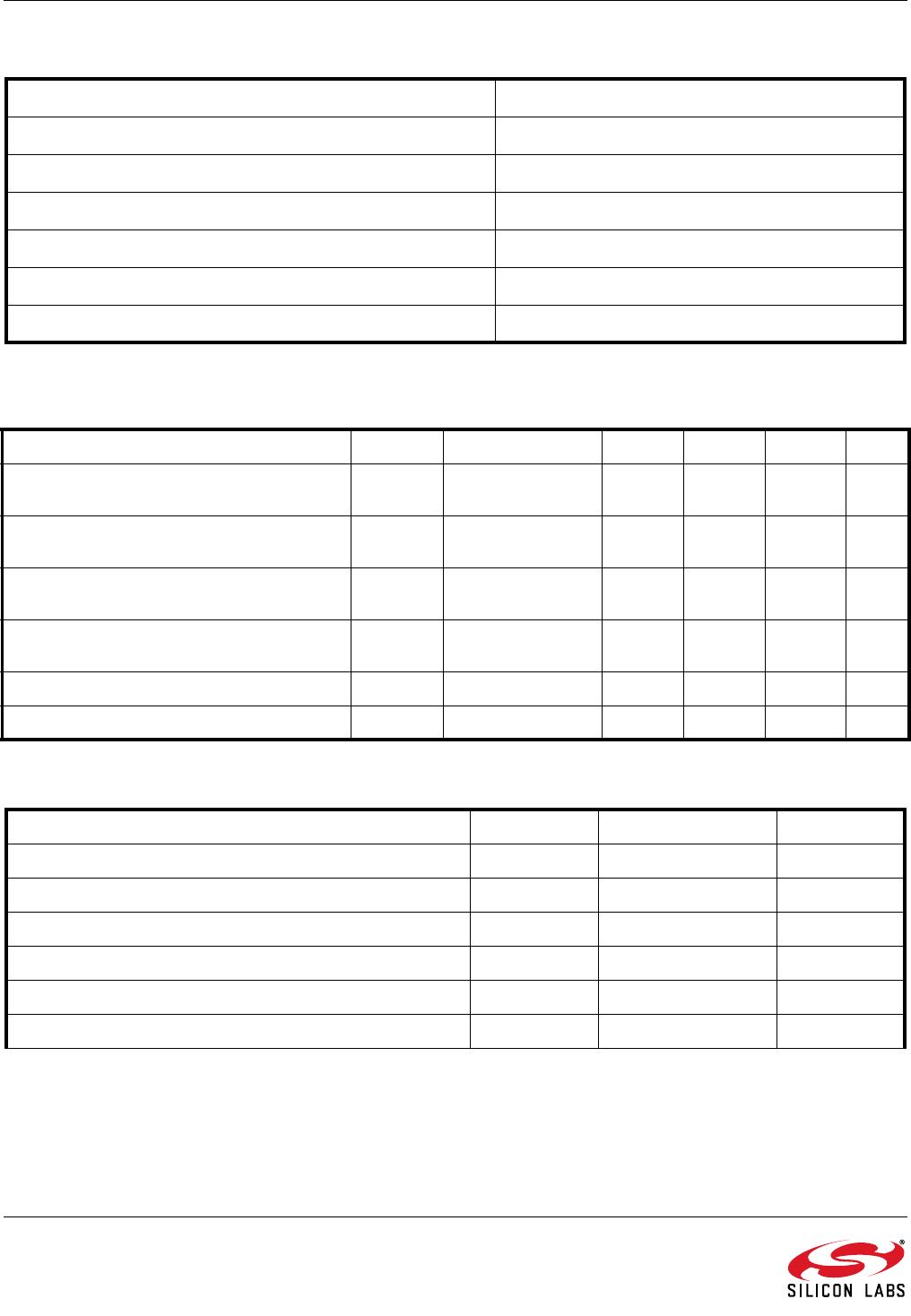

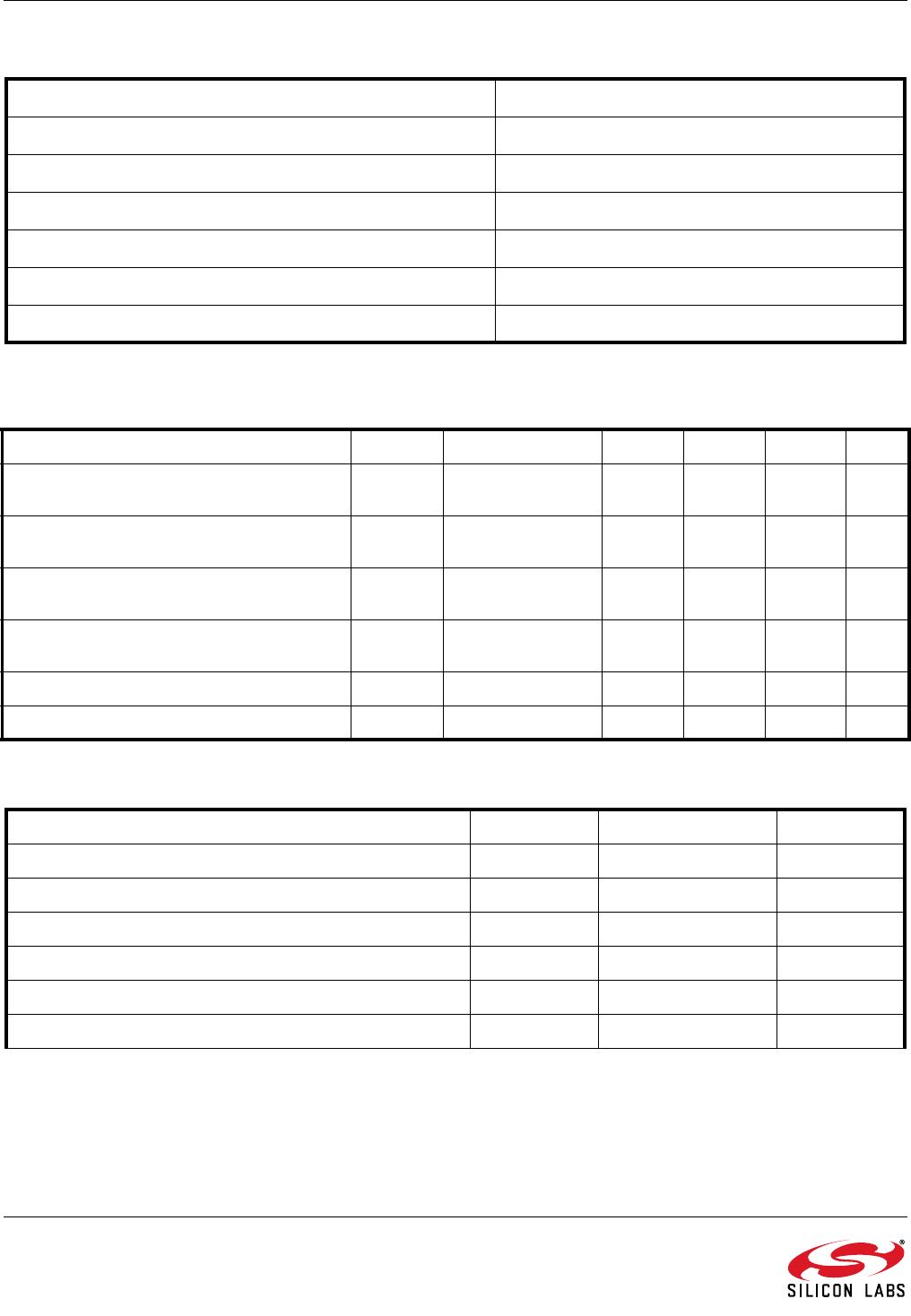

Table 10. Absolute Maximum Ratings

1

Parameter Symbol Rating Units

Maximum Operating Temperature T

AMAX

85 ºC

Supply Voltage V

DD

–0.5 to +3.8 V

Input Voltage V

I

–0.5 to V

DD

+ 0.3

Storage Temperature T

S

–55 to +125 ºC

ESD Sensitivity (HBM, per JESD22-A114) ESD 2500 V

Soldering Temperature (Pb-free profile)

2

T

PEAK

260 ºC