ADuM4120/ADuM4120-1 Data Sheet

Rev. 0 | Page 14 of 17

OUTPUT LOAD CHARACTERISTICS

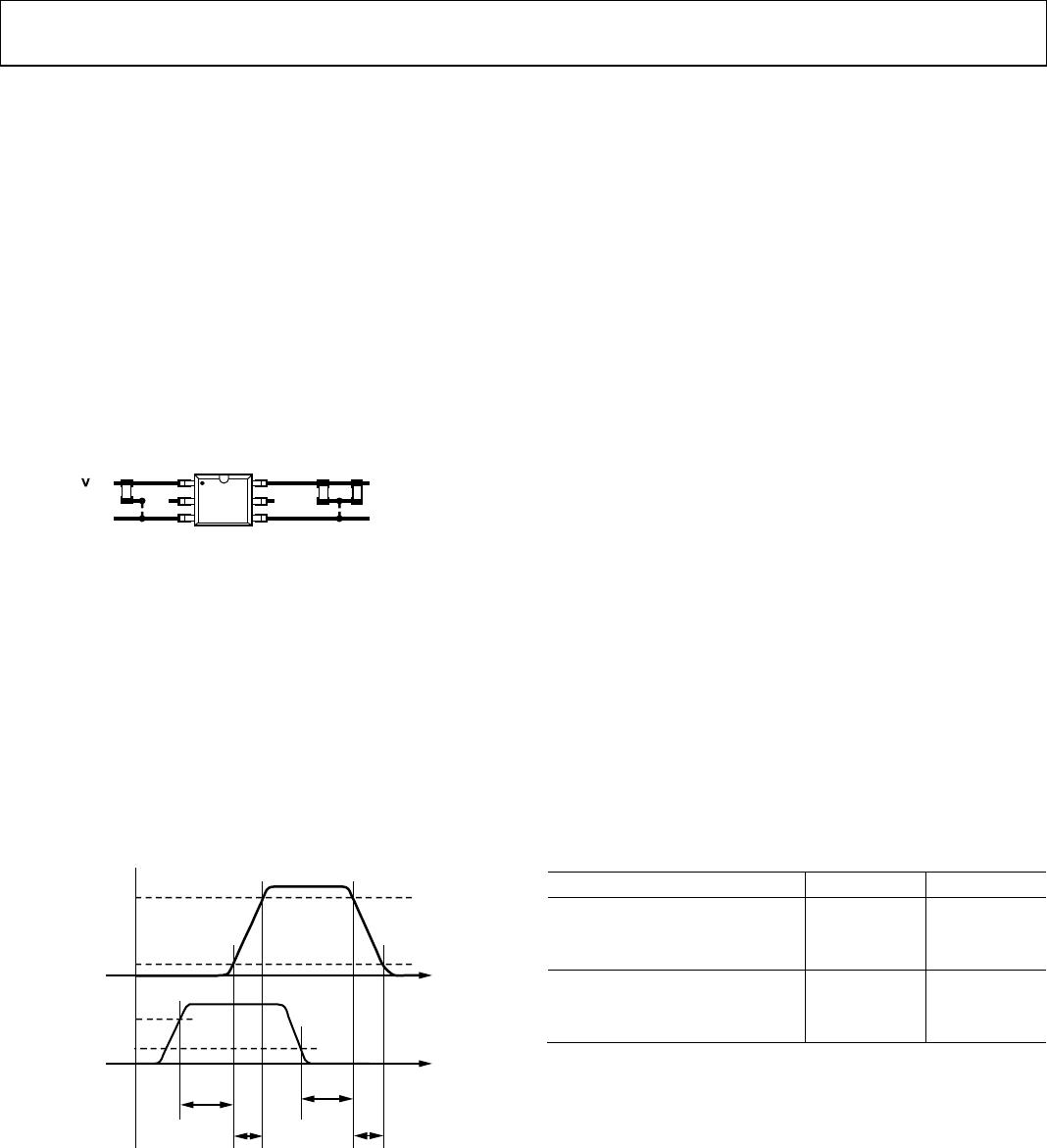

The ADuM4120/ADuM4120-1 output signals depend on the

characteristics of the output load, which is typically an N-channel

MOSFET. The driver output response to an N-channel MOSFET

load can be modeled with a switch output resistance (R

SW

), an

inductance due to the PCB trace (L

TRACE

), a series gate resistor

(R

GATE

), and a gate to source capacitance (C

GS

), as shown in

Figure 23.

R

SW

is the switch resistance of the internal ADuM4120/

ADuM4120-1 driver output, which is about 1.5 Ω. R

GATE

is the intrinsic gate resistance of the MOSFET and any external

series resistance. A MOSFET that requires a 4 A gate driver has

a typical intrinsic gate resistance of about 1 Ω and a gate to source

capacitance, C

GS

, of between 2 nF and 10 nF. L

TRACE

is the induct-

ance of the PCB trace, typically a value of 5 nH or less for a well

designed layout with a very short and wide connection from the

ADuM4120/ADuM4120-1 output to the gate of the MOSFET.

The following equation defines the Q factor of the resistor

inductor capacitor (RLC) circuit, which indicates how the

ADuM4120/ADuM4120-1 output responds to a step change.

For a well damped output, Q is less than one. Adding a series

gate resistance dampens the output response.

GS

TRACE

GATE

SW

C

L

RR

Q

)(

1

In Figure 4 and Figure 6, the ADuM4120/ADuM4120-1 output

waveforms for a 15 V output are shown for a C

GS

value of 2 nF

and 5 resistance. The ringing of the output in Figure 5 and

Figure 7 with C

GS

of 2 nF and no external resistor has a

calculated Q factor of 1.5, where less than one is desired for

adequate damping to prevent overshoot.

Output ringing can be reduced by adding a series gate resistance

to dampen the response. For applications using a 1 nF or less

load, it is recommended to add a series gate resistor of about

5 Ω. As shown in Figure 23, R

GATE

is 5 Ω, which yields a calculated

Q factor of about 0.7 which is well damped

ADuM4120/

ADuM4120-1

V

IN

V

OUT

R

SW

R

GATE

C

GS

L

TRACE

V

15493-123

Figure 23. RLC Model of the Gate of an N-Channel MOSFET

POWER DISSIPATION

During the driving of a MOSFET or IGBT gate, the driver must

dissipate power. This power is significant and can lead to TSD if

considerations are not made. The gate of an IGBT can be

roughly simulated as a capacitive load. With this value, the

estimated total power dissipation, P

DISS

, in the system due to

switching action is given by the following equation:

P

DISS

= C

EST

× (V

DD2

− GND

2

)

2

× fs

where:

C

EST

= C

ISS

× 5.

fs is the switching frequency of IGBT.

This power dissipation is shared between the internal on

resistances of the internal gate driver switches, and the external

gate resistances, R

GON

and R

GOFF

. The ratio of the internal gate

resistances to the total series resistance allows the calculation of

losses seen within the ADuM4120/ADuM4120-1 chip.

P

DISS_ADuM4120/ADuM4120-1

= P

DISS

× 0.5((R

DSON_P

/(R

GON

+ R

DSON_P

)) +

(R

DSON_N

/(R

GOFF

+ R

DSON_N

))

Taking this power dissipation found inside the chip and

multiplying it by the θ

JA

gives the rise above ambient temperature

that the ADuM4120/ADuM4120-1 experiences.

T

ADuM4120/ADuM4120-1

= θ

JA

× P

DISS_ADuM4120

+ T

A

For the device to remain within specification, T

ADUM4120

cannot

exceed 125°C. If T

ADuM4120

exceeds the thermal shutdown (TSD),

rising edge, the device enters TSD and the output remains low

until the TSD falling edge is crossed.

DC CORRECTNESS AND MAGNETIC FIELD IMMUNITY

The ADuM4120/ADuM4120-1 is resistant to external magnetic

fields. The limitation on the ADuM4120/ADuM4120-1

magnetic field immunity is set by the condition in which

induced voltage in the transformer receiving coil is sufficiently

large to either falsely set or reset the decoder. The following

analysis defines the conditions under which a false reading

condition can occur. The 2.3 V operating condition of the

ADuM4120/ADuM4120-1 is examined because it represents

the most susceptible mode of operation.

100

10

1

0.1

0.01

0.001

1k 10k 100k 1M 10M 100M

MAXIMUM ALLOWABLE MAGNETIC FLUX

DENSITY (kgauss)

MAGNETIC FIELD FREQUENCY (Hz)

15493-021

Figure 24. Maximum Allowable External Magnetic Flux Density