NBC12429, NBC12429A

http://onsemi.com

4

The following gives a brief description of the functionality of the NBC12429 and NBC12429A Inputs and Outputs. Unless

explicitly stated, all inputs are CMOS/TTL compatible with either pullup or pulldown resistors. The PECL outputs are capable

of driving two series terminated 50 W transmission lines on the incident edge.

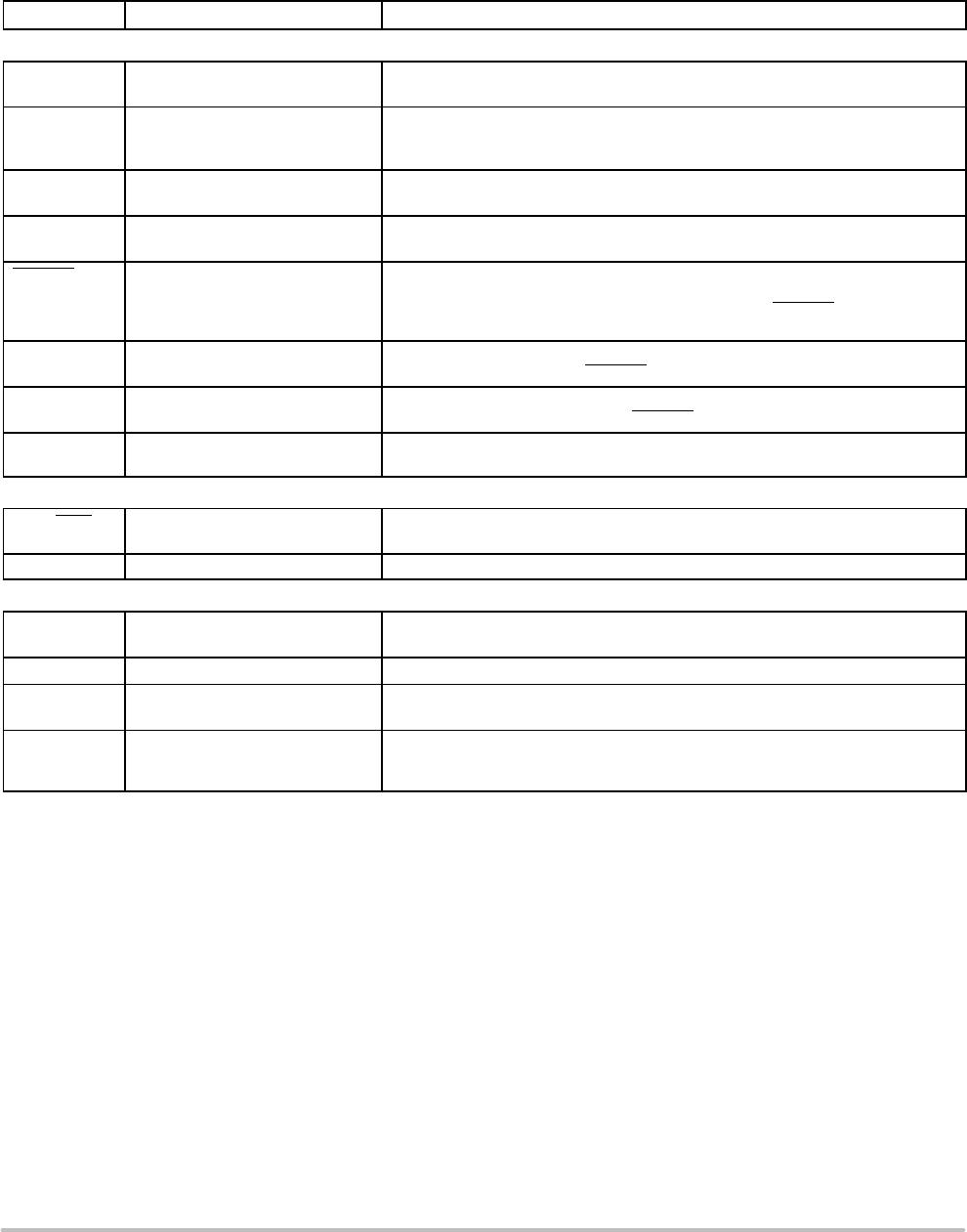

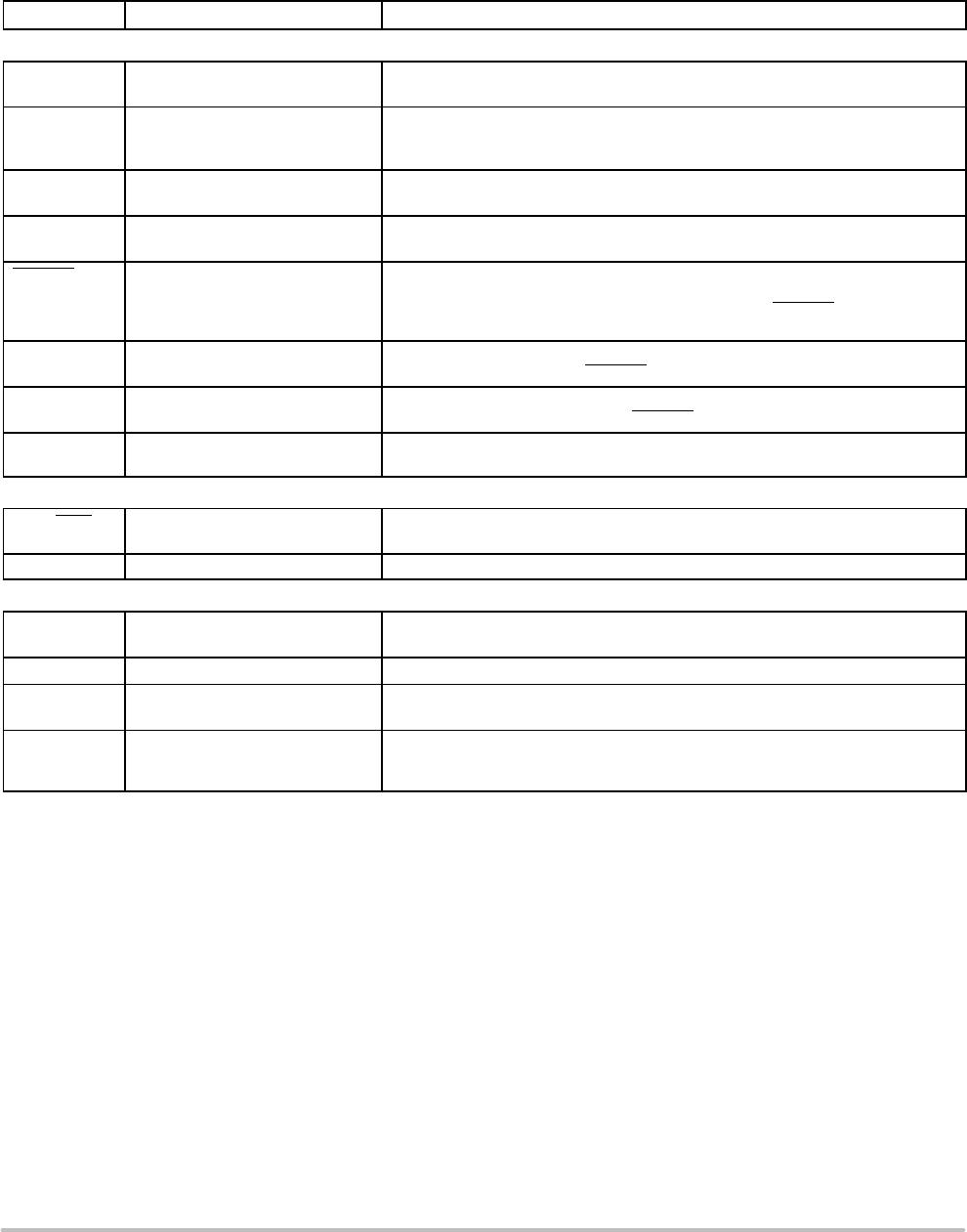

Table 3. PIN FUNCTION DESCRIPTION

Pin Name Function Description

INPUTS

XTAL1, XTAL2

Crystal Inputs These pins form an oscillator when connected to an external series−resonant

crystal.

S_LOAD* CMOS/TTL Serial Latch Input

(Internal Pulldown Resistor)

This pin loads the configuration latches with the contents of the shift registers. The

latches will be transparent when this signal is HIGH; thus, the data must be stable

on the HIGH−to−LOW transition of S_LOAD for proper operation.

S_DATA* CMOS/TTL Serial Data Input

(Internal Pulldown Resistor)

This pin acts as the data input to the serial configuration shift registers.

S_CLOCK* CMOS/TTL Serial Clock Input

(Internal Pulldown Resistor)

This pin serves to clock the serial configuration shift registers. Data from S_DATA

is sampled on the rising edge.

P_LOAD** CMOS/TTL Parallel Latch Input

(Internal Pullup Resistor)

This pin loads the configuration latches with the contents of the parallel inputs.

The latches will be transparent when this signal is LOW; therefore, the parallel

data must be stable on the LOW−to−HIGH transition of P_LOAD

for proper opera-

tion.

M[8:0]** CMOS/TTL PLL Loop Divider

Inputs (Internal Pullup Resistor)

These pins are used to configure the PLL loop divider. They are sampled on the

LOW−to−HIGH transition of P_LOAD

. M[8] is the MSB, M[0] is the LSB.

N[1:0]** CMOS/TTL Output Divider Inputs

(Internal Pullup Resistor)

These pins are used to configure the output divider modulus. They are sampled

on the LOW−to−HIGH transition of P_LOAD

.

OE** CMOS/TTL Output Enable Input

(Internal Pullup Resistor)

Active HIGH Output Enable. The Enable is synchronous to eliminate possibility of

runt pulse generation on the F

OUT

output.

OUTPUTS

F

OUT

, F

OUT

PECL Differential Outputs These differential, positive−referenced ECL signals (PECL) are the outputs of the

synthesizer.

TEST CMOS/TTL Output The function of this output is determined by the serial configuration bits T[2:0].

POWER

V

CC

Positive Supply for the Logic The positive supply for the internal logic and output buffer of the chip, and is con-

nected to +3.3 V or +5.0 V.

PLL_V

CC

Positive Supply for the PLL This is the positive supply for the PLL and is connected to +3.3 V or +5.0 V.

GND Negative Power Supply These pins are the negative supply for the chip and are normally all connected to

ground.

− Exposed Pad for QFN−32 only The Exposed Pad (EP) on the QFN−32 package bottom is thermally connected to

the die for improved heat transfer out of package. The exposed pad must be at-

tached to a heat−sinking conduit. The pad is electrically connected to GND.

* When left Open, these inputs will default LOW.

** When left Open, these inputs will default HIGH.