14

82C54

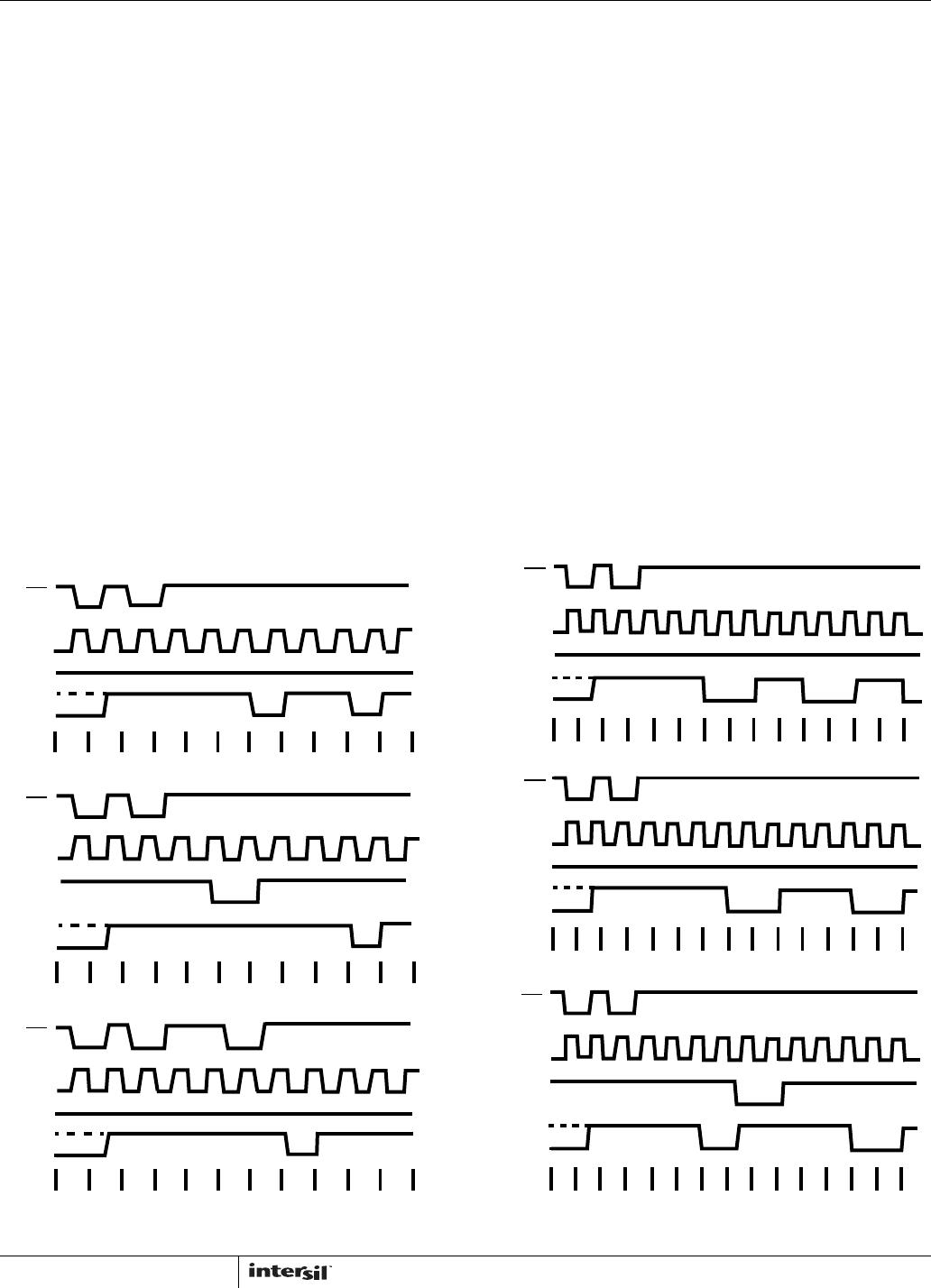

Mode 3 Is Implemented As Follows

EVEN COUNTS - OUT is initially high. The initial count is

loaded on one CLK pulse and then is decremented by two

on succeeding CLK pulses. When the count expires, OUT

changes value and the Counter is reloaded with the initial

count. The above process is repeated indefinitely.

ODD COUNTS - OUT is initially high. The initial count is loaded

on one CLK pulse, decremented by one on the next CLK pulse,

and then decremented by two on succeeding CLK pulses.

When the count expires, OUT goes low and the Counter is

reloaded with the initial count. The count is decremented by

three on the next CLK pulse, and then by two on succeeding

CLK pulses. When the count expires, OUT goes high again and

the Counter is reloaded with the initial count. The above

process is repeated indefinitely. So for odd counts, OUT will be

high for (N + 1)/2 counts and low for (N - 1)/2 counts.

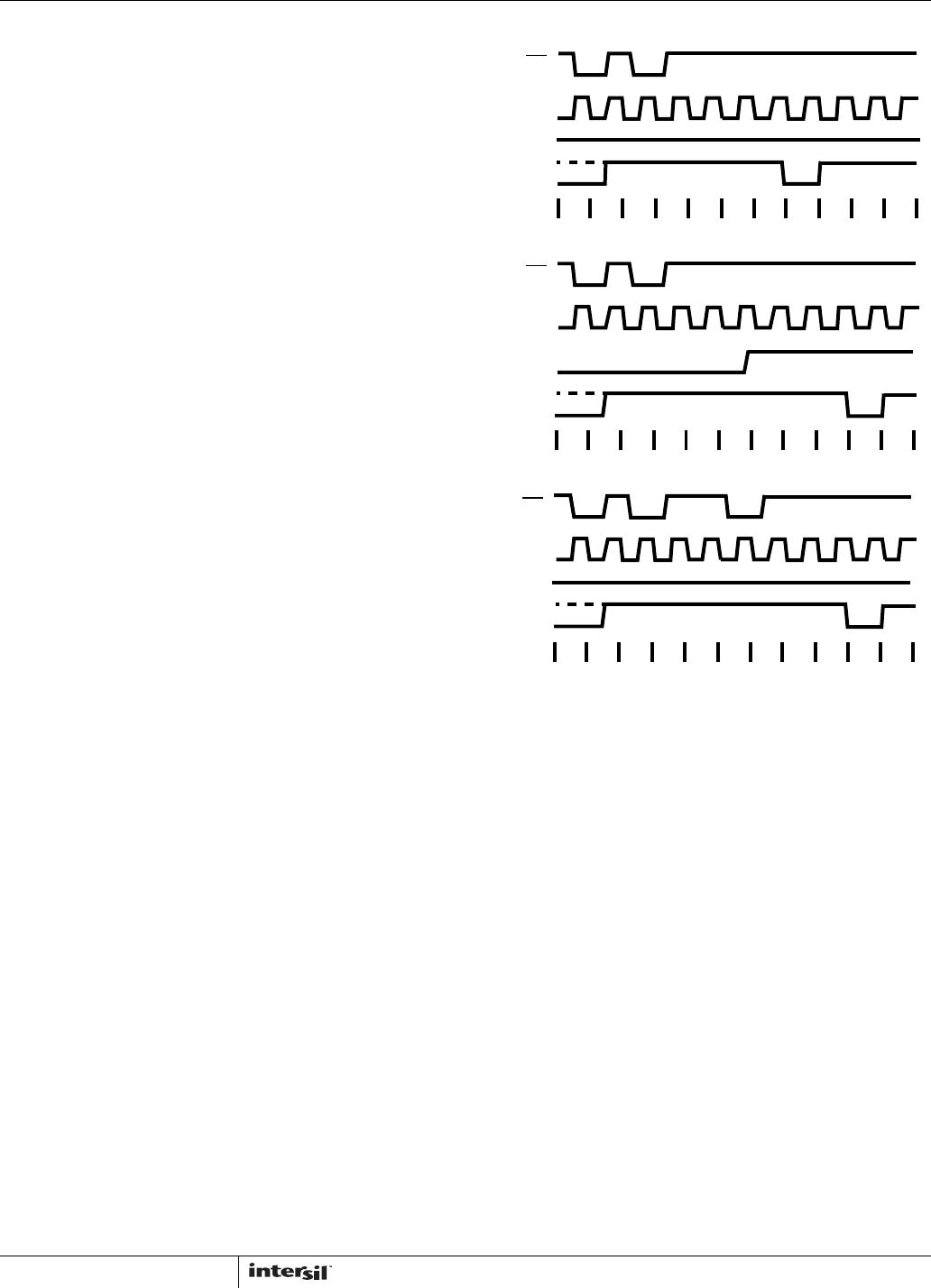

MODE 4: SOFTWARE TRIGGERED MODE

OUT will be initially high. When the initial count expires, OUT

will go low for one CLK pulse then go high again. The

counting sequence is “Triggered” by writing the initial count.

GATE = 1 enables counting; GATE = 0 disables counting.

GATE has no effect on OUT.

After writing a Control Word and initial count, the Counter will be

loaded on the next CLK pulse. This CLK pulse does not

decrement the count, so for an initial count of N, OUT does not

strobe low until N + 1 CLK pulses after the initial count is

written.

If a new count is written during counting, it will be loaded on

the next CLK pulse and counting will continue from the new

count. If a two-byte count is written, the following happens:

1. Writing the first byte has no effect on counting.

2. Writing the second byte allows the new count to be

loaded on the next CLK pulse.

This allows the sequence to be “retriggered” by software. OUT

strobes low N + 1 CLK pulses after the new count of N is

written.

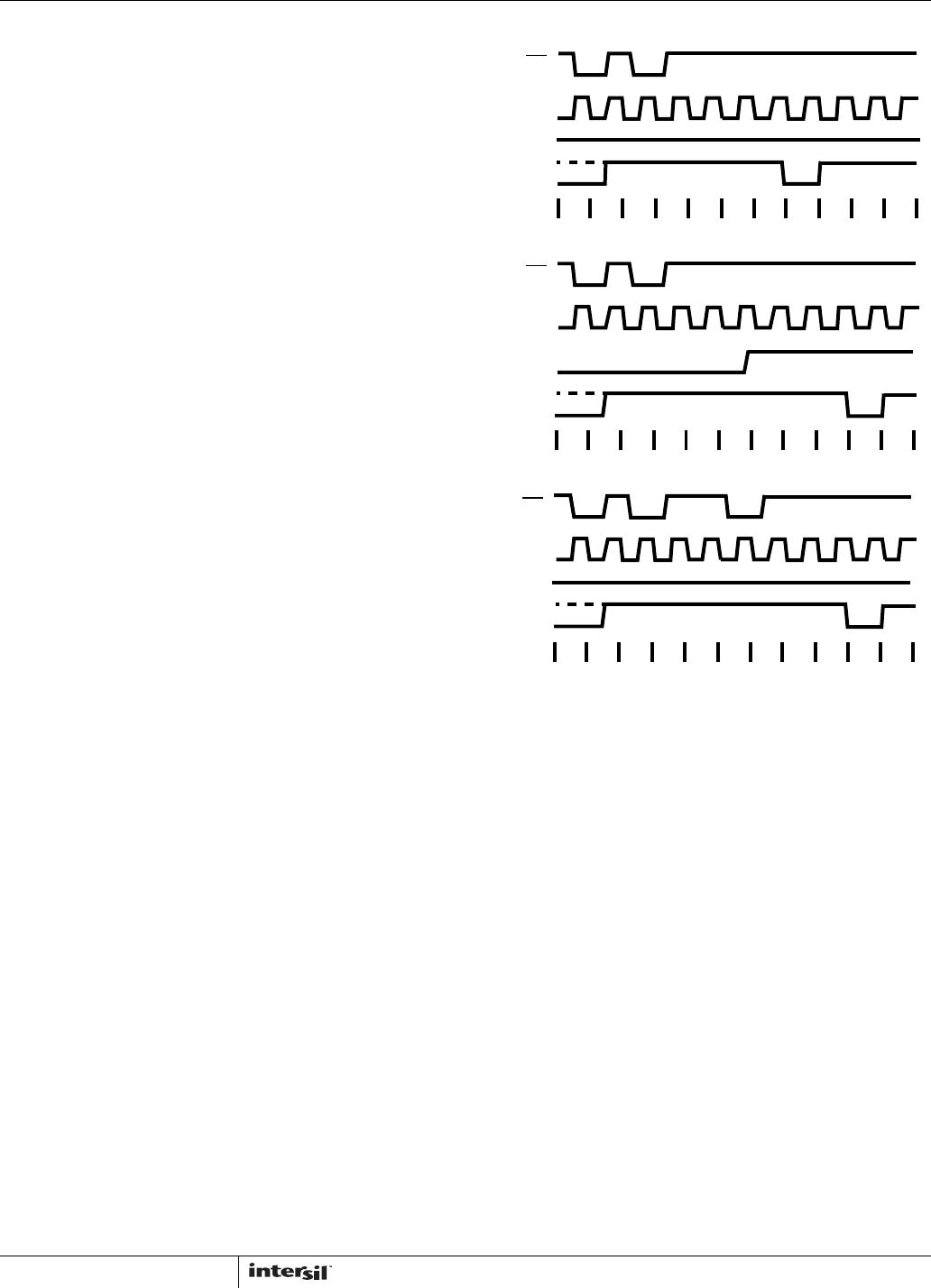

MODE 5: HARDWARE TRIGGERED STROBE

(RETRIGGERABLE)

OUT will initially be high. Counting is triggered by a rising

edge of GATE. When the initial count has expired, OUT will

go low for one CLK pulse and then go high again.

After writing the Control Word and initial count, the counter

will not be loaded until the CLK pulse after a trigger. This

CLK pulse does not decrement the count, so for an initial

count of N, OUT does not strobe low until N + 1 CLK pulses

after trigger.

A trigger results in the Counter being loaded with the initial

count on the next CLK pulse. The counting sequence is

triggerable. OUT will not strobe low for N + 1 CLK pulses

after any trigger GATE has no effect on OUT.

If a new count is written during counting, the current counting

sequence will not be affected. If a trigger occurs after the

new count is written but before the current count expires, the

NNNN

0

2

0

1

0

0

FF

FF

FF

FE

FF

FD

0

3

WR

CLK

GATE

OUT

CW = 18 LSB = 3

WR

CLK

GATE

OUT

WR

CLK

GATE

OUT

CW = 18 LSB = 3

CW = 18 LSB = 3

NNN

0

3

0

2

0

1

0

2

0

1

0

0

FF

FF

NN NN

0

3

0

3

0

2

0

1

0

0

FF

FF

0

3

LSB = 2

N

FIGURE 13. MODE 4