List of figures VND5N07-E

4/22 DocID025077 Rev 2

List of figures

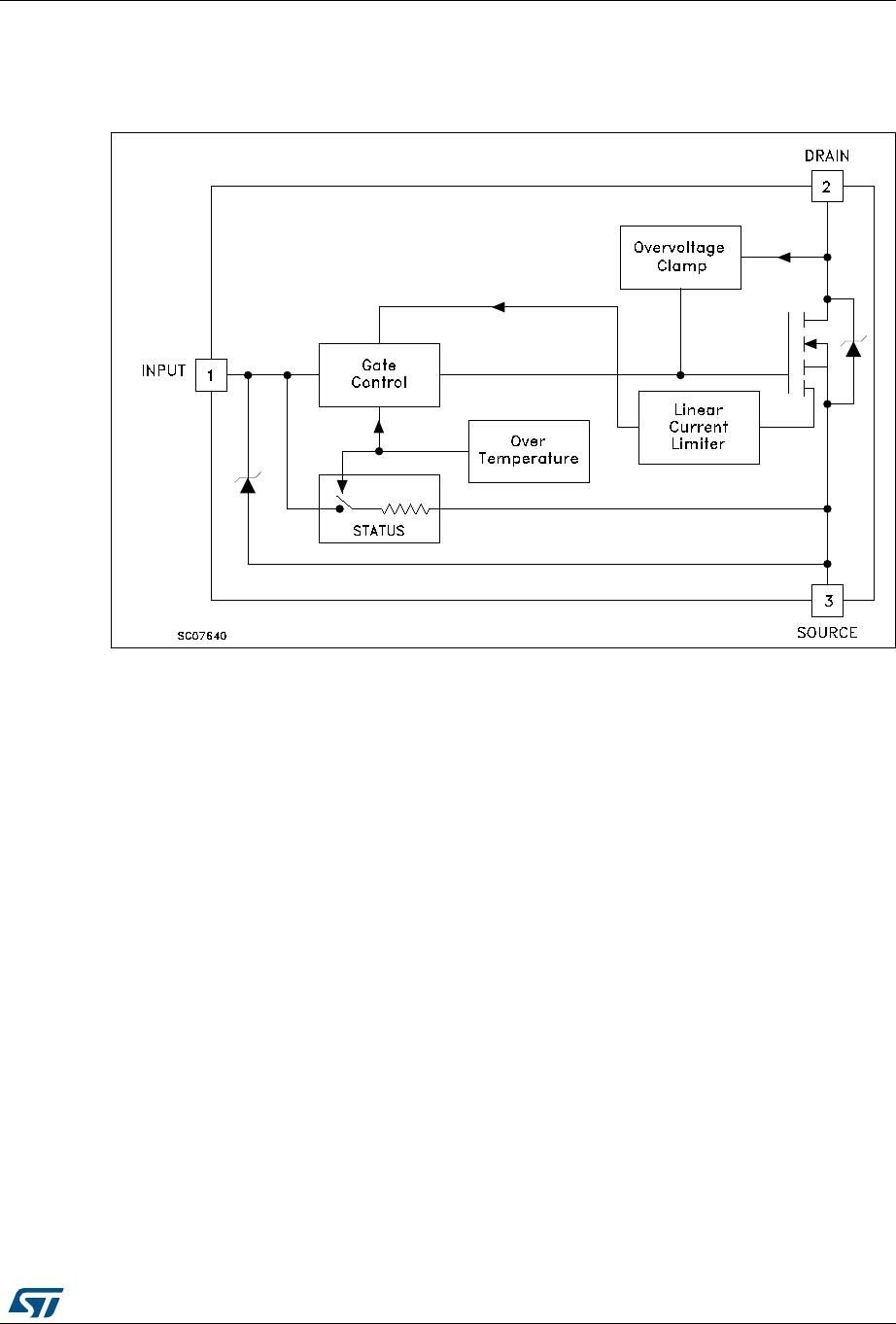

Figure 1. Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. Switching time test circuit for resistive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 3. Test circuit for diode recovery times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 4. Unclamped inductive load test circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 5. Input charge test circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 6. Unclamped inductive waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 7. Switching waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 8. Thermal impedance for DPAK / IPAK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 9. Source-drain diode forward characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 10. Static drain-source on resistance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 11. Derating curve . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 12. Static drain-source on resistance vs. input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 13. Normalized on resistance Vs temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 14. Transconductance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 15. Static drain-source on resistance Vs. Id . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 16. Switching time resistive load. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 17. Turn-on current slope (V

IN

= 10 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 18. Turn-on current slope (V

IN

= 5 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 19. Input voltage vs. input charge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 20. Turn-off drain source voltage slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 21. Turn-off drain-source voltage slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 22. Capacitance variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 23. Switching time resistive load. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 24. Step response current limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 25. Output characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 26. Normalized on resistance vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 27. Normalized input threshold voltage vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 28. Normalized current limit vs. junction temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 29. DPAK package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 30. IPAK mechanical data and package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20