AD734

Rev. E | Page 13 of 20

At least one of the two inputs of any pair must be provided with

a dc path (usually to ground). The careful selection of ground

returns is important in realizing the full accuracy of the AD734.

The Z2 pin is normally connected to the load ground, which can be

remote in some cases. It can also be used as an optional summing

input (see Equation 3 and Equation 4) having a nominal FS

input of ±10 V and the full 10 MHz bandwidth.

In applications where high absolute accuracy is essential, the

scaling error caused by the finite resistance of the signal source(s)

may be troublesome; for example, a 50 Ω source resistance at

just one input introduces a gain error of −0.1%; if both the X

and Y inputs are driven from 50 Ω sources, the scaling error in

the product is −0.2%. If the source resistances are known, this

gain error can be completely compensated by including the

appropriate resistance (50 Ω or 100 Ω, respectively, in the

preceding cases) between the output, W (Pin 12), and the Z1

feedback input (Pin 11). If Rx is the total source resistance

associated with the X1 and X2 inputs, and Ry is the total source

resistance associated with the Y1 and Y2 inputs, and neither Rx

nor Ry exceeds 1 kΩ, a resistance of Rx + Ry in series with

Pin Z1 provides the required gain restoration.

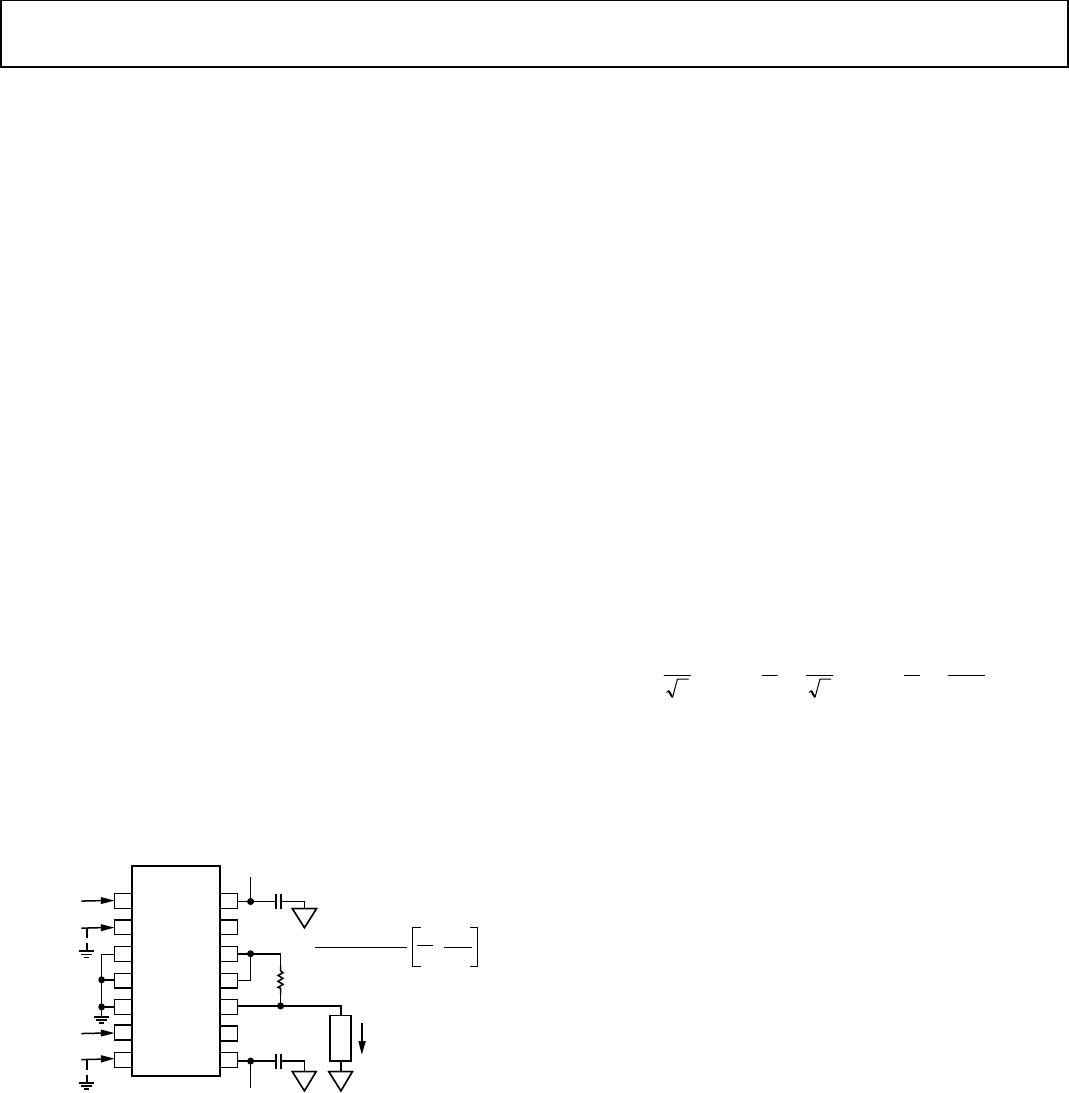

Pin 9 (ER) and Pin 13 (DD) should be left unconnected in this

application. The U inputs (Pin 3, Pin 4, and Pin 5) are shown

connected to ground; they can alternatively be connected to

VN, if desired. In applications where Pin 2 (X2) happens to

be driven with a high amplitude, high frequency signal, the

capacitive coupling to the denominator control circuitry via

an ungrounded Pin 3 can cause high frequency distortion.

However, the AD734 can be operated without modification in

an

AD534 socket and these three pins left unconnected with the

preceding caution noted.

AD734

X1

1

X2

2

U0

3

U1

4

U2

5

VP

14

DD

NC

NC

13

W

12

Z1

11

Z2

10

Y2

7

ER

9

VN

8

Y1

6

L

L

X INPUT

±10V FS

Y INPUT

±10V FS

+15

R

S

–15V

0.1µF

0.1µF

L

LOAD

±10mA MAX FS

±10V MAXIMUM

LOAD VOLTAGE

I

W

I

W

=

(X

1

– X

2

)(Y

1

–Y

2

)

10V

+

1

R

S

1

50kΩ

0827-008

Figure 25. Conversion of Output to a Current

Current Output

It may occasionally be desirable to convert the output voltage to

a current. In correlation applications, for example, multiplication is

followed by integration; if the output is in the form of a current,

a simple grounded capacitor can perform this function. Figure 25

shows how this can be achieved. The op amp forces the voltage

across Z1 and Z2, and thus across the resistor, RS, to be the

product XY/U. Note that the input resistance of the Z interface

is in shunt with RS, which must be calculated accordingly.

The smallest FS current is simply ±10 V/50 kΩ, or ±200 μA,

with a tolerance of about 20%. To guarantee a 1% conversion

tolerance without adjustment, R

S

must be less than 2.5 kΩ. The

maximum full-scale output current should be limited to about

±10 mA (thus, R

S

= 1 kΩ). This concept can be applied to all

connection modes, with the appropriate choice of terminals.

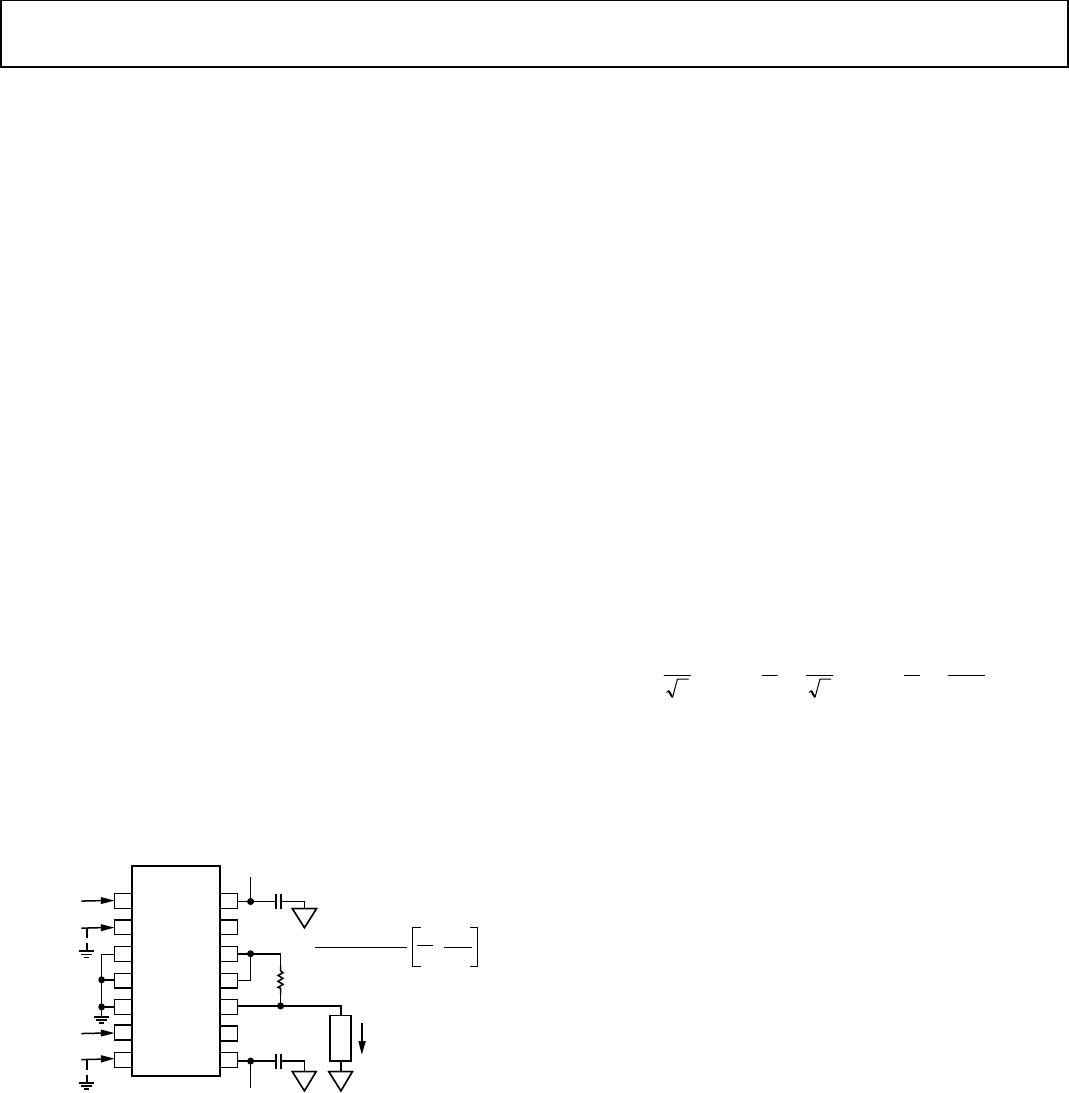

Squaring and Frequency-Doubling

Squaring of an input signal, E, is achieved by connecting the X

and Y inputs in parallel; the phasing can be chosen to produce

an output of E

2

/U or −E

2

/U as desired. The input can have

either polarity, but the basic output is either always positive or

negative; as for multiplication, the Z2 input can be used to add a

further signal to the output.

When the input is a sine wave, a squarer behaves as a frequency

doubler, because

(Esinwt)

2

= E

2

(1 − cos2wt)/2 (8)

Equation 8 shows a dc term at the output, which varies strongly

with the amplitude of the input, E. This dc term can be avoided

using the connection shown in Figure 26, where an RC network

is used to generate two signals whose product has no dc term.

The output is

⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

⎭

⎬

⎫

⎩

⎨

⎧

⎟

⎠

⎞

⎜

⎝

⎛

−

⎭

⎬

⎫

⎩

⎨

⎧

⎟

⎠

⎞

⎜

⎝

⎛

+=

V10

1

4

sin

2

4

sin

2

4

ππ

wt

E

wt

E

W

(9)

for w = 1/CR1, which is just

W = E

2

(cos2wt)/(10 V) (10)

which has no dc component. To restore the output to ±10 V

when E = 10 V, a feedback attenuator with an approximate ratio

of 4 is used between W and Z1; this technique can be used

wherever it is desired to achieve a higher overall gain in the

transfer function.

The values of R3 and R4 include additional compensation for the

effects of the 50 kΩ input resistance of all three interfaces; R2 is

included for a similar reason. These resistor values should not

be altered without careful calculation of the consequences. With

the values shown, the center frequency f

0

is 100 kHz for C =

1 nF. The amplitude of the output is only a weak function of

frequency; the output amplitude is 0.5% too low at f = 0.9f

0

and

f = 1.1f

0

. The cross-connection is simply to produce the cosine

output with the sign shown in Equation 10; however, the sign in

this case is rarely important.