AD734

Rev. E | Page 16 of 20

is sufficient gain to raise the amplitude of E

IN

to that required to

establish an output amplitude of E

C

over the range of 1 V to 10 V.

The X input of the AD734, which has finite offset voltage, can be

troublesome at the output at high gains. The output offset is

reduced to that of the X input (1 mV or 2 mV) by the offset

loop comprising R3, C3, and Buffer A1. The low-pass corner

frequency of 0.16 Hz is transformed to a high-pass corner that is

multiplied by the gain (for example, 160 Hz at a gain of 1000).

In applications not requiring operation down to low frequencies,

Amplifier A1 can be eliminated, but the AD734’s input resistance

of 50 kΩ between X1 and X2 reduces the time constant and

increases the input offset. Using a nonpolar 20 mF tantalum

capacitor for C1 results in the same unity-gain high-pass corner; in

this case, the offset gain increases to 20, which is still acceptable.

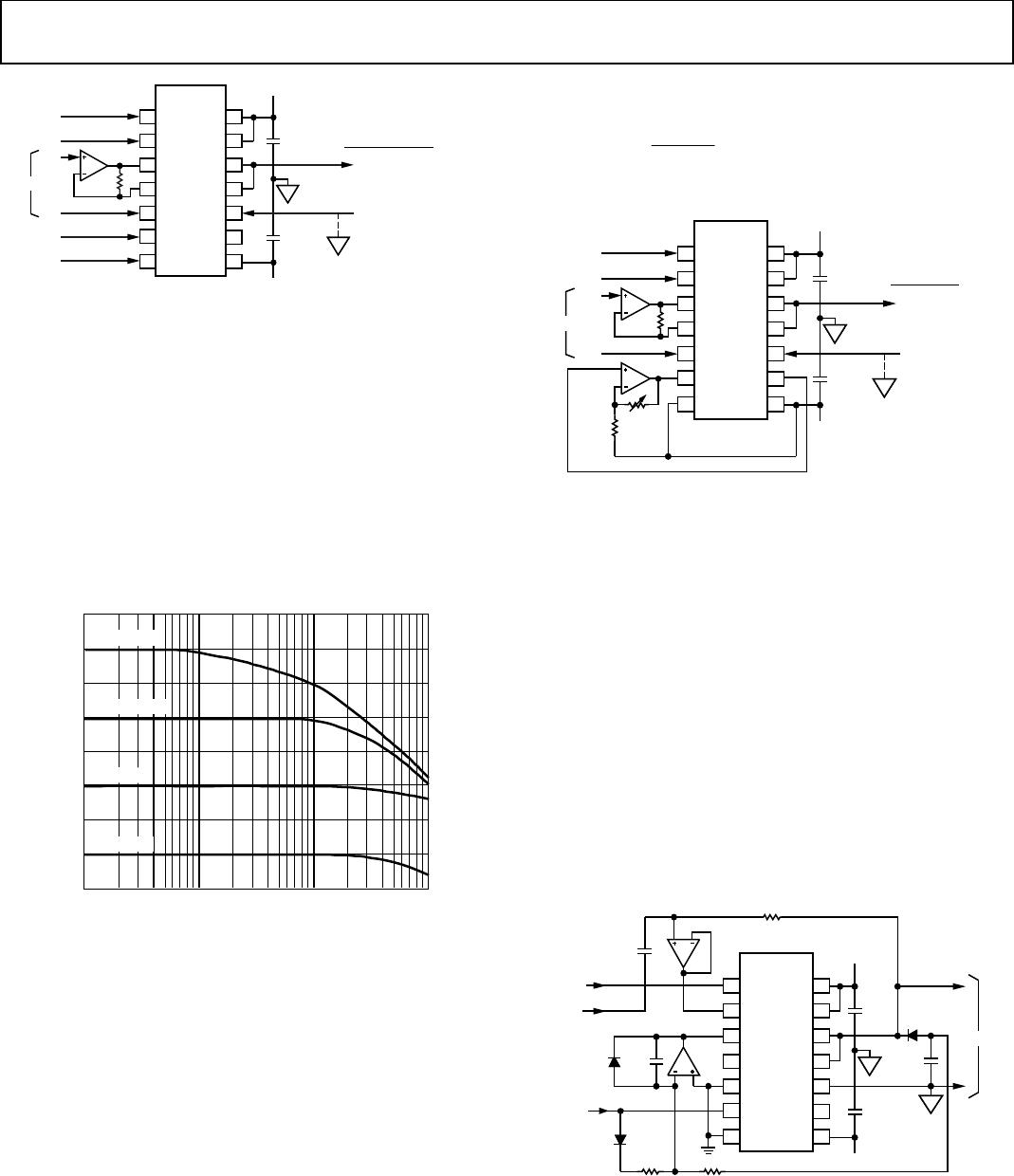

Figure 33 shows the error in the output for sinusoidal inputs at

100 Hz, 100 kHz, and 1 MHz, with E

C

set to 10 V. The output

error for any frequency between 300 Hz and 300 kHz is similar

to that for 100 kHz. At low signal frequencies and low input

amplitudes, the dynamics of the control loop determine the gain

error and distortion; at high frequencies, the 200 MHz gain-

bandwidth product of the AD734 limits the available gain.

The output amplitude tracks E

C

over the range of 1 V to slightly

more than 10 V.

INPUT AMPLITUDE (V)

ERROR (dB)

2

1

0

–1

–2

0.01 0.1 1 10

00827-016

100kHz

100Hz

1MHz

Figure 33. AGC Amplifier Output Error vs. Input Voltage

WIDEBAND RMS-TO-DC CONVERTER USING U

INTERFACE

The AD734 is well-suited to such applications as implicit rms-

to-dc conversion, where the AD734 implements the function

[]

RMS

IN

RMS

V

V

V

2

avg

= (13)

using its direct divide mode. Figure 34 shows the circuit.

AD734

X11

X22

U03

U14

U2

5

VP 14

DD 13

W 12

Z1 11

Z2

10

Y2

7

ER

9

VN

8

Y16

+15

U2b

1/2

AD708

1/2

AD708

–15V

0.1µF

0.1µF

00827-017

L

L

L

L

L

C1

47µF

C2

1µF

V

IN

R1

3.32kΩ

U2a

L

L

V

O

= V

IN

2

Figure 34. A Two-Chip, Wideband RMS-to-DC Converter

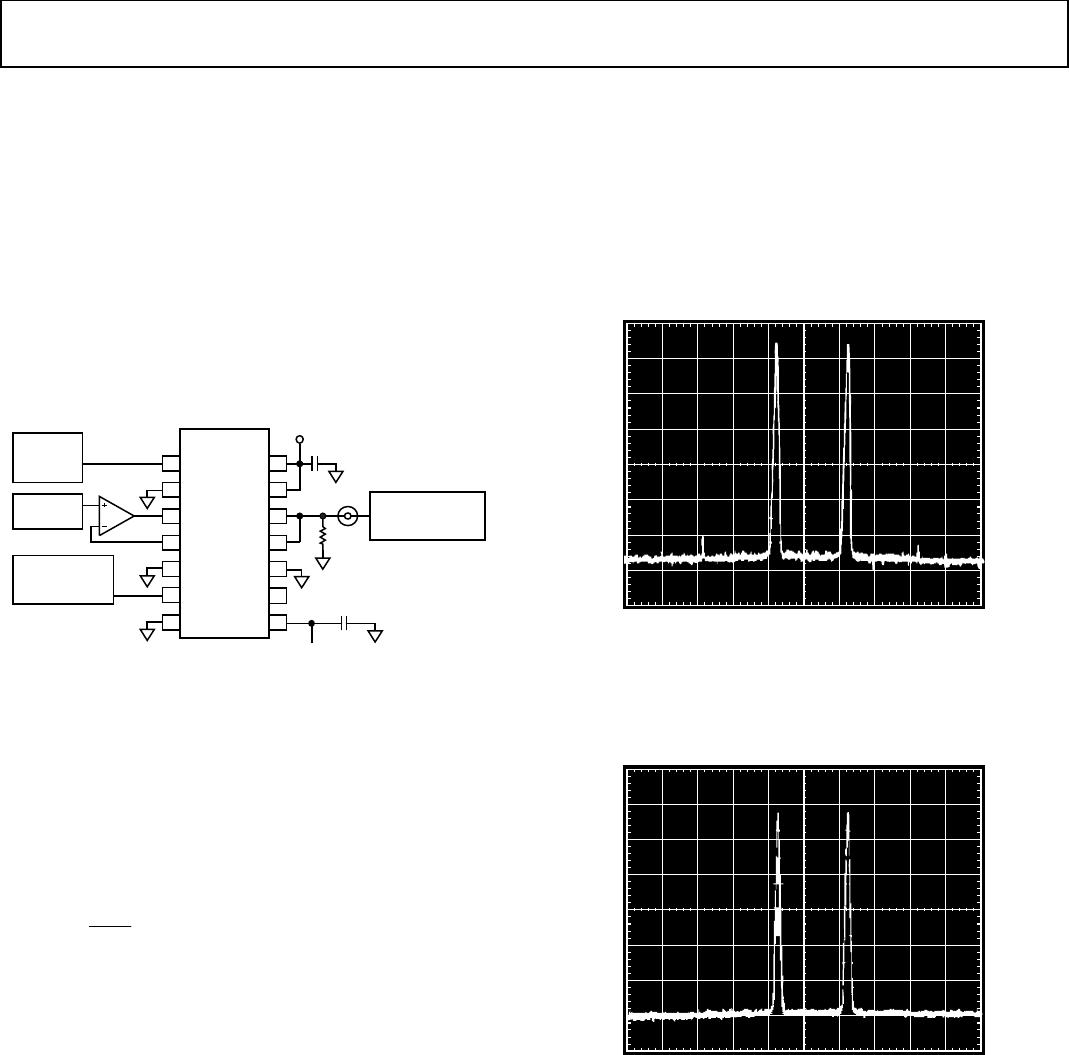

In this application, the AD734 and an AD708 dual op amp

serve as a two-chip rms-to-dc converter with a 10 MHz

bandwidth. Figure 35 shows the circuit’s performance for

square-, sine-, and triangle-wave inputs. The circuit accepts

signals as high as 10 V p-p with a crest factor of 1 or 1 V p-p

with a crest factor of 10. The circuit’s response is flat to 10 MHz

with an input of 10 V, flat to almost 5 MHz for an input of 1 V,

and to almost 1 MHz for inputs of 100 mV. For accurate

measurements of input levels below 100 mV, the AD734’s

output offset (Z interface) voltage, which contributes a dc error,

must be trimmed out.

In the circuit shown in Figure 34, the AD734 squares the input

signal, and its output (V

IN

2

) is averaged by a low-pass filter that

consists of R1 and C1 and has a corner frequency of 1 Hz. Because

of the implicit feedback loop, this value is both the output value,

V

RMS

, and the denominator in Equation 13. U2a and U2b, an

AD708 dual dc precision op amp, serve as unity-gain buffers,

supplying both the output voltage and driving the U interface.

INPUT FREQUENCY (Hz)

OUTPUT VOLTAGE (V)

100

10

1

100m

1m

10m

100µ

10k 100k 1M 10M

00827-018

SQUARE WAVE

SINE WAVE

TRI-WAVE

Figure 35. RMS-to-DC Converter Performance