5

5194F–SEEPR–1/08

AT24C1024B

Notes: 1. This parameter is ensured by characterization only.

2. AC measurement conditions:

R

L

(connects to V

CC

): 1.3 k: (2.5V, 5V), 10 k: (1.8V)

Input pulse voltages: 0.3 V

CC

to 0.7 V

CC

Input rise and fall times: d 50 ns

Input and output timing reference voltages: 0.5 V

CC

4. Device Operation

CLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external

device. Data on the SDA pin may change only during SCL low time periods (see Figure 4-4 on

page 7). Data changes during SCL high periods will indicate a start or stop condition as defined

below.

t

i

Noise Suppression Time

(1)

100 50 ns

t

AA

Clock Low to Data Out Valid 0.05 0.9 0.05 0.55 s

t

BUF

Time the bus must be free before a

new transmission can start

(1)

1.3 0.5 s

t

HD.STA

Start Hold Time 0.6 0.25 s

t

SU.STA

Start Set-up Time 0.6 0.25 s

t

HD.DAT

Data In Hold Time 0 0 s

t

SU.DAT

Data In Set-up Time 100 100 ns

t

R

Inputs Rise Time

(1)

0.3 0.3 s

t

F

Inputs Fall Time

(1)

300 100 ns

t

SU.STO

Stop Set-up Time 0.6 0.25 s

t

DH

Data Out Hold Time 50 50 ns

t

WR

Write Cycle Time 5 5 ms

Endurance

(1)

25°C, Page Mode, 3.3V 1,000,000

Write

Cycles

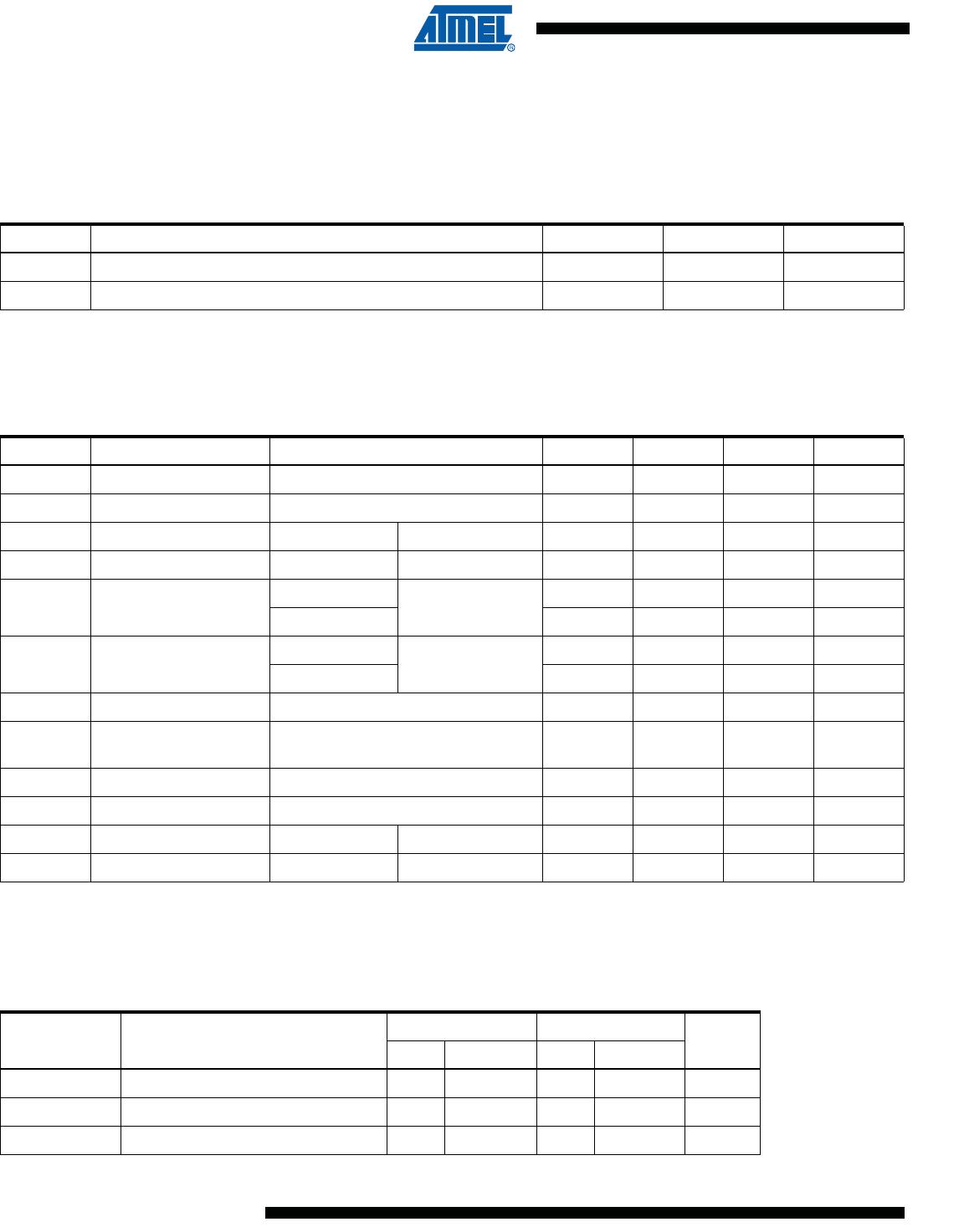

Table 3-3. AC Characteristics (Industrial Temperature)

Applicable over recommended operating range from T

AI

= 40qC to +85qC, V

CC

= +1.8V to +3.6V, CL = 100 pF (unless oth-

erwise noted). Test conditions are listed in Note 2.

Symbol Parameter

1.8-volt 2.5, 5.0-volt

UnitsMin Max Min Max