MAX8563/MAX8564/MAX8564A

Set R

D

= 100kΩ. The above equations also assume that

V

DD

> V

IN_

> 1V when V

IN_

is on or at a high-voltage

state, and that V

DD

> 3V.

Example: Connect 100kΩ from EN to V

DD

and 4kΩ from

EN_ to IN_. Thus, when V

DD

= 12V and V

IN

_ = 0V, then

V

EN

_ = 0.46V. When V

DD

= 12V and V

IN

_ = 1.2V, then

V

EN

_ = 1.6V.

Alternately, to avoid fault shutdown due to the delay of

V

IN

relative to V

DD

, pull EN_ low with a separate control

logic and only drive high when V

IN

reaches a steady-

state value.

Output Voltage

The output voltage range at the source of the n-MOSFET

is from 0.5V to 3.3V when V

DD

is 12V and from 0.5V to

1.8V when V

DD

is 5V. The maximum output voltage is a

function of the minimum gate-to-source voltage (V

GS

) of

the MOSFET and V

DD

.

The external n-MOSFET contains a parasitic diode from

source to drain. If the output is ever anticipated to

exceed the input, current flows from source to drain. If

this is undesirable, external protection is needed. A

simple solution is the placement of a diode in series,

from IN_ to the drain of the n-MOSFET, so that reverse

current is not possible. Due to the forward-voltage drop

of the diode, the maximum output voltage is reduced

and additional power is consumed in the diode.

Enable and POK

The MAX8563/MAX8564/MAX8564A have independent

enable control inputs (EN1, EN2, and EN3). Drive EN1

high to enable output 1. Drive EN2 high to enable out-

put 2. Drive EN3 high to enable output 3. When EN_ is

driven low, the corresponding DRV_ is internally pulled

to GND and POK_ is internally pulled low.

The POK_ is an open-drain output that provides the sta-

tus of the output voltage and pulls low depending upon

circuit conditions. During startup, once the FB_ reaches

the POK_ threshold, the POK_ signal goes high. The

POK_ threshold has 30mV of hysteresis. When the out-

put voltage drops 12% below the nominal regulated

voltage, POK_ pulls low. All POK_ outputs pull low

when UVLO is activated or when the internal VL regula-

tor and reference are not ready.

Output Undervoltage and

Overload Protection

When an overload event or short circuit occurs, the

device that is most vulnerable is the external n-MOSFET.

The MAX8563/MAX8564/MAX8564A monitor the output

voltage to protect the MOSFET. When DRV_ is at its maxi-

mum voltage and the output voltage drops below 80%

but is still greater than 60% of its nominal voltage for

more than 50µs, the MAX8563/MAX8564/MAX8564A

shut down that particular regulator output by pulling

DRV_ to GND. Note that there is an additional inherent

delay in turning off the MOSFET. The delay is a function

of the compensation capacitor and the MOSFET. If the

output recovers to greater than 80% within 50µs, it is not

considered to be in overload and no action is taken.

When the output voltage drops below 60% of its nominal

voltage, the MAX8563/MAX8564/MAX8564A immediately

shut down that particular regulator output by pulling

DRV_ to GND. To restart that particular LDO, V

DD

must

be recycled below the UVLO or the corresponding EN_

must be recycled. The overload protection is shown in

the Typical Operating Characteristics.

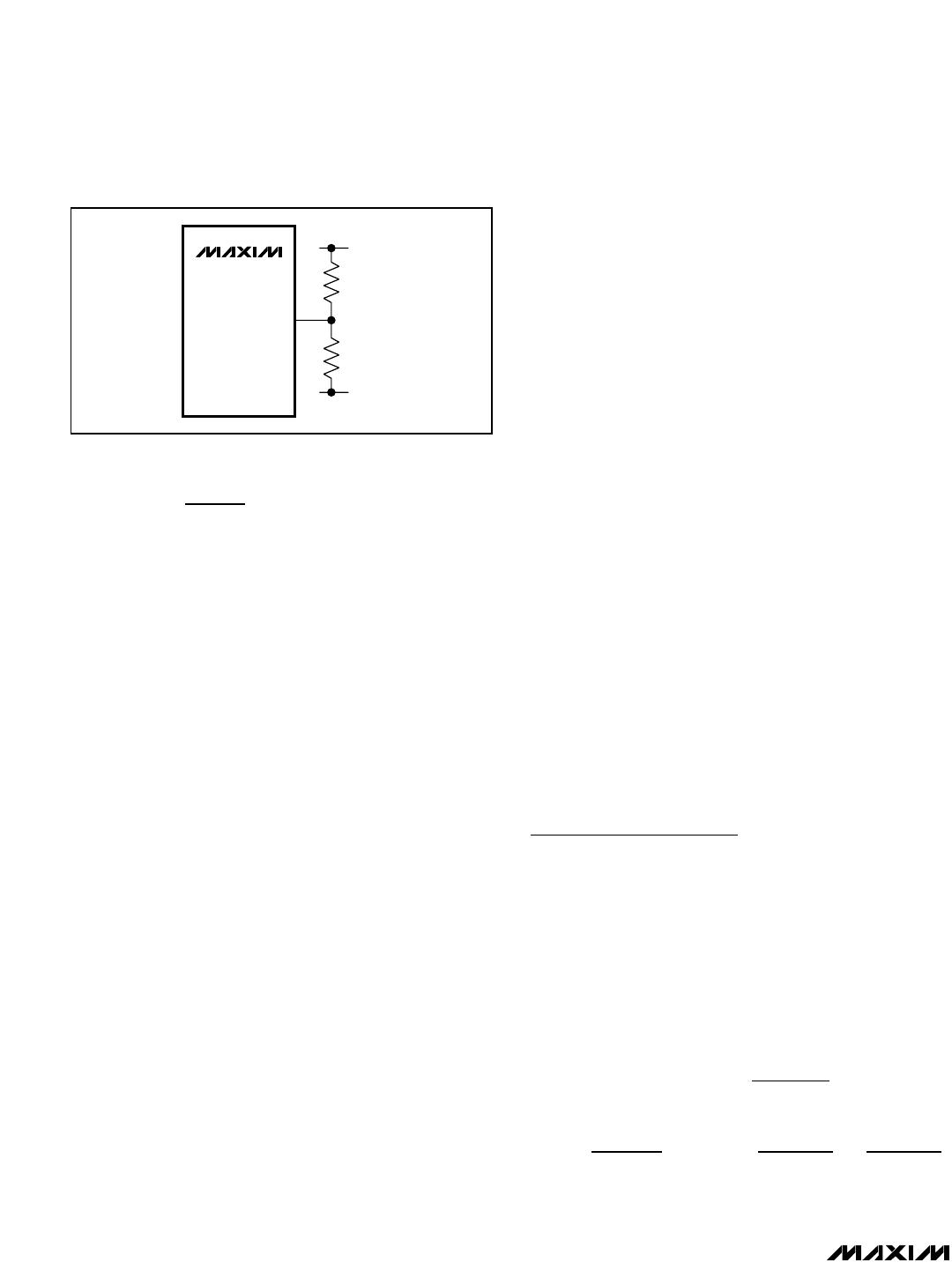

Design Procedure

Output Voltage Setting

The minimum output voltage for each controller of the

MAX8563/MAX8564/MAX8564A is typically 0.5V. The

maximum output voltage is adjustable up to 3.3V with

V

DD

= 12V, and up to 1.8V with V

DD

= 5V. To set the out-

put voltage, connect the FB_ pin to the center of a volt-

age-divider between OUT_ and GND (Figure 5). The

resistor-divider current should be at least 1mA per 1A of

maximum output current; i.e., for a 3A maximum output

current, set the resistor-divider bias current to ≥ 3mA: