LTC2482

11

2482fc

APPLICATIONS INFORMATION

by two orders of magnitude. The part remains in the sleep

state as long as CS is high. The conversion result is held

indefi nitely in a static shift register while the converter is

in the sleep state.

Once CS is pulled low, the device exits the low power mode

and enters the data output state. If CS is pulled high before

the fi rst rising edge of SCK, the device returns to the low

power sleep mode and the conversion result is still held

in the internal static shift register. If CS remains low after

the fi rst rising edge of SCK, the device begins outputting

the conversion result. Taking CS high at this point will

terminate the data output state and start a new conversion.

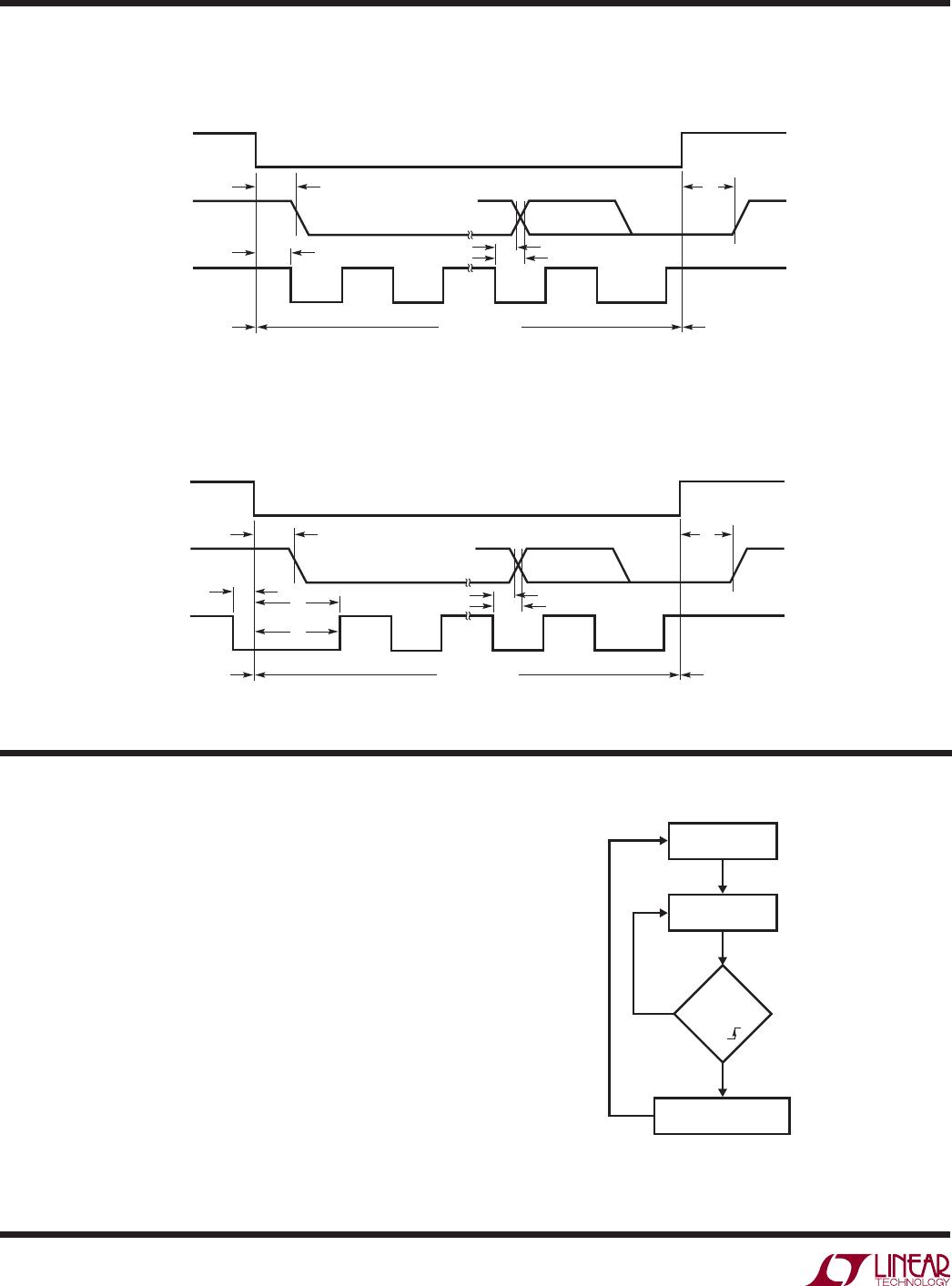

The conversion result is shifted out of the device through

the serial data output pin (SDO) on the falling edge of the

serial clock (SCK) (see Figure 2).

Through timing control of the CS and SCK pins, the LTC2482

offers several fl exible modes of operation (internal or

external SCK and free-running conversion modes). These

various modes do not require programming confi guration

registers; moreover, they do not disturb the cyclic operation

described above. These modes of operation are described

in detail in the Serial Interface Timing Modes section.

Easy Drive Input Current Cancellation

The LTC2482 combines a high precision delta-sigma ADC

with an automatic differential input current cancellation

front end. A proprietary front-end passive sampling net-

work transparently removes the differential input current.

This enables external RC networks and high impedance

sensors to directly interface to the LTC2482 without

external amplifi ers. The remaining common mode input

current is eliminated by either balancing the differential

input impedances or setting the common mode input

equal to the common mode reference (see Automatic Input

Current Cancellation section). This unique architecture

does not require on-chip buffers enabling input signals to

swing all the way to ground and up to V

CC

. Furthermore,

the cancellation does not interfere with the transparent

offset and full-scale autocalibration and the absolute ac-

curacy (full scale + offset + linearity) is maintained with

external RC networks.

Output Data Format

The LTC2482 serial output data stream is 24 bits long. The

fi rst 3 bits represent status information indicating the sign

and conversion state. The next 17 bits are the conversion

result, MSB fi rst. The remaining 4 bits are always zero.

Bit 21 and Bit 20 together are also used to indicate an

underrange condition (the differential input voltage is

below –FS) or an overrange condition (the differential

input voltage is above +FS).

In applications where a processor generates 32 clock

cycles, or to remain compatible with higher resolution

converters, the LTC2482’s digital interface will ignore

extra clock edges seen during the next conversion period

after the 24th and output “1” for the extra clock cycles.

Furthermore, CS may be pulled high prior to outputting

all 24 bits, aborting the data out transfer and initiating a

new conversion.

CS

SDO

Hi-Z

SIG

BIT 21 BIT 20 BIT 19 BIT 18 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0BIT 22BIT 23

DMY MSB B16

CONVERSION RESULT

LSB

SCK

SLEEP DATA OUTPUT

EOC

CONVERSION

2482 F02

Figure 2. Output Data Timing