General Description

DDR2 SDRAM modules are high-speed, CMOS dynamic random access memory mod-

ules that use internally configured 4 or 8-bank DDR2 SDRAM devices. DDR2 SDRAM

modules use DDR architecture to achieve high-speed operation. DDR2 architecture is

essentially a 4n-prefetch architecture with an interface designed to transfer two data

words per clock cycle at the I/O pins. A single read or write access for the DDR2 SDRAM

module effectively consists of a single 4n-bit-wide, one-clock-cycle data transfer at the

internal DRAM core and eight corresponding n-bit-wide, one-half-clock-cycle data

transfers at the I/O pins.

DDR2 modules use two sets of differential signals: DQS, DQS# to capture data and CK

and CK# to capture commands, addresses, and control signals. Differential clocks and

data strobes ensure exceptional noise immunity for these signals and provide precise

crossing points to capture input signals. A bidirectional data strobe (DQS, DQS#) is

transmitted externally, along with data, for use in data capture at the receiver. DQS is a

strobe transmitted by the DDR2 SDRAM device during READs and by the memory con-

troller during WRITEs. DQS is edge-aligned with data for READs and center-aligned

with data for WRITEs.

DDR2 SDRAM modules operate from a differential clock (CK and CK#); the crossing of

CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Com-

mands (address and control signals) are registered at every positive edge of CK. Input

data is registered on both edges of DQS, and output data is referenced to both edges of

DQS, as well as to both edges of CK.

Serial Presence-Detect EEPROM Operation

DDR2 SDRAM modules incorporate serial presence-detect. The SPD data is stored in a

256-byte EEPROM. The first 128 bytes are programmed by Micron to identify the mod-

ule type and various SDRAM organizations and timing parameters. The remaining 128

bytes of storage are available for use by the customer. System READ/WRITE operations

between the master (system logic) and the slave EEPROM device occur via a standard

I

2

C bus using the DIMM’s SCL (clock) SDA (data), and SA (address) pins. Write protect

(WP) is connected to V

SS

, permanently disabling hardware write protection.

Register and PLL Operation

DDR2 SDRAM modules operate in registered mode, where the command/address input

signals are latched in the registers on the rising clock edge and sent to the DDR2

SDRAM devices on the following rising clock edge (data access is delayed by one clock

cycle). A phase-lock loop (PLL) on the module receives and redrives the differential

clock signals (CK, CK#) to the DDR2 SDRAM devices. The registers and PLL minimize

system and clock loading. PLL clock timing is defined by JEDEC specifications and en-

sured by use of the JEDEC clock reference board. Registered mode will add one clock

cycle to CL.

Parity Operations

The registering clock driver can accept a parity bit from the system’s memory control-

ler, providing even parity for the control, command, and address bus. Parity errors are

flagged on the Err_Out# pin. Systems not using parity are expected to function without

issue if Par_In and Err_Out# are left as no connects (NC) to the system.

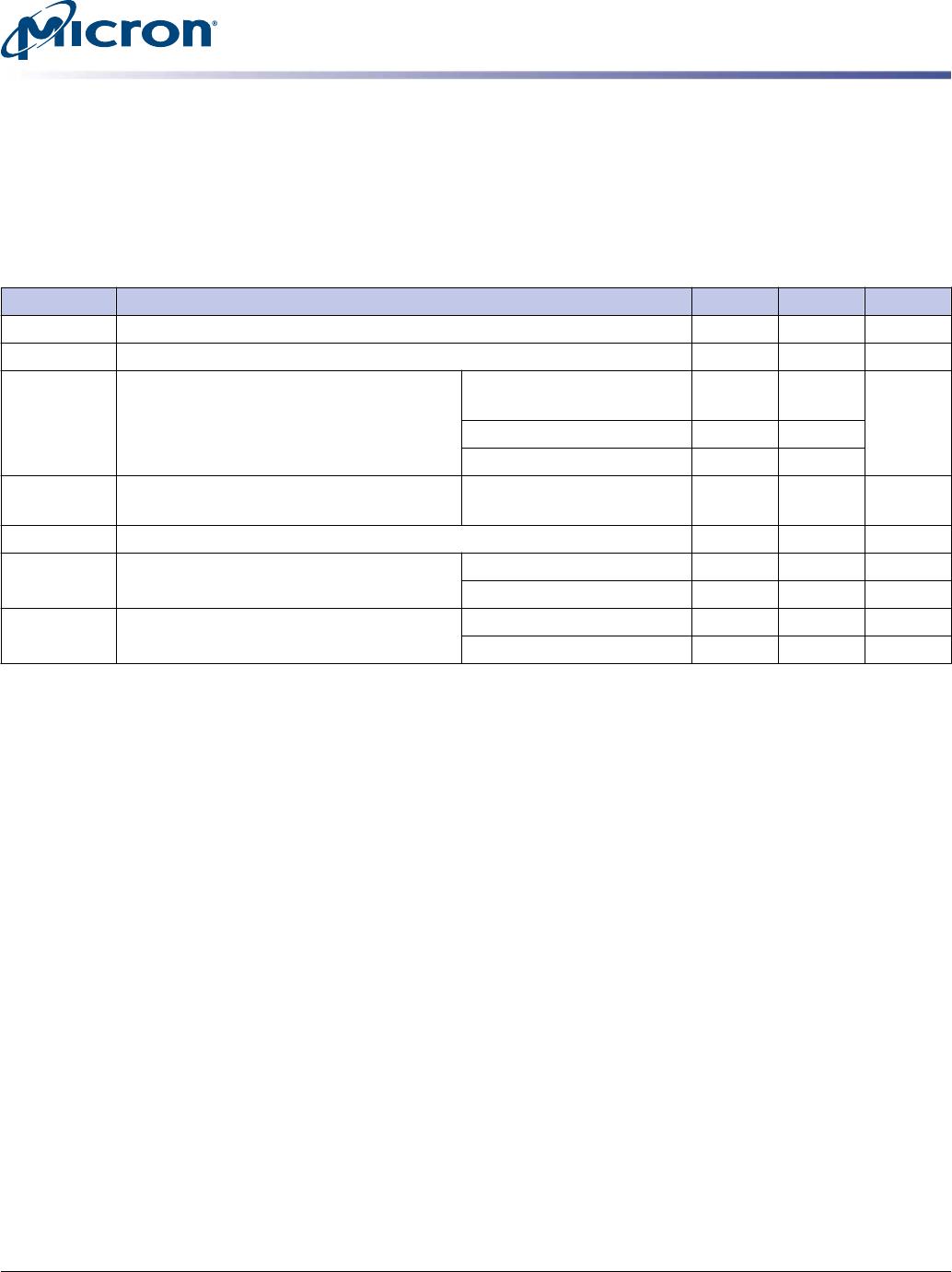

2GB, 4GB (x72, ECC, DR) 244-Pin DDR2 VLP Mini-RDIMM

General Description

PDF: 09005aef83d94997

hvs18c256_512x72pkz.pdf - Rev. E 4/14 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.