LTC3630

19

3630fd

For more information www.linear.com/LTC3630

applicaTions inForMaTion

The value of C

IN

is selected to keep the input from droop-

ing less than 240mV (1%):

C

IN

>

10µH • 1.2A

≅ 2.2µF

C

OUT

will be selected based on a value large enough to

satisfy the output voltage ripple requirement. For a 50mV

output ripple, the value of the output capacitor can be

calculated from:

C

OUT

>

10µH • 1.2A

2

≅ 47µF

C

OUT

also needs an ESR that will satisfy the output voltage

ripple requirement. The required ESR can be calculated

from:

ESR <

≅ 40mΩ

A 47µF ceramic capacitor has significantly less ESR than

40mΩ.

Since an output voltage of 3.3V is one of the standard

output configurations, the LTC3630 can be configured

by connecting V

PRG1

to ground and V

PRG2

to the SS pin.

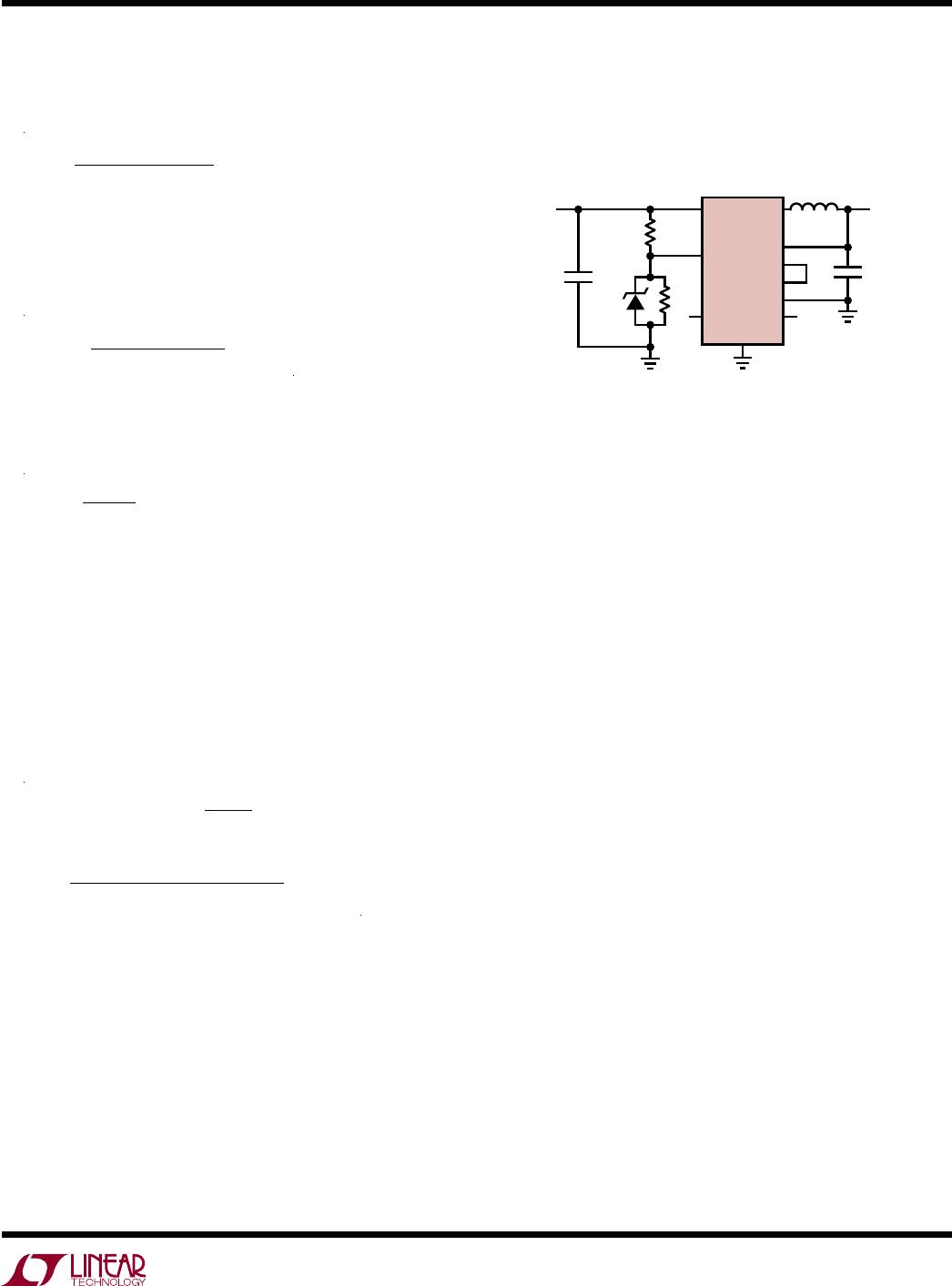

The undervoltage lockout requirement on V

IN

can be satis-

fied with a resistive divider from V

IN

to the RUN pin (refer

to Figure 9). Calculate R3 and R4 as follows:

R3 = 200k whichis ≤

40µA

R4 =

200k • 1.21V

12V – 1.21V + 200k • 4µA

= 20.9k

Choose standard values for R3 = 200k, R4 = 21k. Note

that the V

IN

falling threshold will be 10% less than the

rising threshold or 11V.

Since the maximum V

IN

is more than 4.5x the UVLO thresh-

old, a 4.7V Zener diode in parallel with R4 is required to

keep the maximum voltage on the RUN pin less than the

absolute maximum of 6V.

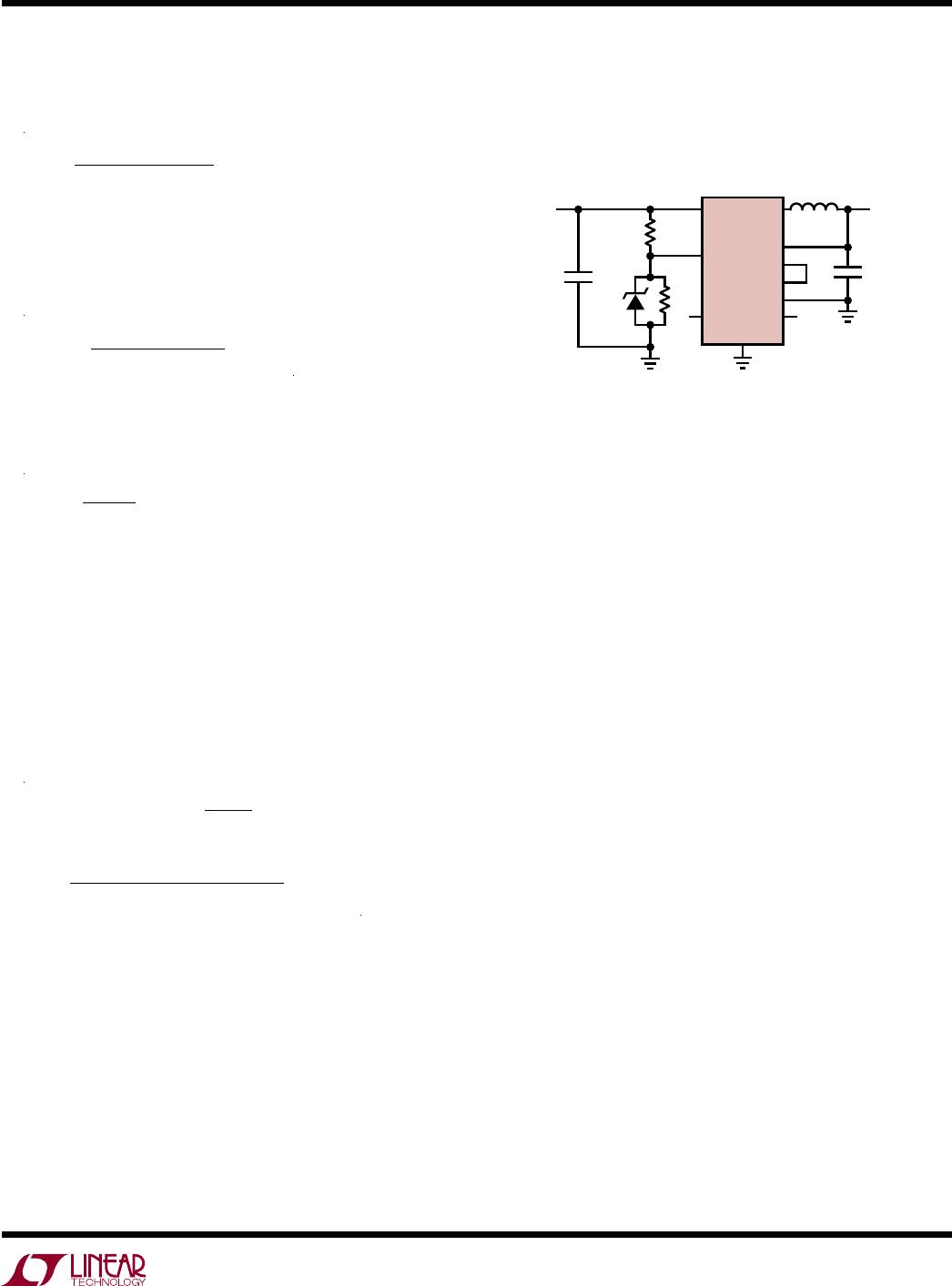

V

FB

SW

V

IN

RUN

200k

2.2µF

47µF

OUT

3.3V

V

IN

21k

4.7V

3630 F11

SS

V

PRG2

V

PRG1

FBO

I

SET

GND

LTC3630

Figure 11. 24V to 3.3V, 500mA Regulator at 200kHz

The I

SET

pin should be left open in this example to select

maximum peak current (1.2A typical). Figure 11 shows a

complete schematic for this design example.

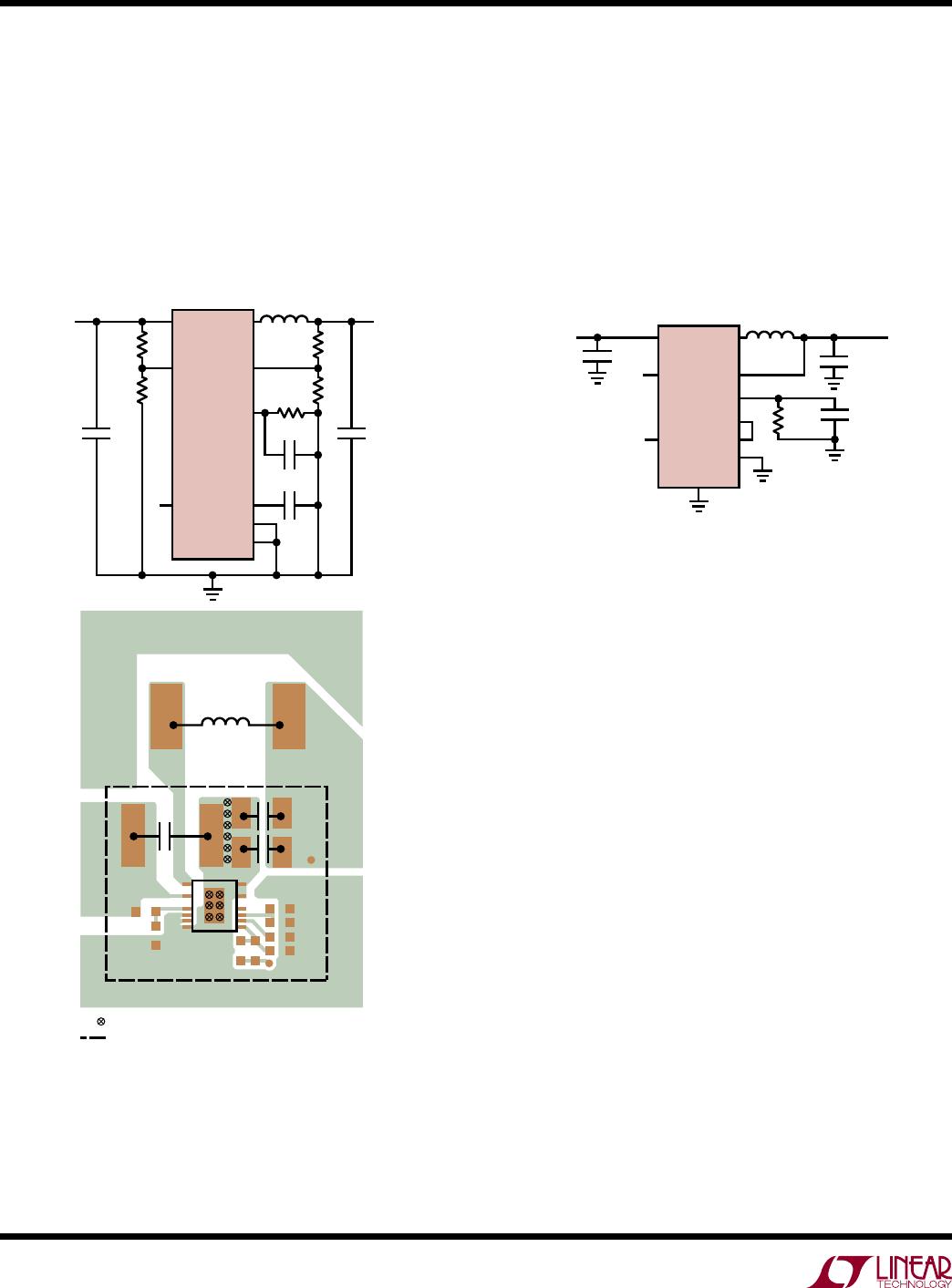

PC Board Layout Checklist

When laying out the printed circuit board, the following

checklist should be used to ensure proper operation of

the LTC3630. Check the following in your layout:

1. Large switched currents flow in the power switches

and input capacitor. The loop formed by these compo

-

nents should be as small as possible. A ground plane

is recommended to minimize ground impedance.

2.

Connect the (+) terminal of the input capacitor, C

IN

, as

close as possible to the V

IN

pin. This capacitor provides

the AC current into the internal power MOSFETs.

3. Keep the switching node, SW, away from all sensitive

small signal nodes. The rapid transitions on the switching

node can couple to high impedance nodes, in particular

V

FB

, and create increased output ripple.

4. Flood all unused area on all layers with copper except

for the area under the inductor. Flooding with copper

will reduce the temperature rise of power components.

You can connect the copper areas to any DC net (V

IN

,

V

OUT

, GND, or any other DC rail in your system).