Temperature Sensor with SPD EEPROM Operation

Thermal Sensor Operations

The integrated thermal sensor continuously monitors the temperature of the module

PCB directly below the device and updates the temperature data register. Temperature

data may be read from the bus host at any time, which provides the host real-time feed-

back of the module's temperature. Multiple programmable and read-only temperature

registers can be used to create a custom temperature-sensing solution based on system

requirements and JEDEC JC-42.2.

EVENT_n Pin

The temperature sensor also adds the EVENT_n pin (open-drain), which requires a pull-

up to V

DDSPD

. EVENT_n is a temperature sensor output used to flag critical events that

can be set up in the sensor’s configuration registers. EVENT_n is not used by the serial

presence-detect (SPD) EEPROM.

EVENT_n has three defined modes of operation: interrupt, comparator, and TCRIT. In

interrupt mode, the EVENT_n pin remains asserted until it is released by writing a 1 to

the clear event bit in the status register. In comparator mode, the EVENT_n pin clears

itself when the error condition is removed. Comparator mode is always used when the

temperature is compared against the TCRIT limit. In TCRIT only mode, the EVENT_n

pin is only asserted if the measured temperature exceeds the TCRIT limit; it then re-

mains asserted until the temperature drops below the TCRIT limit minus the TCRIT

hysteresis.

SPD EEPROM Operation

DDR4 SDRAM modules incorporate SPD. The SPD data is stored in a 512-byte, JEDEC

JC-42.4-compliant EEPROM that is segregated into four 128-byte, write-protectable

blocks. The SPD content is aligned with these blocks as shown in the table below.

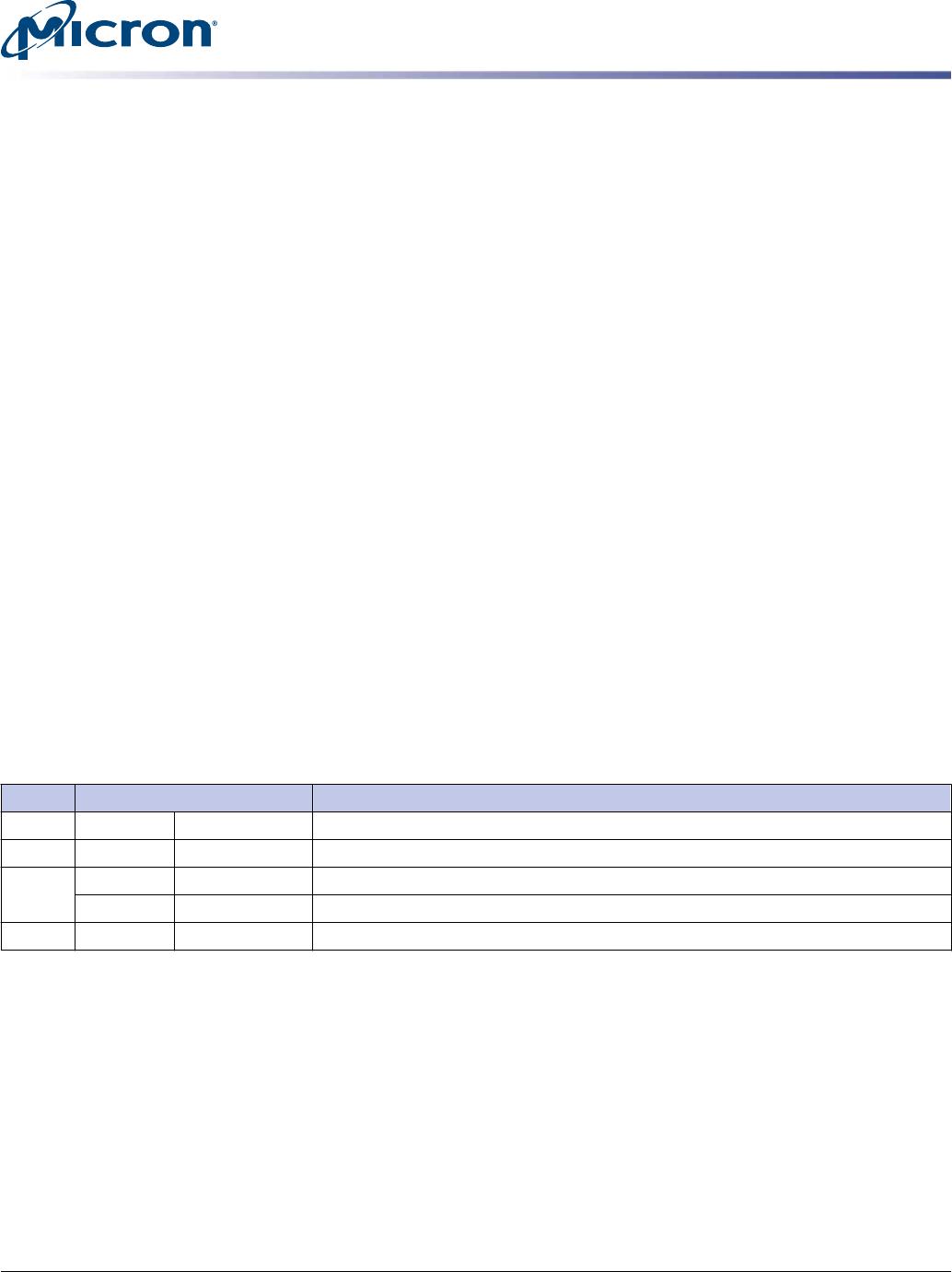

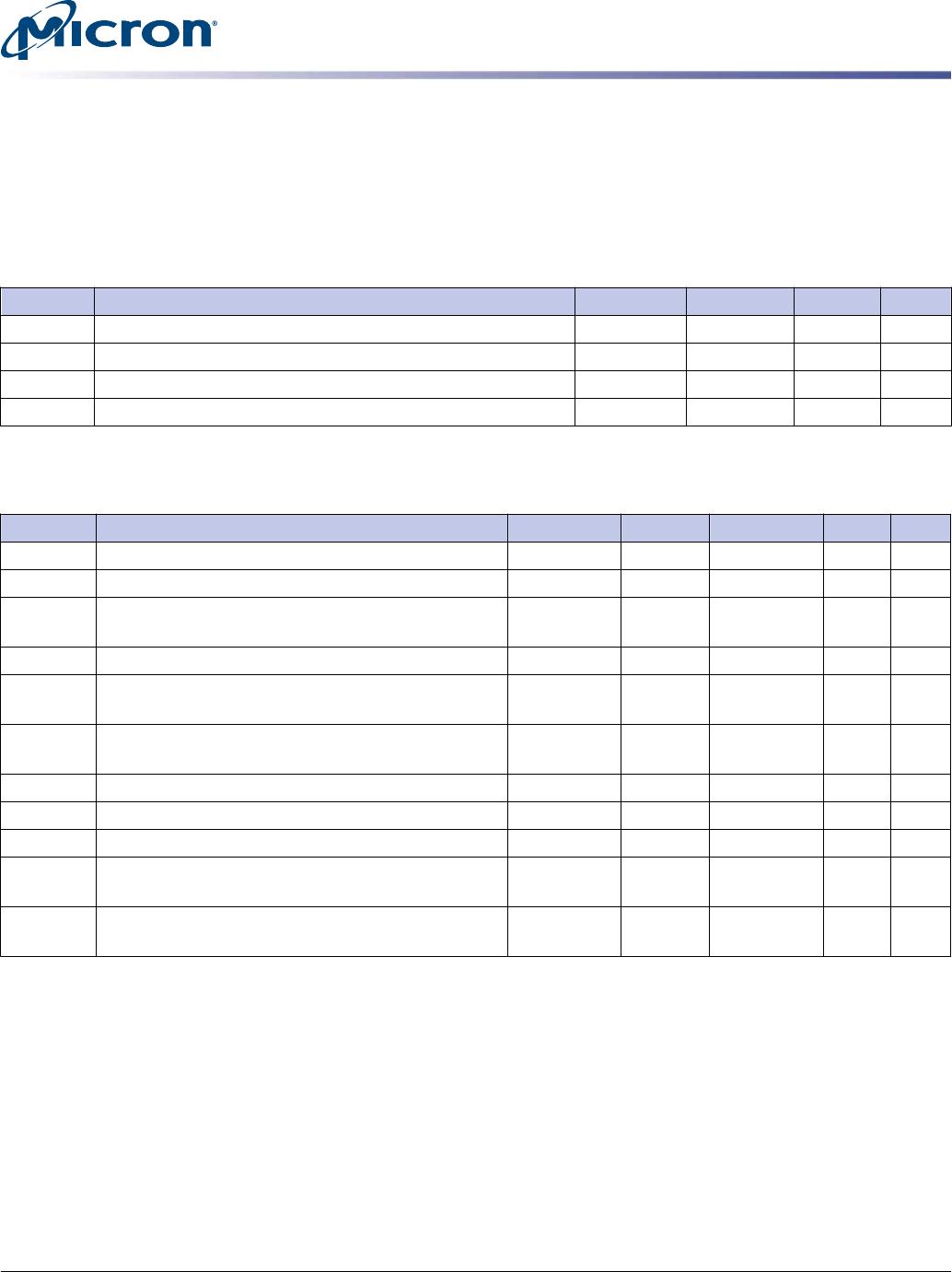

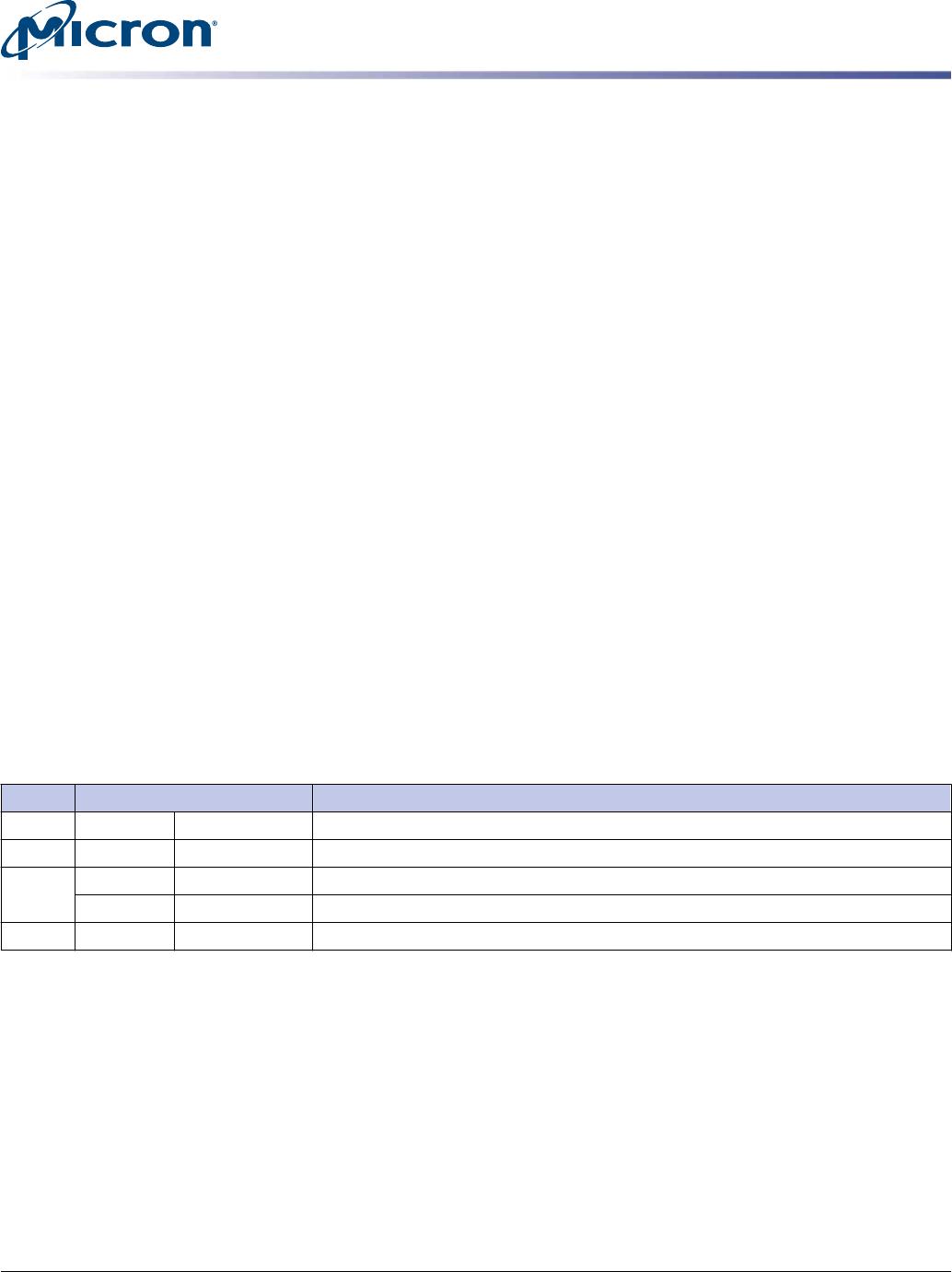

Block Range Description

0 0–127 000h–07Fh Configuration and DRAM parameters

1 128–255 080h–0FFh Module parameters

2 256–319 100h–13Fh Reserved (all bytes coded as 00h)

320–383 140h–17Fh Manufacturing information

3 384–511 180h–1FFh End-user programmable

The first 384 bytes are programmed by Micron to comply with JEDEC standard JC-45,

"Appendix X: Serial Presence Detect (SPD) for DDR4 SDRAM Modules." The remaining

128 bytes of storage are available for use by the customer.

The EEPROM resides on a two-wire I

2

C serial interface and is not integrated with the

memory bus in any manner. It operates as a slave device in the I

2

C bus protocol, with all

operations synchronized by the serial clock. Transfer rates of up to 1 MHz are achieva-

ble at 2.5V (NOM).

Micron implements reversible software write protection on DDR4 SDRAM-based mod-

ules. This prevents the lower 384 bytes (bytes 0 to 383) from being inadvertently pro-

grammed or corrupted. The upper 128 bytes remain available for customer use and are

unprotected.

16GB (x72, ECC, DR) 288-Pin DDR4 RDIMM

Temperature Sensor with SPD EEPROM Operation

09005aef862e760f

asf18c2gx72pdz.pdf - Rev. D 8/16 EN

11

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.