General Description

High-speed DDR4 SDRAM modules use DDR4 SDRAM devices with two or four internal

memory bank groups. DDR4 SDRAM modules utilizing 4- and 8-bit-wide DDR4 SDRAM

devices have four internal bank groups consisting of four memory banks each, provid-

ing a total of 16 banks. 16-bit-wide DDR4 SDRAM devices have two internal bank

groups consisting of four memory banks each, providing a total of eight banks. DDR4

SDRAM modules benefit from DDR4 SDRAM's use of an 8n-prefetch architecture with

an interface designed to transfer two data words per clock cycle at the I/O pins. A single

READ or WRITE operation for the DDR4 SDRAM effectively consists of a single 8n-bit-

wide, four-clock data transfer at the internal DRAM core and eight corresponding n-bit-

wide, one-half-clock-cycle data transfers at the I/O pins.

DDR4 modules use two sets of differential signals: DQS_t and DQS_c to capture data

and CK_t and CK_c to capture commands, addresses, and control signals. Differential

clocks and data strobes ensure exceptional noise immunity for these signals and pro-

vide precise crossing points to capture input signals.

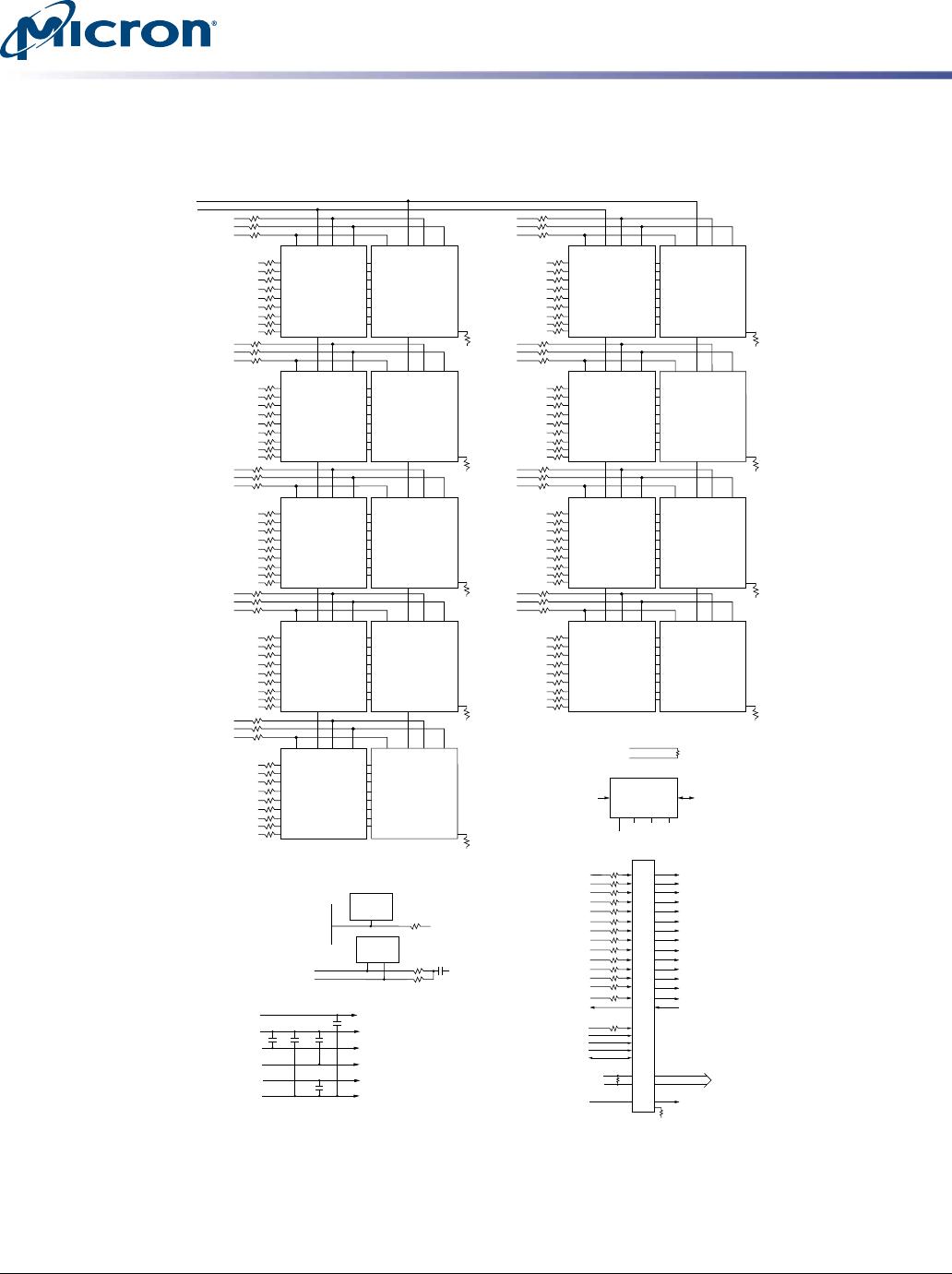

Fly-By Topology

DDR4 modules use faster clock speeds than earlier DDR technologies, making signal

quality more important than ever. For improved signal quality, the clock, control, com-

mand, and address buses have been routed in a fly-by topology, where each clock, con-

trol, command, and address pin on each DRAM is connected to a single trace and ter-

minated (rather than a tree structure, where the termination is off the module near the

connector). Inherent to fly-by topology, the timing skew between the clock and DQS sig-

nals can be easily accounted for by using the write-leveling feature of DDR4.

Module Manufacturing Location

Micron Technology manufactures modules at sites world-wide. Customers may receive

modules from any of the following manufacturing locations:

Table 6: DRAM Module Manufacturing Locations

Manufacturing Site Location Country of Origin Specified on Label

Boise, USA USA

Aguadilla, Puerto Rico Puerto Rico

Xian, China China

Singapore Singapore

16GB (x72, ECC, DR) 288-Pin DDR4 RDIMM

General Description

09005aef862e760f

asf18c2gx72pdz.pdf - Rev. D 8/16 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.